电路图是设计PCB的基础,绘电路图要注意布局合理、排列均匀、图面清晰。PADS Logic可以在电路图中插入OLE对象,如Word、Excel文档及画图文件等。选择Edit>Insert New Object命令,打开“插入对象”对话框即可操作。

Logic自动分配元件的参考编号(Reference Designator)。一个元件内的门没有用完之前,不能新建另一个同类型元件的标号。删除了元件门或重新编号后留下的空位编号将被自动填充。Logic的网络标号是定义在连线上的,即在两个引脚间没有连线就不能建立网络。所以在放置元件时必须留下适当间隔,不可直接以元件引脚相接。

选择主工具栏上的设计按钮,打开设计工具盒,如图1所示。

其功能是:添加元件、添加连线、编辑元件/层次符号、新建层次符号、交换元件标号和交换元件引脚。

首先要确定元件库已被调入,可用库管理器查看。由于PADS自带的元件库较少,可选(All Libraries),将元件库全部调入。

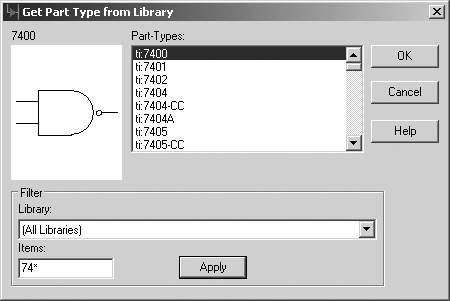

选择添加元件按钮,弹出Add Part对话框。可直接输入元件名或点击Browse按钮,弹出Get Part Type from Library(从库中获取元件)对话框,如.所示。

在Library对话框中选择元件库,Items为元件过滤栏。如寻找74系列元件,在此栏中输入74*后按Apply,就可在Part-Types的列表中找出所需的元件类型,如7401。

确定后,7401的CAE符号随光标出现。可对CAE符号进行编辑,方法见上期相关文章。移动光标到合适的位置,单击鼠标放置一个元件。可连续放置元件,按ESC键放弃。此元件被自动命名为U1-A。7401中有4个CAE符号,连续放置的7401会被命名为U1-A~D。第5个7401被命名为U2-A。

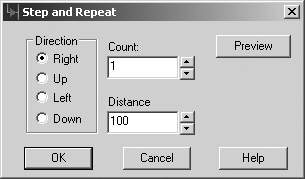

放下第1个元件后,弹出菜单中的Step and Repeat(步进和重复)命令激活,可成排地粘贴元件。选择此命令后弹出图3所示对话框。

Direction是重复放置的方向,Count是放置元件的数量,Distance是元件的间距,按Preview可预览放置的效果。

放置元件后,可进行必要的调整。

Logic中对元件的一套编辑操作称为动词模式(Verb Model)。分复制模式、移动模式、删除模式和查询模式。

Logic可对调电路图中元件的标号和引脚。选中元件,点击交换元件标号按钮66,再点击另一同类的元件,这两个元件的标号即被对调。按同样的方法,用交换引脚按钮67对调同一门电路的同类型引脚。交换引脚时系统会提示是否保持原有连线,应根据具体情况确定。

③修改元件属性

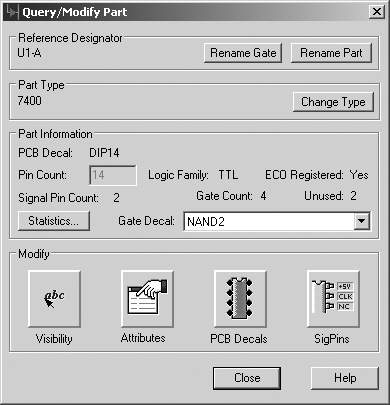

元件放置后才能修改其属性。选中一个对象,再选择查询/修改按钮 ,弹出属性对话框,见图4。

在Reference Designator区重命名元件编号;Part Type更改元件类型;在Part Information区显示元件的PCB封装、引脚数、逻辑类型、信号引脚数、封装中的逻辑门数等; 按Statistics按钮产生引脚统计文本; 在Gate Decal下拉列表中更改元件的CAE符号样式。

在Modify区中,各按钮的功能为:Visibility设置元件参数字符显示;Attributes设置元件属性描述;SigPins设置元件电源的接地引脚参数;PCB Decals设置元件PCB封装,其对话框如图5所示。

图5中,Assigned in栏是当前的PCB封装,Alternates in是可用的封装,按Browse从元件库中搜寻封装。在Apply update to栏中有两个选项:This Part是将选定的封装用于本元件,All Parts This Type将选定的封装用于所有此类型的元件。

2.添加连线和总线

连线和总线具有电气意义。每个连线都有惟一的网络标号,自动生成的网络标号形如“$$$08315”。每个总线都有一组网络标号。在绘图时应尽量减少各种连线的交叉和折弯。

(1)连线

选择连线按钮68,光标处于连线状态。连线必须从引脚开始,到引脚或其他电气符号结束。左击产生连线转角,按退格键取消转角。在连线状态时,右击打开快捷菜单,如图6所示。Angle改变连线走线角度,只有任意角度和直角两种模式。

(2)电源和接地符号

图6菜单中,Ground为加接地符号于连线(有3种样式),Power是电源符号(有4种样式)。调出符号后,按组合键Ctrl+Tab循环改变符号样式。操作系统为中文输入状态时,组合键无效。

(3)总线

应用总线可使电路图比较整洁,易于阅读。总线通过网络标号建立电路连接。在主工具栏中选择总线按钮,打开总线工具盒,如图7所示。

这些按钮的功能为:添加总线、改变总线局部形状、延伸总线端点、平移一段总线、删除总线。

可以在图纸的任意位置开始画总线,在需要转角处单击,双击完成绘制。

结束绘制总线,系统弹出Add Bus对话框,如图8所示。

在Bus Name栏中添加总线名,可从下拉列表中选取已有的总线名;Rename区是重命名总线名,修改总线属性时有效; Bus Type栏选择总线类型,有两种格式:数字Bit Format和混合网络Mixed Net。数字网络名的格式是XXXX[NN:NN]。X为字母或数字,N为数字。混合网络名在下面的Bus区域定义。

用连线符号添加总线分支线。从元件脚引向总线,在弹出的对话框中为分支线定义网络名。分支线的网络名应在总线网络名的范畴内。用复制或“步进和重复”命令可快速建立分支线。

(4)页面连接符号

页面连接符号可建立同一文件中各电路图纸间的连接。画连线时在快捷菜单中选Off-page命令,产生页面连接符号,按组合键Ctrl+Tab改变符号形状。确定后弹出Add Net Name对话框,输入网络名。

3.层次电路

PADS Logic支持从顶向下和从底向上的电路设计。对电路图纸定义层次符号,可使之成为另一张电路图纸的下级图纸。最高级的图纸为0级,包含了它和其下级全部设计内容。一个电路文件最多不能超过1024级层次和图纸数。

(1)新建层次电路符号

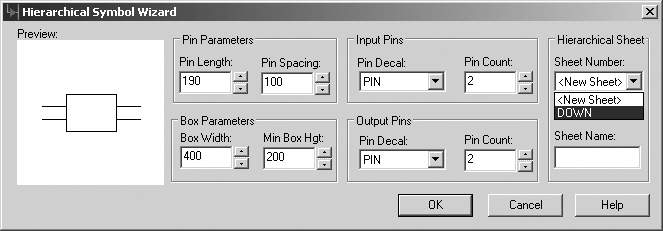

选择设计工具盒中的New Hierarchical Symbol按钮 ,打开层次符号对话框,见图9。

在Pin Parameters区定义引脚的长度和间距;Box Parameters区定义图纸符号的边长; Input/Output Pin区定义输入/输出引脚的类型和数量;在Sheet Number区指定符号所对应的图纸。如果没有现成的图纸,在Sheet Name区键入图纸名后,系统将新建一页图纸。确定后,一个层次电路符号将出现在原电路图中。

(2)建立层次电路

现制作一个只有2个层次的电路。在新文件中选择Setup>Sheet命令,打开图纸管理对话框,在对话框中选择Add按钮,添加一页新的图纸。再用Rename按钮将Sheet 1改名为UP,Sheet 2改名为DOWN。

在图纸UP中绘制电路,将电路复制后粘贴到图纸DOWN中, 提示信息报告已将元件U1的标号改为U2。回到UP图纸中,选择层次符号按钮,在图9的Sheet Number下拉列表中选DOWN,确定。系统进入层次符号编辑器中,可更改引脚类型,名称等符号属性。两张图纸的连接网络名已定义,不必更改。选菜单命令File>Complete退出。

回到电路图编辑器中,将层次电路符号放在合适的位置。现在图纸下拉列表变成如图10所示的形态,反映了图纸的层次关系。

也可用菜单命令View>Push/Pop Hierarchy显示下层/上层图纸。

文/甘雨