在早期的集成电路彩电中,行场扫描电路一般是采用具有正反馈环路的施密特触发器加上RC定时元件构成。自动频率控制一般是将行逆程脉冲经积分电路变换成锯齿波,再与行同步脉冲一起送到AFC鉴相器中。鉴相器根据上述两路输入信号的相位关系,产生误差电压去控制行振荡器的频率与相位,以确保与发送端同步。场振荡电路的同步是由场同步脉冲对场振荡器的同步触发来完成的。这种传统的RC定时式行场扫描电路的最大弱点是稳定性不够,故常设行、场同步调节旋钮,同时也增大了故障率。为此,近年出品的彩电都废除了上述传统RC定时式行场扫描电路,而采用了数字分频式行场扫描电路,它的优点是:

●提高了电路工作稳定性,减少了集成电路功耗。

●响应速度快,极大地提高了行场扫描电路的抗干扰能力。

●减少了机器元器件,降低了成本,简化了调整手续。

●彩电制式转换十分方便,只需通过制式开关给出控制信号,切换VCD晶体和组合电路的逻辑关系(改变频率),即可实现不同制式的切换,且不必增加很多外围元器件。

●可获得多种定时精度高、脉冲宽度准确的定时脉冲,如色同步选通脉冲、部分CPU无信号关机必须的计时脉冲等。

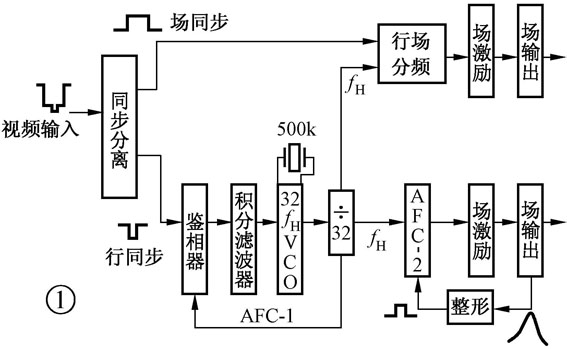

数字分频式行场扫描电路组成如图1所示。由图1看出,行扫描电路包含有两个锁相环路。一是由鉴相器、积分滤波器、晶体压控振荡器(500kHz VCO)及32分频器构成的自动频率控制电路,称为AFC-1。任务是用来产生频率和相位都很准确的行频脉冲,确保与发射端同步。二是AFC-2环路,任务是随时校正行激励脉冲的波形,以确保行逆程时间、行输出管正向导通时间及电流峰值稳定,基本上不受行输出电路负载变化的影响。场扫描电路由行场分频电路、场推动及场输出等部分组成,其核心是行场分频电路,它包括由多级双稳态触发器组成的异步式计数器和组合逻辑电路。为了使读者能对数字分频式行场扫描电路有一个清楚的了解,下面以M51308 SP集成电路为例,作具体介绍。

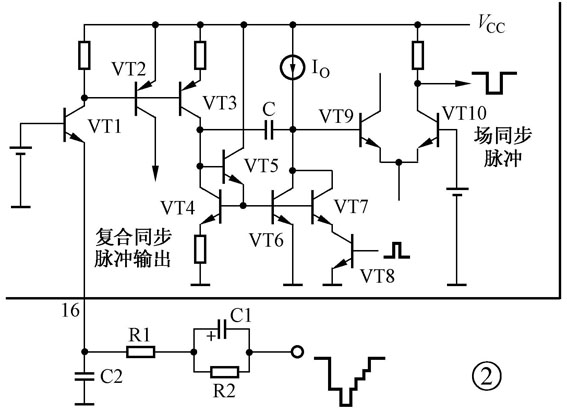

1.同步分离电路

该电路在M51308 SP内部,其电路见图2。从输入的视频信号加至VT1发射极,当同步头信号没有到来时,VT1处于微导通状态,导通电流由电阻R1、R2来决定。当同步头到来时,由于大电容C1上电压不能突变,大阻值电阻R2被C1短路,则同步头的负跳变只通过小阻值电阻R1加至VT1的发射极,使VT1以较大电流导通,其集电极电位下降,此时电容C1正向充电,两端电压上升。即视频信号的同步头过去以后,由于C1两端电压升高,使VT1发射极电位上升,使VT1变为截止,其集电极电位又回至高电平。也就是说,在同步头到来时,在VT1的集电极产生一个负脉冲,这便是分离出来的复合同步脉冲。同步头过后,靠电容C1的电压保证VT1仍处于截止状态,但C1可通过电阻R2及C2缓慢放电,为下一同步头到来时VT1再次导通作准备。VT1集电极产生的负极性复合同步脉冲,经VT2倒相成正脉冲,即所需要的复合同步脉冲,经过分离电路可得到行同步脉冲。负极性复合同步脉冲部分也作用于VT3基极,在该脉冲未到来时VT3截止,电流源VT4~VT6也截止。但差动放大器VT9导通、VT10截止,VT10集电极应为高电平。当复合同步脉冲中的行同步脉冲到来时,VT3导通,于是VT5、VT4、VT6导通,电容C被充电,电流流向是VT3集电极→C→地,使VT9基极电位下降,但由于行同步脉冲持续的时间短,VT9基极电位下降得不多,VT9、VT10的状态不变,即行同步脉冲不会通过VT9、VT10输出。当场同步脉冲到来时,VT3~VT6导通时间长,C充电时间大大延长,于是VT9基极电位下降很多,使VT9截止、VT10导通,VT10集电极为低电平。当场同步脉冲过去后,VT9、VT10状态又发生翻转,VT10集电极回到高电平,于是在VT10集电极便产生正的场同步脉冲。另外,有一个窄脉冲在场同步脉冲即将到来时,作用于VT8基极,使VT8饱和,为VT7导通准备条件。当场同步脉冲到来后,VT6与VT7并联导通,加大了电流,使C充电更快,VT9基极电位下降得更迅速,使VT9、VT10准确可靠地翻转。

2.行扫描电路

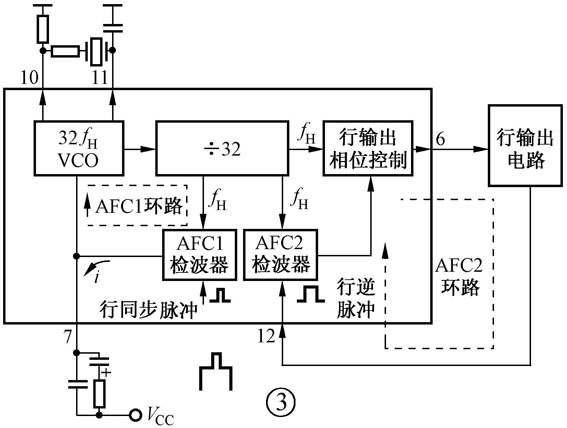

行扫描电路由行振荡器(500kHz VCO)、32分频器、AFC1环路、AFC2环路、行驱动电路以及一致性检测电路等构成,如图3所示。M51308SP⑩、外接500k陶瓷振荡器、RC元件与集成电路内的移相网络、相位合成网络等构成500kHz压控振荡器(VCO),其振荡输出送至由五级双稳态触发器构成的32分频电路,分频得到的行频方波与来自同步分离电路的行同步脉冲一起送至AFC1检波器。它能鉴别行振荡脉冲与行同步脉冲的相位差,产生正或负的鉴相电流,经⑦脚外接的低通滤波器变为直流电压去控制并锁定VCO的振荡频率与相位,使其与发送端严格保持一致。

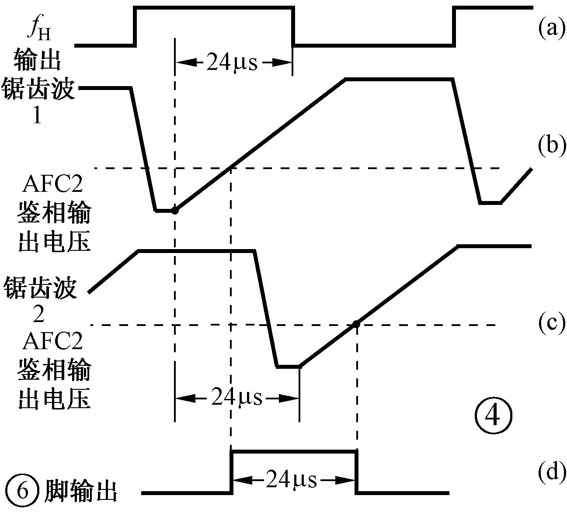

AFC2锁相环路由32分频器、AFC2检波器、行输出相位控制电路及行输出电路等组成。32分频器输出的频率与相位是已和行频严格同步的方波脉冲,延迟4μs后加至AFC2检波器的一个输入端,同时行输出变压器送出的行逆程脉冲由M51308SP送至AFC2检波器的另一个输入端。AFC2检波器鉴别两路信号相位差,产生对应的误差电压去控制行输出相位控制电路输出相位控制脉冲,使⑥脚输出的行激励信号相位得以控制,即可调节行逆程的开始时间,使行输出管的正向导通时间及电流峰值均得以校正。比如行输出电路负载变化(如亮度变化),导致行逆程时间、逆程偏转电流的负向幅度发生变化,从而引起行输出管正向导通时间及电流峰值也改变,但由于AFC2检波器输入的行频方波相位已被锁定,故行逆程时间的变化必然导致AFC2检波器输出正的或负的直流分量,即AFC2鉴相直流电压上升或下降。由图4可看出,M51308SP⑥脚输出的行激励脉冲前沿提前或滞后到达,会使行输出管的正向导通时间及电流峰值得以校正。⑥脚输出的行激励脉冲前沿移动范围是向前8μs、向后12μs。

3.场扫描电路

M51308SP集成块的场扫描电路由场分频电路、锯齿波发生器、场激励等构成。由双稳态触发器构成的场分频电路对2f\(_{H}\)(2×15625Hz)脉冲分频,从而获得场频脉冲信号,同时来自同步分离电路的场同步脉冲对场分频电路进行复位,以保证所产生的场激励脉冲与场同步脉冲严格同步。场分频电路等效电路见图5。

10级双稳态触发器串联构成异步分频计数器。

分频器中部分触发器的输出送至组合逻辑电路进行逻辑判断,判断结果去控制与门电路的状态。在每一场开始时,与门输出为低电平,双稳触发器按二进制规律分频计数,到该场快要结束时,组合逻辑电路输出由0变为1,与门开启,当场同步脉冲到达,通过与门使各级双稳态触发器的异步置零端复位,该场结束。这时逻辑电路的输出由1回到0,与门关闭,同时使各级双稳态触发器的异步置零端变为0,开始新一场的计数分频。

概括地说,就是场同步脉冲作为计数分频电路的置零脉冲,计数分频电路末级输出脉冲的频率严格等于场同步脉冲的频率。若场频为50Hz,则与门开门时间在276~352个行脉冲之间,换成频率则为44Hz~56.5Hz,这便是场频为50Hz时的场同步引入范围。若场频为60Hz,则与门开门时间在232~296个行脉冲之间,场同步引入范围为53Hz~67.8Hz。场分频电路输出的场激励脉冲宽度为:50Hz时为21个行周期,60Hz时为17个行周期(行周期为64μs)。

(王绍华)