本文介绍用AT89C51单片机构成的八位数字频率计的原理与制作。

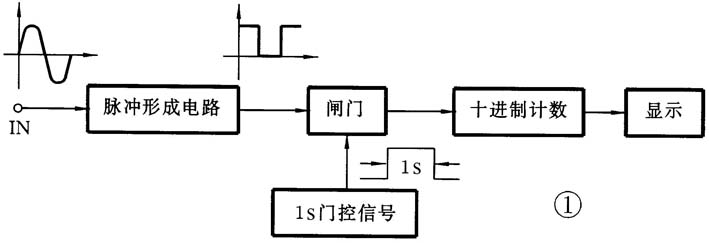

频率计的原理方框图如图1所示。首先,把被测信号A(以正弦波为例)通过脉冲形成电路转变成脉冲B,其重复频率等于被测频率,然后将它加到闸门的一个输入端。闸门由门控信号C来控制其开、闭时间,只有在闸门开通时间内,被测脉冲B才能通过闸门,送到十进制电子计数器进行计数。计数的结果通过LED数码管等显示器件显示出来,就是被测信号的频率。

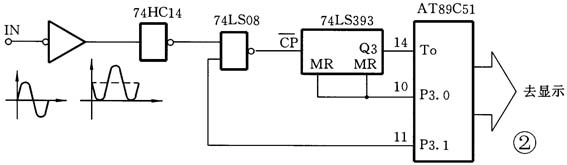

实际电路的原理方框图如图2所示。前置放大器完成信号放大、电平平移的任务,被测的交流信号D被放大、平移成脉冲直流信号E,再经74HC14施密特反相器整形成矩形脉冲。与门74LS08作为计数闸门,方波信号被送到与门的一个输入端,与门的另一个输入端连接1s门控信号,实际制作中连接AT89C51的(P3.1)。当为高电平时闸门打开,低电平时闸门关闭。电平的高低可通过指令加以控制。闸门开时矩形脉冲送到74LS393进行计数和分频,74LS393是双4位二进制计数器,在这里接成级连方式,组成一个8位二进制计数器,同时也是分频比为256的分频器。采用74LS393的理由是:AT89C51内有2个16位的二进制加法计数器,一个用作定时器,另一个用作脉冲计数。16位二进制的最大计数值为2\(^{16}\)-1=65535,不能满足精确测量的需要,虽然可以通过软件计数的方法来提高分辨率,但是AT89C51内置计数器的计数速率受500kHz(24M时钟)的限制,所以意义并不大。74LS393的最大计数速率可达50MHz,与AT89C51内的T0组成24位的计数器,其最大计数值为2\(^{24}\)-1=16777215,分辨率大大提高。本电路中没有采用十进制计数,因为AT89C51内置计数器只能进行二进制加法计数,计数结束后再进行二进制转十进制运算,然后将结果送到显示缓冲区进行显示。

完整的电路如图3所示,AT89C51外接晶振为24MHz,该晶振的频率稳定性十分重要,因为它也是门控信号的时间基准。内置计数器可通过软件设置对振荡频率的12分频进行计数/定时,这里将T1置为方式2,即常数自动重装入的8位定时器,并将其初值置为06。这样,每12×250/24M=125μs发生一次定时器T1中断,在T1中断的入口处(001BH)对中断的次数进行软件计数,当中断次数为1s/125μs=8000次时,历时1s。在计数开始时使用SETB P3.1指令打开闸门(74LS08),经74HC14整形后的脉冲信号通过74LS08的一个与门至74LS393进行计数,其计数值作为频率计频率值的低8位(D0~D7),1s后关闭闸门,其计数结果通过P1口读入,D7位(74LS393的其中一个Q3)与AT89C51的T0引脚连接,T0计数值作为频率计的D8~D23位。关闭闸门后,CPU将计数结果送至20H~22H单元,其中20H单元存放低位字节(从P1口读入的数据,即74LS393的值),21H和22H单元分别存放TL0和TH0的值,然后调用二进制转十进制子程序,把二进制的计数结果转为十进制,送至30H至33H(压缩的BCD码)单元,显示子程序则将BCD码经查表指令译为7段LED字形码,然后进行显示。

实际制作中数字处理部分只要连接无误便可正常工作。前置放大由于频宽达20M以上,故对不太熟悉高频电路的爱好者来说有一定难度。笔者经过精心挑选,采用两级结型场效应管组成的电路具有电路简单、高频、高输入阻抗的特点,较容易制作成功。由于电路比较简单,可直接在万能板上布线,信号引线应选用高频屏蔽线,制作完毕后通电测试,业余条件下可选一走时准确的石英钟,其晶振频率为32768Hz,用屏蔽线芯接触晶振的某一端,频率计应显示为32768。若有一定误差,可在程序中合适的位置增减NOP指令来微调闸门的启闭时间。本自制频率计的相关程序放在本期配刊光盘的“本期程序”文件夹中,读者可到光盘中查看。

(谢志芳)