以PSPICE语言为内核的电路仿真软件主要用于分析模拟电路。用这些软件分析数字电路时,只能用瞬态分析功能观察电路的时域曲线。PSPICE的大多数分析功能(如交流小信号分析、参数分析、直流分析等),在数字电路研究中无用武之地。数字电路分析的重点是输出量和输入量之间的逻辑关系,因此需要以逻辑分析为核心的仿真工具软件。

很多可编程逻辑器件(PLD)制造商为了推广它们的芯片,出品了各自的器件开发工具软件。如Lattice公司的Synari-o、Xilinx公司的Fundation、Altera公司的MAX+plus II等。这些软件能以VHDL等硬件描述语言来设计数字系统,也可以用电原理图设计逻辑电路。VHDL(Very high speed integrated Hardware Description Language甚高速集成电路硬件描述语言)出现于上世纪80年代。现已成为描述、验证和设计数字系统的标准语言之一。它可用于设计任意复杂的数字电路,硬件描述语言使设计数字电路的过程更像编写程序。用绘电路图的方法设计数字电路与设计模拟电路完全一样,使用者可以用电气图形符号设计各种组合逻辑电路和时序逻辑电路等。

现在高校用得较多的此类软件是MAX+plus Ⅱ(较新的版本是V10.21)。MAX+plus Ⅱ是一个全集成化的可编程逻辑设计环境。该软件功能强大、界面友好、在线帮助详实,可以设计多达上百万门的数字逻辑系统。用原理图的方法输入电路,可放置基本门电路(如与门、或门和非门等),使用74系列集成电路或功能更强的宏功能逻辑电路则更为方便。MAX+plus Ⅱ电路中观测的信号点数量没有限制,可方便地设置各个输入信号,可根据观测需要设置波形的显示方式,有非常强大的数字系统仿真功能。电子爱好者既可以用MAX+plusⅡ设计可编程逻辑器件;也可将它作为数字逻辑电路的仿真工具,不用搭建硬件电路就能对设计进行调试和验证。MAX+plus Ⅱ是一个学习数字电路技术理想的辅助工具。

Altera公司提供了免费的学生版MAX+plus Ⅱ。学生版仅支持逻辑门数较少的MAX系列PLD芯片,但软件的各种功能都与正式版完全相同。可从Al-tera公司站点www.altera.com下载MAX+plus II。为了得到授权文件,先要了解C盘的序列号:执行Options>Li-cense Setup命令,点击License Setup页system info按钮查阅C盘序列号。以此序列号到http://www.altera.com/auth-code/index-u.html 申请License.dat文件。公司将通过E-mail寄达授权文件。在MAX+plus Ⅱ的License Setup页License File or Server Name栏填入License文件的路径即可工作。图1是MAX+plus Ⅱ的界面。

我们将用实例说明在MAX+plus Ⅱ中用原理图设计和仿真数字电路的基本操作方法。MAX+Plus Ⅱ的工作流程为设计输入、项目编译、项目检验和项目编程等4个主要步骤。

一、设计输入

1.建立设计项目文件

和大多数工程设计软件一样,MAX+plus II用项目来管理设计文件。先建立设计项目文件,然后在项目文件下建立和产生各种设计文件。设计文件中有一个是顶层文件,顶层文件的文件名必须和项目文件名一致。编译器针对顶层文件进行编译。项目还管理各种中间文件(如波形文件等),所有中间文件的文件名应一致(系统自动赋予不同的后缀名)。由于系统在工作时会生成许多中间文件,所以最好将每个设计项目放在一个单独的子目录中。本文以一个双输入与门电路为例。

(1) 运行MAX+plus II,进入图1所示的系统界面。

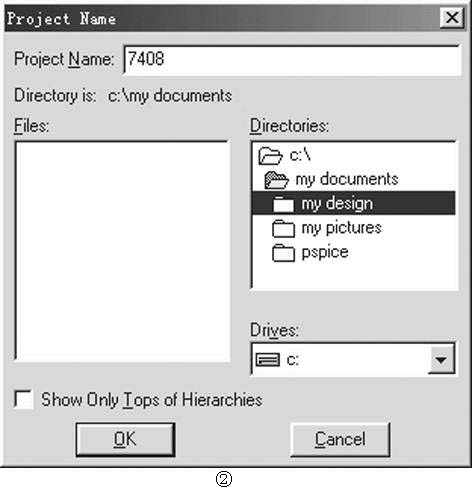

(2) 执行菜单命令File>Project>Name,打开项目文件名对话框(图2)。

在Project Name栏填入新建设计项目文件名“7408”,项目文件的后缀为.acf。点击“OK”按钮完成项目文件建立。

2.绘制电原理图

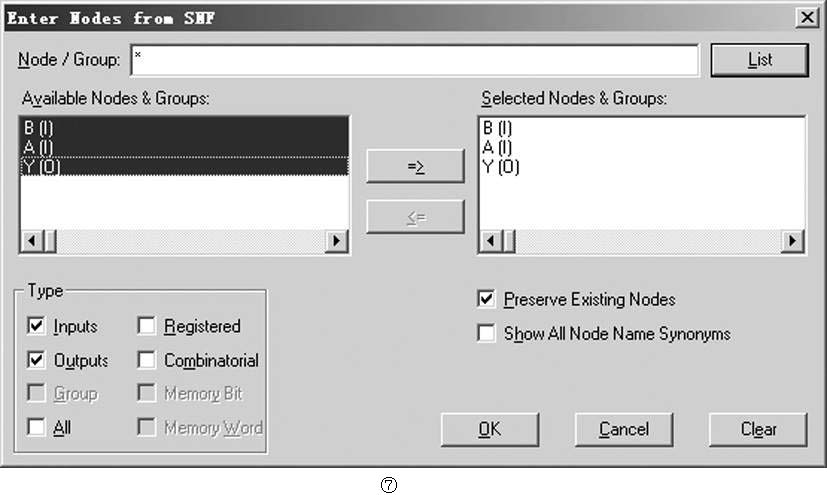

在已经建立项目文件的界面下,执行菜单命令File>New。打开新建文件对话框(图3)。

此对话框中,从上向下可选的文件类型依次为:图形编辑器文件、电气图形符号编辑器文件、文本编辑器文件和波形编辑器文件。选中Graphic Editor file,确定后进入图形编辑界面。按下保存文件按钮,弹出Save as对话框。按缺省的文件名保存为7408.gdf。

用鼠标点击图形编辑区中恰当位置后,执行菜单命令Symbol>Enter Symbol,或在图形编辑区双击鼠标,打开图形符号输入对话框(图4)。

MAX+plus II共有4个元件库,在目录MAXplus2\MAX2lib\下:原始数字元件库prim(包括缓冲器、门电路、触发器、输入端子和输出端子等);宏功能元件库mf(包括组合逻辑功能器件和74系列逻辑器件等);参数化模块元件库mega-lpm(数字电路系统常用的功能模块,如FIR滤波器,SDRAM控制器等);电子设计交换格式元件库edif(为设计数据交换用的工业标准格式元件)。

选择元件库mf,在Symbol Libraries区选中7408。确定后,在绘图区出现与门7408。双击图纸中的器件,则打开电气图形符号编辑器,可进一步编辑器件的内部电路。如果对元件名称比较熟悉,可在Symbol Name栏键入元件名称。如在符号名称栏中键入Input和Output,即在图纸中放置相应输入端和输出端的电气图形符号。把Input放在7408的输入引脚,Output放在7408的输出引脚。将输入端和输出端的元件标号分别改为A、B和Y,如图5所示。

如果要重复放置元件,只要先按下Ctrl键,再拖动该元件到另一处,即完成复制。选中一个区域后,用此法可复制选中的全部对象。欲旋转或翻转元件,先点击元件,使其处于选中状态(为红色),再调用Edit菜单的Rotate和Flip子命令,或主工具栏上的相关按钮。

需要添加元件连线时,将光标移到元件引脚上,光标变为十字形。按下鼠标左键拖至另一元件引脚,完成一个导线连接。选中连线后按Delete键即删除此连线。单击导线,使其处于高亮(为红色),为该导线所联系的节点命名。节点名可用大写和小写的字母、数字和一些符号,如斜线“/”、连字号“-”和下划线“—”等。

使用总线(Bus)让图纸简明易读,也可减少绘图工作量。从元器件总线端引出的连线系统自动设置为总线。总线有两种命名方法:以单个节点命名,如A0,A1,A2;以数组方法命名,如A[2..0]。

二、项目编译

电路绘制完毕,用编译器(Compiler)对电路图作基本的处理与错误检查,包括电路网络表提取到最后编程文件的生成。在编译过程中自动产生时序仿真、器件适配等文件。如在编译中发现错误,系统停止编译,弹出提示信息,指示错误发生的位置和原因。

完成电路图输入后,执行界面主菜单MAX+plus Ⅱ>Compiler命令,打开编译器(图6)。

启动编译器后,系统进行一系列的分析处理,最终建立多个必要的设计文件。编译器首先提取定义连接设计文件层次的信息,然后检查设计中的错误。最后建立设计组织图和数据库。如果设计中存在错误,将在messages-Compiler信息窗口中给出详细的说明,出错信息用红字列出。

编译器调用的工具依次为:

(1) Compiler Netlist Extractor网络表提取器,建立图形设计的网络表,并检查其逻辑正确性;

(2) Database Builder数据库构造器,产生一个精简的项目数据库;

(3) Logic Synthesizer逻辑综合器,对设计进行逻辑综合,简化逻辑算法;

(4) Partitioner分割器,将一个项目的逻辑分割到若干同一系列的器件中,前提是项目中采用了两个或两个以上的芯片,或者一个芯片装不下该设计。学生版没有此功能;

(5) Fitter适配器,计算可编程逻辑器件的布局和布线;

(6) Timing SNF Extractor时序仿真网络表提取器,产生时序仿真的标准时延文件;

(7) Assembler装配器,产生可编程逻辑器件的配置文件。

如果我们只是仿真分析数字电路的逻辑关系,而不实际烧录CPLD芯片的话,可以不理会这些过程。

三、项目检验

编译后如果没有错误提示,就可以进入时序仿真阶段。

1.建立波形文件

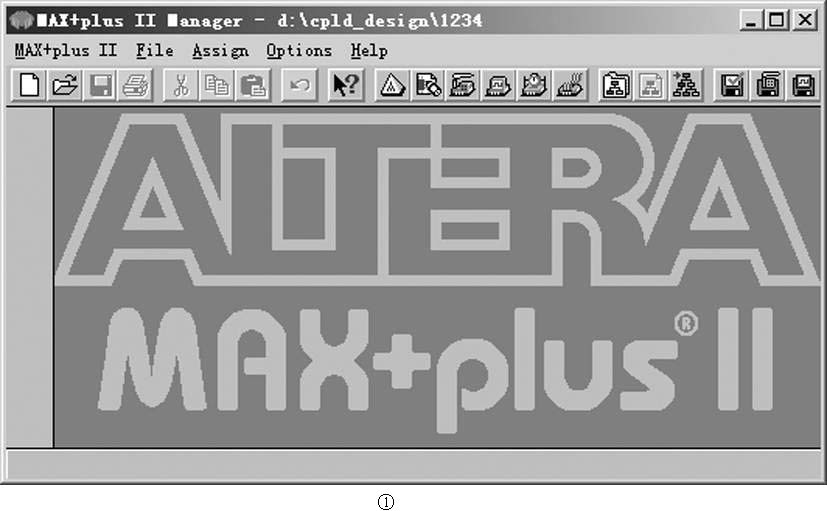

打开图3所示新建文件对话框,选中Waveform Editor File(用.scf格式)项。建立一个新的波形编辑文件(图8),用系统提示的缺省文件名保存。

2.导入观测节点

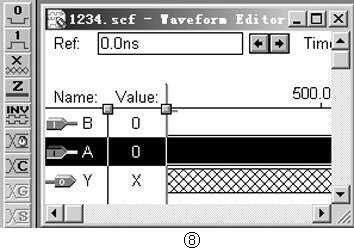

执行菜单命令Node>Enter Nodes From SNF,或从图形工作区的弹出菜单中调用此命令。打开“Enter Nodes From SNF”对话框(图7),从SNF(仿真节点)文件输入拟观测的节点。

Node/Group栏中填入拟列出的节点名,缺省为星号“*”,表示将列出电路图中全部节点。Type区是节点类型过滤,只有符合选中类型的节点,点击List按钮后才能显示在Available Nodes & Groups列表中。选中的信号以反相显示,按下向右箭头按钮,将这些节点调入Selected Nodes & Groups区。

3.编辑节点波形

在图8的波形编辑器中,已调入输入和输出节点。用编辑器窗口左面的工具按钮对输入节点赋值。当前有效的按钮依次是:赋值“0”、“1”、“不定值”、“高阻”、“(将已有信号)反相”、“时钟”和“周期信号”。最下面两个按钮对信号组和状态机赋值。可以对一个节点分段赋予不同类型的值。

我们现对输入节点赋以周期信号值。选中节点A,点击周期信号按钮 ,弹出对话框图9。

在图9中,“To:100us”是此周期信号的终了时间,可用菜单命令File>End Time改变;Count Every是信号半个周期的长度;Multiplied By是Count Ev-ery栏的倍率。如此值是2时,产生信号的半周期为200ns。设置好的输入波形如图10所示。

4.运行仿真

先保存文件,再执行菜单命令MAX+plus II>Simulator,在弹出对话框中点击“Start”按钮,开始仿真。如果没有错误,得到输出节点Y的波形图线。从图10中可以看出,输出信号有6ns的延迟,反映了器件工作的实际物理过程。

5.改变数据显示方式

为便于观测数据,可将多个输入(输出)数据作为一个数组来显示。先选中A和B两个输入信号:点住信号名B并向下拖动鼠标至A,即将A和B两个节点图线选中。执行菜单命令Node>Enter Group,弹出图11所示的 Enter Group对话框。在Group Name栏中填入信号组的命名;在 Radix区中选择数字的进位制;选项Display Gray Code Count As Binary Count决定在以二进制计数时是否以格雷码显示。

确定后得到图12所示波形图。Value列中前面的字母表示数制,其后的数字表示该波形在光标处的值。双击Value列数字也可打开图11对话框,改变显示的数制。

四、项目编程

项目编程是将设计下载到器件中,需要硬件配合。有关此项技术,请参阅相关专著,本文从略。

MAX+plus II不仅可用来仿真数字电路,它所包含的可编程逻辑器件(PLD)、硬件描述语言(HDL)等都是非常实用的新技术,值得电子爱好者关注和学习。

(甘雨)