2.逻辑分析仪

逻辑分析仪主要用来测试以微处理器为核心的数字系统。在数字硬件电路、嵌入式系统和监控软件的研制和调试过程中,逻辑分析仪都是一个必备的工具。逻辑分析仪有多种触发模式。不管被测系统多么复杂,逻辑分析仪都能准确地找到那些隐蔽的、偶然的特殊时刻,然后把触发条件发生前后各信号的数据流保存和显示出来。逻辑分析仪至少有16个测量通道。通道数越多,仪器能检测的数据信息量越大。

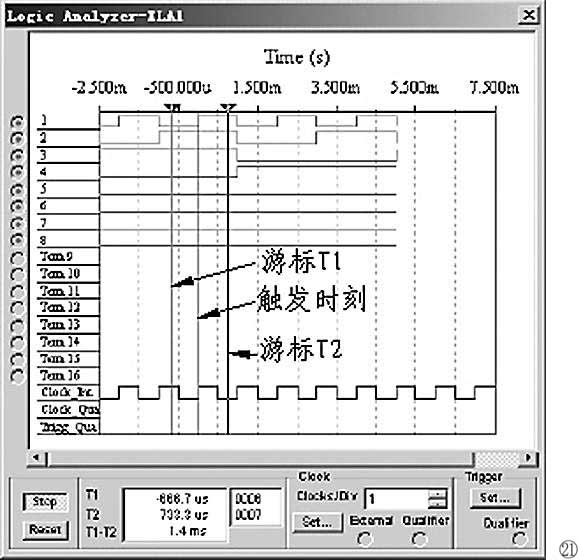

Multisim的虚拟16通道逻辑分析仪有伪波形和十六进制数字两种显示方式。它支持内部或外部的时钟、上升沿或下降沿触发和字组合触发模式。允许向前或向后滚动窗口查看信息,用游标定位数据和计算时间差。

逻辑分析仪图标上1~F为16个信号接线端。其界面上的16个圆点对应于16个输入信号接线端子。波形的颜色和接线的颜色一致。波形的名称就是信号线的网络名,便于检查信号的来源。

在波形窗口中,用游标来定位时序窗口中数据点的时刻,测量事件之间的时间差和读出数据值(以16进制表示)。时间值和数据值分别显示在界面下部的两个读数窗口中(见图21)。

在仿真运行中和结束后均可执行菜单命令View/Show/Hide Grapher,调出波形分析窗口,更好地显示和分析逻辑图线。

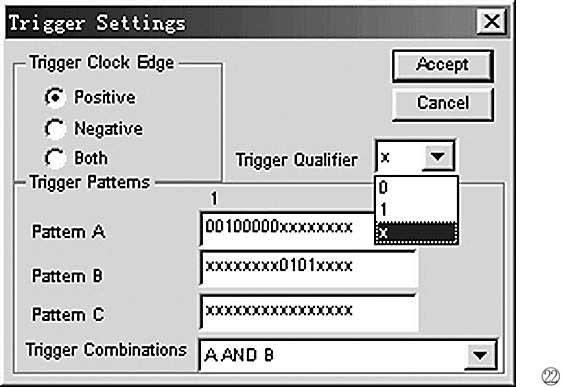

逻辑分析仪从一串漫长的序列中获取数据,所以如何定位在需要观察的数据点附近成为一个重要的问题。逻辑分析仪用触发来定位数据的获取点。可由数据字、数据字组合或事件来控制定位,选择数据波形在窗口中的位置。仪器一旦检测到符合触发条件的样本,并且该触发位于所要求的存储器位置时,就停止采集更多的样本。触发在存储器中的位置被称为“触发位置”。仪器立即将此点附近的一系列数据保存在存储器中,这个过程就是触发。这个特定的参考点被称为触发字。图22是逻辑分析仪的触发设置对话框。

(1) Trigger Clock Edge选择触发时钟沿。Positive以时钟上升沿触发;Negative以时钟下降沿触发;Both为两者均可触发。

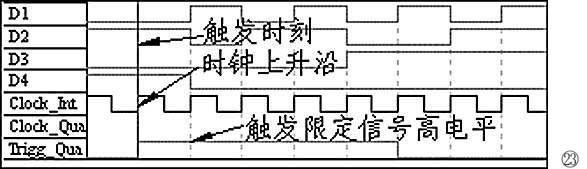

(2) Trigger Qualifier选择触发限定词。触发限定词的作用是过滤外部触发限定信号。触发限定信号连接在逻辑分析仪图标的T端子上。如果触发限定词被设为“x”(任意字,可为1或0),则限定词不起作用。触发信号一经确认,逻辑分析仪就被触发。如果触发限定词被设为“1”或“0”,则仅当触发限定信号和选定的触发限定词匹配时逻辑分析仪才能被触发。

图23是设置了触发限定信号的测试图线。时钟频率是1kHz,触发限定信号的频率是100Hz。Trigger Clock Edge设为上升沿触发,Trigger Qualifier设为1。触发条件是:时钟为上升沿,触发限定信号为高电平。

(3) Trigger Patterns触发字设定。仪器检查数据线的信号,当数据的组合形式和设定的触发字组合一致时,才能导致触发。可设置3个触发字A、B和C,触发字为16位二进制数,可用的字符为0、1和x。要注意触发字设置的位置排列是低位在左,高位在右,与字发生器中排列的方向正好相反。

① 逻辑分析仪的1~F接线端都有信号时,触发字可由1和0组合而成。如0010000000000000。如果逻辑分析仪只接上了部分数据线,则对应于未接线的数据位必须以x填充。如只在前8位接了线,则触发字应表示为00100000xxxxxxxx。

② 应用“与”触发组合时,可能要用2个或3个信号源。触发字要对应于各自的信号源。如触发字组合为“A AND B”,字发生器XWG1以0~7接到逻辑分析仪的1~8端,XWG2以0~7接到逻辑分析仪的9~F端。此种情形下,前一个触发字的后8位应填以x,而后一个触发字的前8位应填以x,如图22所示。

(4) Trigger Combination触发字组合。一共有6类21种触发组合形式。

① A为单一事件触发: 找出A,然后触发并填入存储器。

OR B为“或”触发:找出A或者B之中的一个,然后触发并填入存储器。即任一事件先产生都将满足本条件。

AND B为“与”触发。找出A,同时找出B,然后触发并填入存储器。AND关系是事件A和事件B同时出现,由于电路中两个或多个事件极难真正同时出现,此条件是受制约的。为了满足一个AND条件,两个事件必须发生在同一时钟周期之内。

NO B为“非”触发。找出A,而此时B不出现,然后触发并填入存储器。A NO B用于把采集到的一组数据和参考数据进行比较,一旦两者不一致,即进行跟踪,采集数据。

THEN B为序列触发。找出A,接着找出B,触发并填入存储器。序列关系是事件B在事件A后出现。事件必须按规定的次序出现。

THEN (B WITHOUT C)为具有序列返回的序列触发。找出A,然后当C不出现时找出B,触发并填入存储器。如果C出现,则触发无效。

(5) 时钟设置

Clocks/Div为窗口中水平分度显示的时钟期数,从1~128。点击Set按钮,打开时钟设置对话框,见图24。

① Clock source为设置时钟源,有外部和内置两种选择。一般选用内置时钟触发。

② Clock Rate决定内置时钟的频率。实际的逻辑分析仪为了准确捕捉信号,通常使用比被测线路更高的频率。但在Multisim的虚拟仪器中,内置时钟频率过高会使显示波形拉得太长,最好和信号频率一致。

③ Clock Qualifier时钟触发限定。时钟限定是用外部的另一信号来过滤外部时钟信号,使用内部时钟本选项无效。采用外部时钟触发时,在图标的C端接时钟信号,Q端接触发限定信号。也就是说逻辑分析仪同时接一个外部时钟信号和一个控制信号。时钟限定是指对所有存入存储器进而在屏幕上显示的数据加以限制的一种能力。时钟限定如果设为“x”,则限定无效。只要确认触发信号,样本就被读入;如果时钟限定被设为“1”或“0”,则仅当时钟信号匹配于选定的限定信号时,样本才能被读入和存储。

图25是应用时钟限定信号的测试线路。图中逻辑分析仪的外部时钟频率是1kHz,时钟限定信号的频率是100Hz。

Trigger Clock Edge设为下降沿触发,Clock Qualifier设为0。触发条件是:时钟为下降沿,时钟限定信号为0。图26是测试所得图线。

④ Sampling Setting为取样设定。普通示波器只能观察触发之后的信号波形,而逻辑分析仪的内置存储器可以保存触发前的信息。这样可显示相对于触发点时间坐标为负的数据。触发时刻的时间坐标为0,以一条竖直的绿线表示。

⑤ Pre-trigger Samples记录触发前的波形数目;Post-trigger Samples记录触发后的波形数目。

⑥ Threshold Voltage阈值电压。

图21所示波形图的触发条件是:时钟为上升沿;单个触发字A为11100000xxxxxxxx;触发前记录3个波形;触发后记录5个波形。

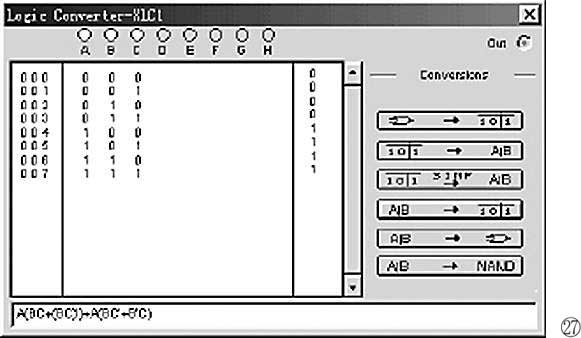

3.逻辑转换器

逻辑转换器能将数字电路的真值表、逻辑表达式和逻辑电路等三种表示形式相互转换。特别适合于学习和研究数字电路原理。

逻辑转换器的最上端是8个输入端和1个输出端,此端口是对于电路图而言。点击输入端,即可输入真值表。点击输出列的符号,其数字将按0、1、x顺序循环变化。在面板的右边是转换按钮(见图27)。从上向下依次为:

(1) 电路图转为真值表。将电路图的输入端和输出端分别与逻辑分析仪图标的输入端和输出端相连。按下此按钮即可得该电路的真值表。

(2) 真值表转为逻辑表达式。选定输入端,然后在真值表右面输出列中定义输出值。按下此按钮,相应的逻辑表达式会出现在面板最下面的逻辑表达式栏中。

(3) 真值表转为最简化逻辑表达式。按下此按钮后得到最简化的逻辑表达式。

(4) 逻辑表达式转化为真值表。在逻辑表达式栏中输入逻辑表达式,按下此按钮后得到真值表。

(5) 逻辑表达式转化为电路图。将输入的逻辑表达式转换为电路图。

(6) 逻辑表达式转化为与非门电路。将输入的逻辑表达式转换为全部由与非门构成的电路图。

利用逻辑转换器,我们可以方便地构建数字电路。化简复杂的逻辑式也只是举手之劳。

例如:化简逻辑式Y=A(BC+(BC)‘)+A(BC’+B‘C)。将表达式输入逻辑转换器后先化成真值表,再点击“真值表转为最简化逻辑表达式”按钮,得到结果为A。

4.数字电路仿真模型

在数字仿真中有两种模型可供选择:使用理想化元件以得到更快的仿真结果或者使用实际模型以得到更准确的结果。如果你需要较快的仿真过程,并且设计电路并不依赖于数字元件的详细性能,宜选择理想模型;如果你需要更接近实际情况的波形来说明采用LS或HC元件的电路响应情况,则宜选择实际情况模型。仿真模型的选项在执行菜单命令Simulate/Dig-ital Simulation随后打开的对话框中。

帮助菜单命令Help/Multisim Refer-ence打开仿真元件的参考资料,也包括了数字集成电路4000系列和74xx系统的全部逻辑函数,可备查考。

Multisim的生产商Interactive公司的网页是:www.interactiv.com,此软件试用版可在该网站上下载。

(甘雨)