随着计算机技术的快速发展,数字电路的应用越来越普遍。因此,逻辑电平测试器将成为数字电路设计试验及检查修理的常备工具。

逻辑电平的数码显示大多采用LED数码管,它是由特殊形状的LED发光二极管构成的光电器件,通常包括a~g7个笔段和小数点dp,共8只发光管。根据各发光管公共端接法不同,数码管被分成共阳极和共阴极两大类。共阳极数码管是将内部8只LED管的阳极(正极)连在一起引出后接电源正端,当某LED管的阴极(负极)加低电平时,相应的笔段发光;共阴极数码管则将8只LED管的阴极连在一起引出后接电源负端(或地端),当某管阳极加高电平时,对应的笔段燃亮。逻辑电平测试电路一般从被测电路获得工作电压,若采用单独供电,两者的地线必须相连。要求逻辑电平测试电路功耗低、电路简单、结构紧凑、使用和携带方便(可作成电平笔),因此应尽可能选用小尺寸微型高亮度或超高亮度的数码管。测试结果高电平可显示H或1,低电平可显示L或0。发光颜色可根据个人喜好,选择红、绿、黄等。

从逻辑电平的测试到最终显示结果,实际上是一个简单的逻辑电平变换过程,一般可用晶体管、数字逻辑门或电压比较器等来实现这种变换。本文将通过8个实用电路,介绍逻辑电平测试电路的具体设计方法和技巧,供读者参考。

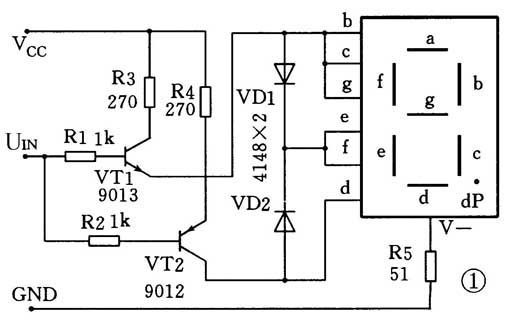

图1是使用NPN、PNP两种极性的晶体管和共阴极数码管组成的测试电路。正电源V\(_{CC}\)和地端GND用夹子与被测电路相连,U\(_{IN}\)端通过探针接被测点。当被测点为高电平时,VT1导通,b、c、g笔段为高电平并发光,同时经隔离管VD1使e、f笔段也发光,数码管显示出H字形;被测点为低电平时,VT2导通,d、e、f笔段发光,显示L字形。VD1、VD2起隔离作用,并完成逻辑“或”的功能(也可用二输入端或门代替),使显示H或L时e、f笔段均发光。调整R3、R4大小可改变高、低电平的检测阈值,调整R5可改变数码管发光亮度。

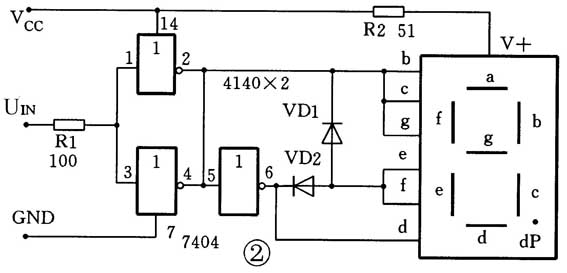

图2是使用TTL六非门(或称反相器)7404组成的测试电路。由于TTL(CMOS亦同)电路有确定的高、低电平输入阈值电压,因此无需另外设置或调整,测试结果非常精确。输入端的两个非门并联可增加驱动能力,高电平显示H,低电平显示L。由于使用共阳极数码管,故VD1、VD2的极性要改变(与图1相反)。如果测试CMOS电平,则应使用CMOS非门电路4069等。

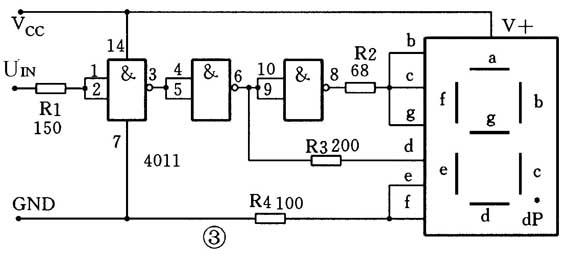

图3是使用CMOS与非门4011接成反相器组成的测试电路,也可用非门代替4011。高电平显示H,低电平显示L。由于R2~R4已起限流作用,因此数码管其阳极端直接与正电源V\(_{CC}\)相连。将高、低电平均需发光的常亮笔段e、f经R4接地,可减少驱动电流。

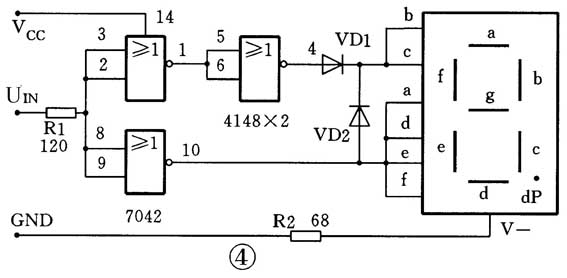

图4使用TTL或非门接成反相器,配用共阴极数码管,高电平显示1,低电平显示0。

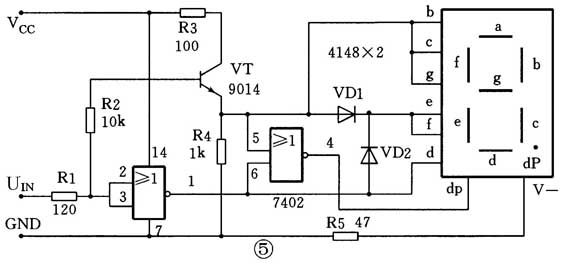

图5可通过点亮小数点dP指示开路(未测试)状态。高电平时VT导通,显示H;低电平时VT截止,7402①脚为高,显示L;探针开路时,7402的②、③脚相当输入高电平,①脚输出低电平。同时VT截止,⑤脚被R4下拉为低电平,④脚输出高电平仅驱动小数点dP发光。

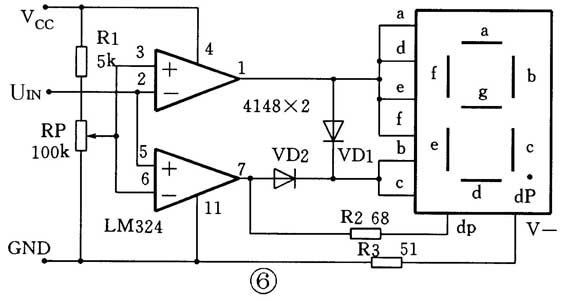

图6是使用电压比较器LM324组成的测试电路,其特点是便于检测阈值电平的调整,可测试DTL、TTL、CMOS等多种逻辑电平。由电压比较器的原理可知:当同相输入端(正端)电压高于反相输入端(负端)电压时,比较器输出高电平;反之,则输出低电平。RP为比较电压调整电位器,当U\(_{IN}\)高于设置电压时,⑦脚输出高电平,显示1,同时小数点dP发光;U\(_{IN}\)低于设置电压时,①脚输出高电平显示0,但小数点不亮;当U\(_{IN}\)检测到高、低变化的时钟脉冲时,若频率很低,可见0、1交替显示。频率较高时1、0变化非常快,所以只见显示为0,同时小数点dp发光,这种“带点的零”即可表示检测的是时钟脉冲。对于用H、L代表高、低电平的测试电路,在检测到较低频率的时钟脉冲时,H、L会轮流出现,频率较高时将显示H、L合成的字形“”。

与图6相比,图7可通过电阻R1~R4设置不同的高、低电平检测阈值。阈值电压可由分压公式算得,按图示R1~R4取值时,⑨脚高电平阈值为2.3V,⑤脚低电平阈值为0.8V。当U\(_{IN}\)≤0.8V时⑦脚输出高电平,VT导通,显示0;U\(_{IN}\)≥2.3V时⑧脚输出高电平,显示1,小数点dp发光;当U\(_{IN}\)输入时钟脉冲时,显示“带点的零;当U\(_{IN}\)处于0.8~2.3V之间时,⑦、⑧脚均输出低电平,数码管任何笔段均不发光(无显示)。

图8使用单时基电路NE555构成测试电路,利用NE555内部两个电压比较器和由三只5kΩ电阻组成的电阻分压器(故称其为555),②、⑥脚并接作测试输入端,高、低阈值刚好相差一倍,由RP调整确定。例如测试TTL电平时,调节RP使⑤脚为2.4V,测⑥脚触发高电平为2.4V,②脚触发低电平为1.2V,即当U\(_{IN}\)≥2.4V时显示1,U\(_{IN}\)≤1.2V时显示0。