本文介绍的脉冲发生器可产生单脉冲、短脉冲群和脉冲流,作为集成逻辑电路的注入控制信号。与逻辑笔、逻辑夹配合使用时,逻辑脉冲发生器作为激励源,逻辑笔、逻辑夹用来监测受激器件输出状态。

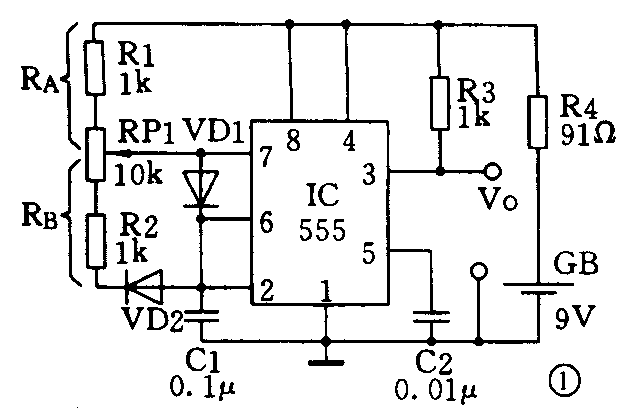

一、占空比可调的脉冲发生器

该电路主要使用555时基集成电路和部分元器件组成,如图1所示。它可以产生占空比可调的脉冲信号加到数字电路中用于检测电路的好坏。

由日可见,该电路接成无稳态多谐振荡器,电容器C1与R1、RP1、R2组成充放电电路。二极管VD1、VD2把电容器C1的充电和放电通路分开。电容器C1通过R\(_{A}\)和VD1充电,通过RB和VD2放电,调节电位器RP1改变R\(_{A}\)和RB的数值,改变充放电时间,也就改变了脉冲的占空比,成为占空比可调的脉冲发生器。

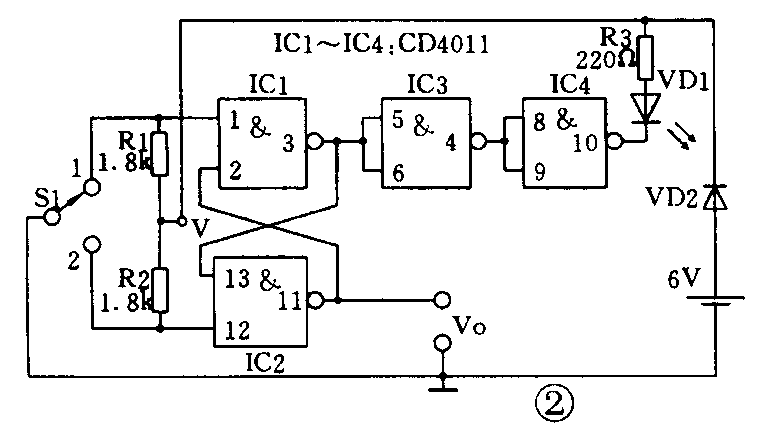

二、逻辑脉冲发生器

图2是用CD40ll四2输入“与非”门构成简单的逻辑脉冲发生器。IC1、IC2构成RS触发器,由负脉冲触发。IC3、IC4接成反相器,把发光二极管VD1与基本RS触发器隔离开。S1是回簧开关,平时S1与1端相连,按下S1时才与2端相连。

用CD4011的两个与非门IC1、IC2组成的负脉冲触发的RS触发器,其两个反向输入端1脚、12脚分别与两个上拉电阻器R1、R2相连,并分别与别的常闭、常开触点相连,S1的簧片接地。通常,当S1未按下时,常闭触点与地接通,l脚为低电平;常开触点悬空,12脚为高电平,此时触发器处于被复位状态,输出端11脚为低电平。当S1按下时,12脚接地为低电平,l脚悬空为高电平,触发器被置位,11脚输出高电平。松开S1时,触发器重新被复位。这样,每按下S1一次,触发器的11脚便输出一个正向脉冲逻辑信号,因此该电路又称为单脉冲电路。使用时把探针放在脉冲进入电路的地方,按下开关即可。假若被测电路需要负脉冲,先按住开关然后放开,再按住开关,便得到负脉冲。当11脚输出正脉冲时,3脚输出负脉冲,经两个反相器后,加到发光二极管VD1的负端,VD1的正极接到电源正端,故发光二极管发亮。

二极管VD2一方面防止电池接反,起保护作用,另一方面利用它的正偏压降,在使用6V电池时,实际加到电路中的电源电压约为5.3V。

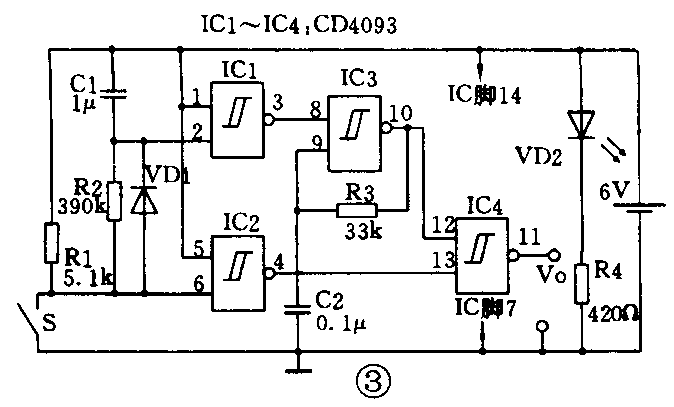

三、延迟脉冲发生器

该电路是用有施密特触发器的四2输入与非门CD4093和一些电阻器、电容器构成。电路图如图3所示。

CD4093在电路中由IC1、IC2、IC3、IC4组成,其中IC3与R3、C2接成可控振荡器,振荡频率由R3、C2决定。当IC1输出高电平时,IC3开始振荡;若IC1输出低电平,IC3就被迫停振。IC1的输出又由其输入状态而定。IC2输出信号用来控制与非门IC4,也就是当IC2输出高电平,IC4输出可控振荡器IC3产生的信号,反之IC2输出低电平时,IC3输出高电平,IC2的输出又由其输入状态而定。当开关S按下之前,IC1和IC2输入端均为高电平,于是其输出均为低电平,使IC3、IC4被封锁。

当开关S接通后,C1上电压不能突变,IC1仍暂输出低电平,于是IC3仍被封锁,IC2输出高电平,从而IC4封锁被打破。C1经充电后,即经过一段延迟后,IC1输出呈高电平,IC3开始振荡,产生脉冲经IC4反相后输出。当放开S时,C1经R1、R2、VD1放电,IC1、IC2输出低电平,IC3、IC4被封锁。

显然,改变C1、C2可改变电路的延迟时间,本电路的延迟时间大约为0.5s。脉冲重复频率可通过改变C2、R3来调节。本电路的脉冲重复频率为200~300Hz。

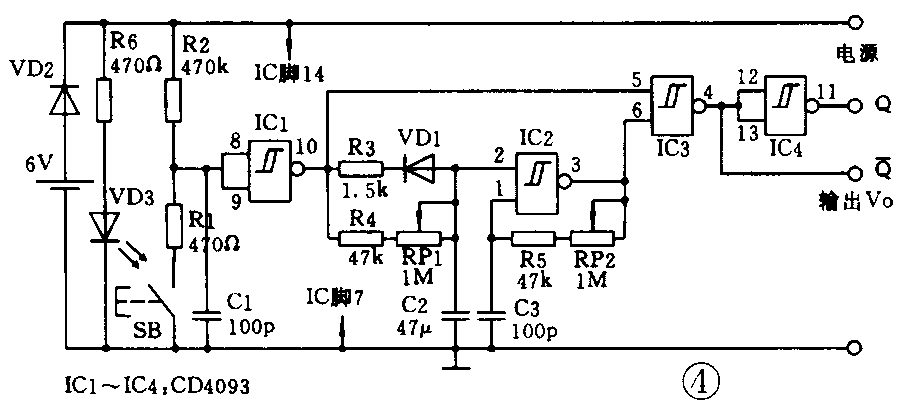

四、脉冲和脉冲串发生器

图4所示电路能产生正负脉冲串。它是由一片四2输入有施密特触发器的与非门CD4093和一些电阻器、电容器等构成。

CD4093集成电路中IC1、IC4作反相器使用;IC2与C3、R5、RP2组成可控振荡器,其2脚的电位控制振荡器振荡与否;IC3作为有施密特触发器的与非门。IC1的8、9脚在开关SB未按下时处于高电位,按下开关SB时,则处于低电位,放开SB后,IC1的8、9脚又处于高电位;这样,当按一下开关SB便立即松开,给IC1的输入端一个负脉冲信号,再经IC1反相整形,又经IC3、IC4输出两个相位相反的单脉冲信号。

当按下开关SB时间较长时,IC1输出高电平,通过R4、RP1向C2充电,使端电压上升到IC2的门限电平时,由IC2组成的振荡器起振并产生脉冲串信号。这些脉冲串经IC3、IC4后输出正负脉冲串信号。脉冲串的频率用RP2调节。R3、VD1用来保证C2迅速放电,以避免重复按动SB时振荡器不起振。

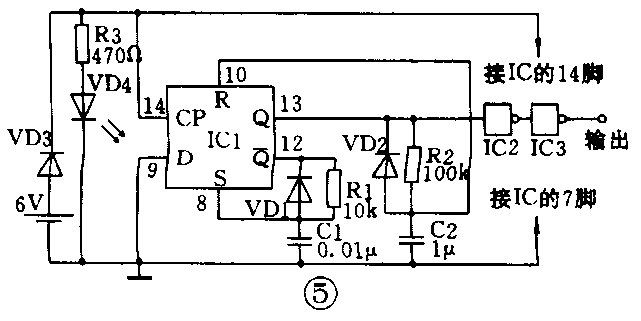

五、用D触发器的可调脉冲发生器

电路如图5所示。图中IC1是D触发器,CP是时钟脉冲输入端,D是数据输入端,R是复位输入端,S是置位输入端,Q为触发器输出Q-,可为触发器反相输出端。IC2、IC3为两个反相器。它们共同组成占空比可调的脉冲发生器。

假设图 5中初始状态 Q为低电平,Q-为高电平。Q-端通过R1对C1充电,使S点电位逐渐升高,达到置位电平时,则Q端由低电平变为高电平,Q-端由高电平变为低电平。此时,C2开始被充电,C1通过与R1并联的二极管VD1放电,R端电位逐渐升高,达到复位电平时,则Q端由高电子变为低电平,Q-端由低电平变为高电平,完成一个振荡周期。通过反相器将Q端的脉冲输出。这样,脉冲持续时间T2约为0.66R2 C2,截止时间T1约为0.66R1 C1,重复频率f=l/(T1+T2)。由图可见,决定时间常数T1和T2的是两个完全分开的RC电路,可以分别调节,互不影响,实现了占空比可调的脉冲发生器。

D触发器选择CMOS系列集成电路CD4013,它的内部含有两个D触发器,我们只用其中一个。反相器选用CD4069集成电路,内部含有六个反相器,我们只用其中的两个。(翟春林)