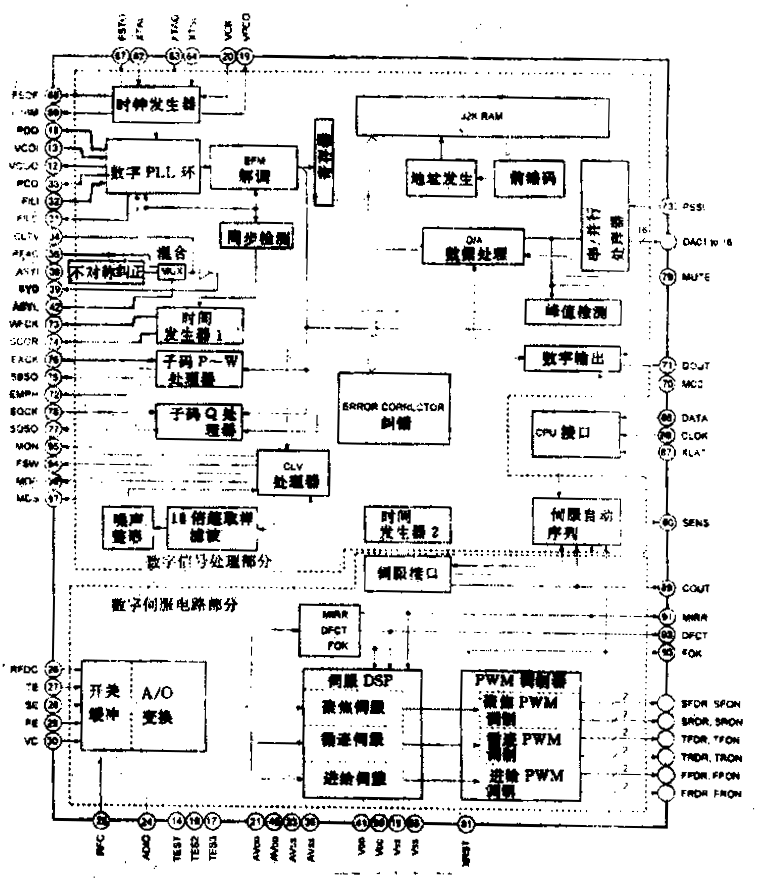

CXD2545Q是索尼公司生产的数字信号处理和数字伺服大规模集成电路,亦称数码平台。在VCD机中用于组成数字伺服系统。该集成电路内含数字信号处理(DSP)和数字伺服处理(SSP)两大部分。其中DSP部分与1990年生产的,在CD及VCD机中大量应用的CXD2500基本相同,经实践表明性能优异可靠;SSP部分引入的优点是可用外界CPU对数字伺服环路进行基于软件的控制,使以前模拟伺服系统中必须用电位器调整的寻迹/聚焦偏置及增益可实现免调试,从而提高读片性能和整机可靠性。CXD2545Q的内电路框图及各引脚功能说明分别如附图和附表所示。该集成电路采用100引脚四列扁平塑封(100pin QFP)结构。(王德沅)

f燘f

附表

管脚号 代号 I/O 功能说明

1 SRON O 进给驱动输出

2 SRDR O 进给驱动输出

3 SFON O 进给驱动输出

4 TFDR O 循迷驱动输出

5 TRON O 循迹驱动输出

6 TRDR O 循迹驱动输出

7 TFON O 循迹驱动输出

8 FFOR O 聚焦驱动输出

9 FRON O 聚焦驱动输出

10 FRDR O 聚伙驱动输出

11 FFON O 聚焦驱动输出

12 VCOO O 模拟EFMPLL振荡电路输出

13 VCOI I 模拟EFMPLL振荡电路输入fLOCK=8.6436M

14 TEST I 测试脚正常接地

15 VSS 数字地

16 TES2 I 测试脚正常接地

17 TES3 I 测试脚正常接地

18 PDO O 模拟EFMPLL充电脉冲输出

19 VPCO O 可变块PLL充电脉冲输出

20 VCKI I 外部VCO(中心频率16.9344M)输入,用来作为可变块时钟

21 AVDD 模拟电源

22 IGEN I 数字伺服放大器中电流源的参考电阻连接端

23 AVSS 模拟地

24 ADIO O A/D变换器输入信号检测脚

25 RFC I REDC低通滤波器电容连接地

26 RFDC I RF输号输出幅度:2.15~5.0V(VDD=AVDD=5.0V

27 TE I 循迹误差信号输入,输入幅度:2.15±5.0V(VDD=AVDD=5.0V)

28 SE I 进给伺服信号输入,幅度:2.5±1.0V

29 FE I 聚焦误差信号输入,幅度:2.5±1.0V

30 VC I 中心电压输入

31 FIFO O 主PLL滤波器输出

32 FILI I 主PLL滤波器输入

33 FCO O 主PLL环充电脉冲输出

34 CLTV I 主PLLVCD控制电压输入

35 AVSS 模拟地

36 RFAC I EFM信号输入

37 BIAS I 不对称电路恒流输入

38 ASYI I 不对称电路电容电压输入

39 ASYO EFM全幅度输出(低电平:VSS高电平:VDD)

40 AVDD 模拟电源

41 VDD 数字电源

42 ASYE I 不对称电路开/关(低:off高:on)

43 PSSL I 音频数据输出模式选择脚 低:串行输出 高:并行输出

44 WDCK O D/A 接口和字时钟f=2Fs工作于48位槽格式

45 LRCK O D/A接口和LR时钟f=Fs(48位槽格式)

46 DA16 O PSSL=1,DA16输出;PSSL=0,48位槽串行数据输出

47 DA15 O PSSL=1,DA15输出;PSSL=0,48位槽格式位时钟输出

48 DA14 O PSSL=1,DA14输出;PSSL=0,64位槽格式数据输出

49 DA13 O PSSL=1,DA13输出;PSSL=0,64位槽格式位时钟输出

50 DA12 O PSSL=1,DA12输出;PSSL=0,64位槽LR时钟输出

51 DA11 O PSSL=1,DA11输出;PSSL=0,GTOP输出

52 DA10 O PSSL=1,DA10输出;PSSS=0,XUGF输出

53 DA09 O PSSL=1,DA09输出;PSSL=0,XPLCK输出

54 DA08 O PSSL=1,DA08输出;PSSL=0,GFS输出

55 DA07 O PSSL=1,DA07输出;PSSL=0,RFCK输出

56 06 O PSSL=1,DA06输出;PSSL=0,C2PO输出

57 05 O PSSL=1,DA05输出;PSS=0,XRAOF输出

58 04 O PSSL=1,DA04输出;PSSL=0,MNT3输出

59 03 O PSSL=1,DA03输出;PSSL=0,MNT2输出

60 02 O PSSL=1,DA02输出;PSSL=0,MNT1输出

61 01 O PSSL=1,DA01输出;PSSL=0,MNTO输出

62 XTAI I 晶振输入,16.9344M或33.8688MHz

63 XTAD I 晶振输出

64 XTSL I 晶振选择脚低电平:16.9344MHz高电平:33.8688MHz(常速状态下)

65 VSS 数字地

66 FSTI I 数字伺服参考时钟输入

67 FSTO O 输出2/3晶振频率(62和63之间)此频率不随可变块变化

68 FSOF O 输出1/4晶振频率此脚不随可变块变化

69 C16M O 16.9344M输出此脚随可变块同步变化(常速状态)

70 MD2 I 数字输出控制(低:off高:on)

71 DOUT O 数字输出

72 EMPH O 唱片去加重模式输出(唱片加重:高电平;唱片未加重:低电平)

73 WFCK O WFCK输出

74 SCOR O 子码同频信号S0或S1被检测到时,输出高电平。

75 SBSQ O 子码P~Q串行输出

76 EXCK I SBSQ读时钟输入

77 SQSO O 子码Q89bit输出,PCM峰值和电平16位数据输出

78 SQCK I SQSO读时钟输入

79 MUTE I 静音开关脚(高电平:静音)

80 SENS O SENS输出到CPU

81 XRST I 系统复位(低电平复位)

82 DIRC I 单轨迹跳跃(VDD电平时禁止)

83 SCLK I SENS串行数据读时钟输入

84 DFSW I DFCT开关脚(高电平:DFCT对抗电路关闭)

85 ATSK I 抗震脚

86 DATA I 来自CPU的串行数据输入

87 XLAT I 来自CPUM的锁脉冲(LATCH)输入

88 CLOK I 来自CPU的串行数据变换时钟

89 COUT O 轨迹数输出

90 VDD 数字电源

91 MIRR O 镜像信号输出

92 DFCT O 缺陷信号输出

93 FOK O 聚焦OK信号输出

94 FSW O 主轴电机输出滤波器开关输出

95 MON O 主轴电机开/关控制输出

96 MDP O 主轴电机伺服控制

97 MDS I 主轴电机伺服控制

98 LOCK O GFS被以460Hz采样;GFS高电平时,本脚输出高电平。

99 SSTP I 光盘内圈轨迹检测信号输入

100 SFDR O 进给伺服输出