在野外工程测量及控制应用系统中,往往由于交流供电的困难或其它种种原因,使得单片机应用系统(也包括一般电路系统)不得不使用干电池或蓄电瓶供电,因而应用系统的低功耗设计问题就变得十分突出。如何设计一个低功耗的应用系统?多大功耗才算低?很难提出准确的硬指标来衡量,因为硬件系统规模有大有小,界线比较模糊,不能一概而论。但是有经验的系统设计工程师根据你的设计方案就能得出结论,你的设计方案是否合理,是否属于低功耗系统,能否进一步降低功耗等等。如何设计?依据什么原则?这些问题对于初涉系统设计的人员是很难处理好的。即使是有经验的系统工程师也得仔细斟酌。下面根据本人在实际工作中的体会,谈谈单片机应用系统的低功耗设计应该注意的问题及一些设计技巧。

一、单片机应用系统低功耗设计的一般考虑

单片机应用系统的低功耗设计一般应考虑以下几点:

1.尽可能简化电路系统的设计方案。在保证系统主要功能的前提下,删除一些可要可不要的功能,以保证电路最简,降低功耗。例如,在现场人机对话功能不是必须时,可将键盘、显示电路删除,利用串行接口和微机来实现数据交换。这样既可降低功耗,又可方便实现远程控制。又如现场打印机一般不应设计成实时打印方式,而设计成定时打印或可控打印方式,避免打印机常开而增大功耗。

2.尽可能选用低功耗元器件,既保证实现系统功能又可使功耗最小。相同功能的集成电路芯片,CMOS型的就要比TTL型的功耗低得多,例如一片2764程序存储器芯片,其工作电流约为100mA,而一片同样功能的27C64芯片,其工作电流仅为30mA左右。又如当系统必须加显示电路时,选择LCD液晶显示器要比LED显示器功耗低得多。

3.尽可能选用集成度较高的大规模集成电路芯片。因为CMOS集成电路的芯片大规模的与中规模的功耗没有太大差别,而大规模集成芯片比中规模集成芯片的功能要强得多。例如,EPROM芯片27C64(8k字节存储单元)、27C256(32k字节存储单元)其工作电流都在30mA左右,静态电流都在1mA左右。如果选用4片27C64来代替一片27C256显然是不合理的。同样静态数据存储器的选取、一些接口芯片的选取也应尽可能遵循这一原则。

4.在满足系统工作速度前提下尽可能降低系统时钟频率,这也是降低系统功耗的有效方法之一。因为在任何电路中总是存在着一定的分布电容以及晶体管PN结的结电容,工作频率越高,电容充放电的速度就越快,电流就越大,因而功耗就越大。例如,某数据采集系统在11MHz时钟频率时工作电流为200mA,在6MHz时工作电流仅为170mA。

5.充分利用大规模集成电路芯片的低功耗工作方式来降低功耗。现行市场上许多大规模集成电路芯片都设计有低功耗工作方式,例如80C31单片机在11MHz时钟下5V供电时,正常运行功耗为十多毫安,待机方式功耗为几毫安,而掉电方式下仅为十几微安,可见其功耗差别是很大的。又如有些A/D转换器件设计有休眠方式,如20位模数转换器A/D7703工作时的电源功耗为25mW,而休眠时静态功耗仅10μW。

利用软件设计技巧也能使系统功耗进一步降低。利用软件设计技巧降低功耗所遵循的基本原则是尽量减少单片机的工作时间,使单片机有更多的时间处在低功耗状态。因此应充分优化系统监控软件,如少用或不用软件循环来实现延时,采用中断方式而不用循环扫描方式查寻键盘信号,数码显示器采用静态方式而不用动态扫描方式等等,尽可能减少单片机的工作时间,使其有更多的时间处在低功耗的待机状态或掉电状态,这些措施都有利于降低系统功耗。

二、设计技巧

下面举例说明单片机应用系统低功耗的设计技巧。

1.将80C31设计为待机方式

80C31单片机的待机方式是靠一条指令来激活的,当CPU执行完一条把寄存器PCON.0置1的指令(MOV PCON,#01H)后,单片机即进入待机状态,此后提供给CPU的内部时钟信号被切断,但时钟信号仍提供给中断逻辑、定时器和串行口,CPU的全部状态(包括堆栈指针SP、程序状态字PSW、累加器A及所有的工作寄存器)在等待期间都被保留起来。当CPU退出待机方式时,即可自动恢复现场,继续原来的工作。

单片机退出待机状态有两种方法,即中断方法和复位方法。

所谓中断方法是指当外部中断源激活任何一个被允许的中断时,寄存器PCON.0位将被硬件清除,使CPU结束待机状态,转而进入中断服务程序。中断服务完毕,即执行一条RETI指令之后,下一条要执行的指令将是使单片机进入待机方式指令后面的一条指令。

终止待机状态的另一个方法是靠硬件复位,复位信号加在80C31单片机的RESET端。

显然,无论是复位信号还是中断信号,都是依靠单片机外部电路提供的,要设计一个合理的低功耗系统,还要根据系统的任务及信号的性质来决定电路方案。

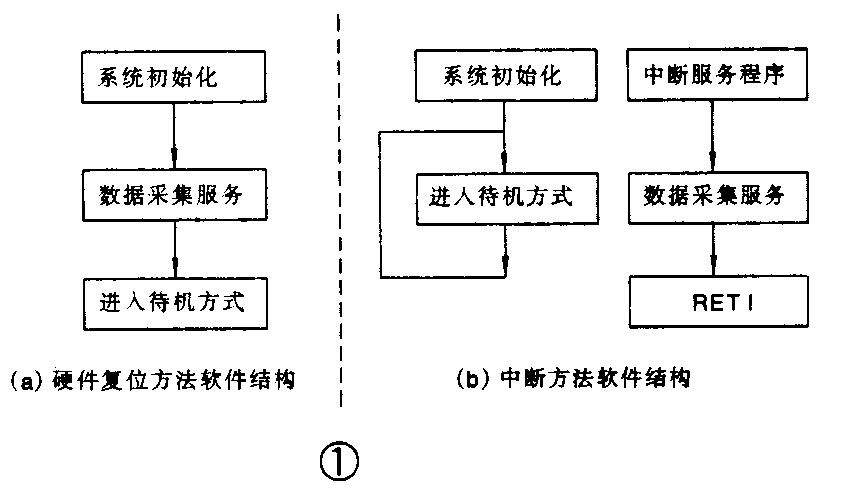

例如,某个单片机系统执行现场数据采集任务,每隔一小时采集一次。显然单片机一小时采集一次数据所需时间是非常短暂的,大量时间不是在工作,而是处于循环等待之中。根据这一特征,我们可以在外部特设一个硬时钟(如MC146818),时钟的整点信号脉冲与单片机的某个中断输入线连接(或与复位线连接,但复位脉冲宽度必须大于两个机器周期)。在监控软件设计时,单片机每结束一次采数周期后,紧跟着执行一条MOV PCON,#01H指令,使单片机进入待机状态,直到下一个中断信号或复位信号来激活,单片机重复下一个采数周期。工作过程如图1所示。其中(a)为以复位方式退出低功耗状态的软件结构,(b)为以中断方式退出低功耗状态的软件结构。

2.光耦电路的灵活设计

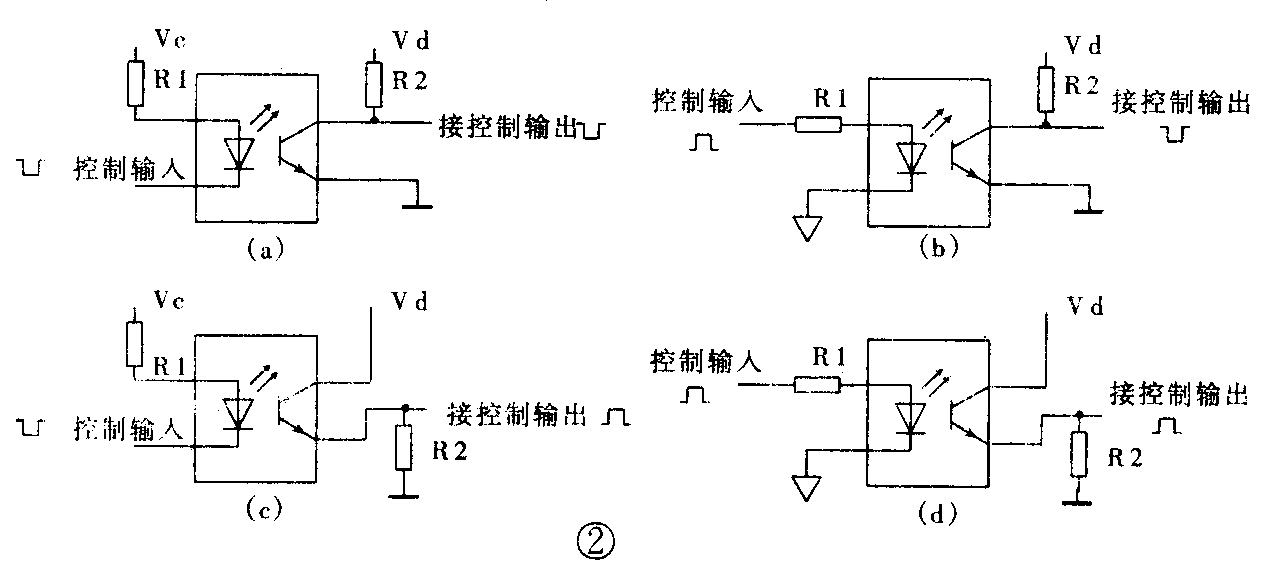

在有些电路系统设计中,为避免主机与现场的电磁联系,提高系统可靠性,须接入光电耦合器件来实现信号的连接,而光电耦合器件一般功耗相对较大。一个普通光电耦合器件其工作电流差不多都在20mA左右,高速光电耦合器件的工作电流更大。因此降低功耗的唯一办法就是尽可能使该器件工作时间短些,而大部分时间处在截止状态,这就要求光耦器件的连接必须合理。下面介绍光耦电路的几种常见接法:

从原理上讲,图2的四个电路都是可行的,当输入有效时输出端都能够产生有效的控制脉冲去控制某个装置的动作,如控制继电器开关的通与断,控制马达的开与关。但是从功耗角度讲,对于有特定时序要求的系统,其差别是很大的。例如要求系统每隔一小时产生一个宽度为1ms的正脉冲,我们希望光电器件仅在1ms时间是工作的,而其余时间都是截止的。显然选择(c)、(d)都是合理的。如果选择(a)、(b)结构,虽然也能达到目的,但势必使光电器件在绝大部分时间处于动态工作状态,对降低功耗是不利的。

3.对不同类型电路分别供电以降低系统功耗

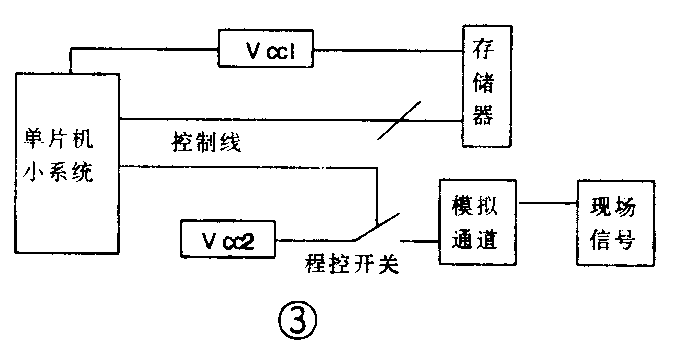

某些系统中,一部分电路动态工作频度高或频繁切换而另一部分电路工作时间很短,其大部分时间都处于静态。此时可以对其分开供电,将工作频度高或频繁切换的电路(例如80C31小系统)用一组电源供电,而将另一些不常工作的电路(例如数据采集器的模拟通道)单独设置一组电源供电,这组电源可受单片机控制,仅在工作时才由单片机提前打开程控开关进行供电,其余时间均切断电源,保证系统功耗最小。其结构框图如图3所示。

4.其它措施

在具体设计时,考虑到某些细节也有利于降低系统功耗,例如对CMOS芯片的所有不用的输入端引脚不能空置,而应接地或上拉至电源。这不仅可避免因电路处于动态而增大功耗,而且可提高系统工作的可靠性。又如对大容量存储空间可分成两部分来设计,一部分为经常使用的数据缓冲器,用于存放CPU经常读/写的数据;另一部分用于保存数据,这部分存储空间CPU很少作读/写操作,大部分时间处于静态,因而可降低功耗。(周振安)