VCD是最近兴起的视听新产品,它采用先进的数字信号处理技术,提供给用户超级的视听享受。在VCD中,绝大部分采用美国C-Cube公司生产的CL480解码芯片。

对VCD激光唱头及CD-DSP部分已有文章作了专门介绍,本文主要介绍以CL480芯片为核心的MPEG解码及视频处理部分的功能电路。

1.VCD整机简介

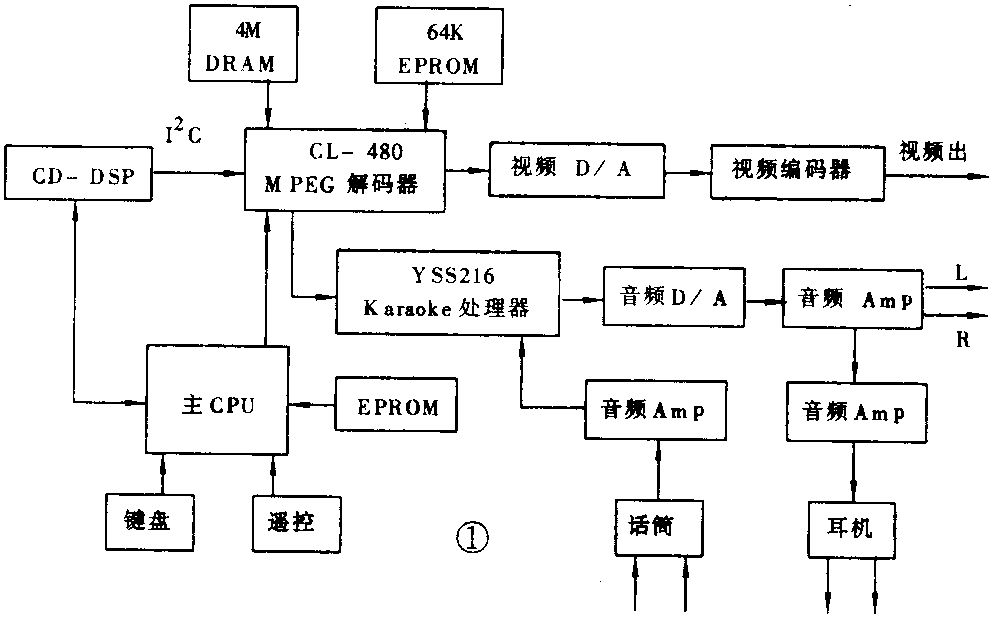

一个较为完整的VCD整机框图如图1所示。由图中可以看出:CD-DSP输出的信号经I\(^{2}\)C总线传送给解压缩芯片CL480。 I2C总线包含5路信号线;左右声道时钟信号、位时钟信号、数据信号、错误信号和地线。其中数据信号线提供串行的视/音频MPEG压缩数据流。

CL480接收从CD-DSP输出的串行压缩数据,进行MPEF-1系统解码和视/音频解码,输出解压缩的数字视频信号和音频信号。

解压以后的信号中,有关视频图像部分的数字视频信号先经过D/A转换器,把全数字RGB转换为模拟RGB信号,再输入视频编码器变换为复合视频信号,最后输出送到电视机。

解压缩信号中的数字音频信号送到YSS216中进行处理,经数字混响、回声、变调等处理后输出模拟音频信号,可送入音频放大器或电视机的音频接口。

2.MPEF-1解码器

VCD的核心就是MPEG-1解码器,它重建被压缩的视/音频数据,提供高质量的图像、声音进行播放。大部分VCD采用美国C-Cube公司的CL480 MPEG-1解码芯片,它集系统解码、视/音频解码为一体,是目前公认的解码能力很强的芯片。

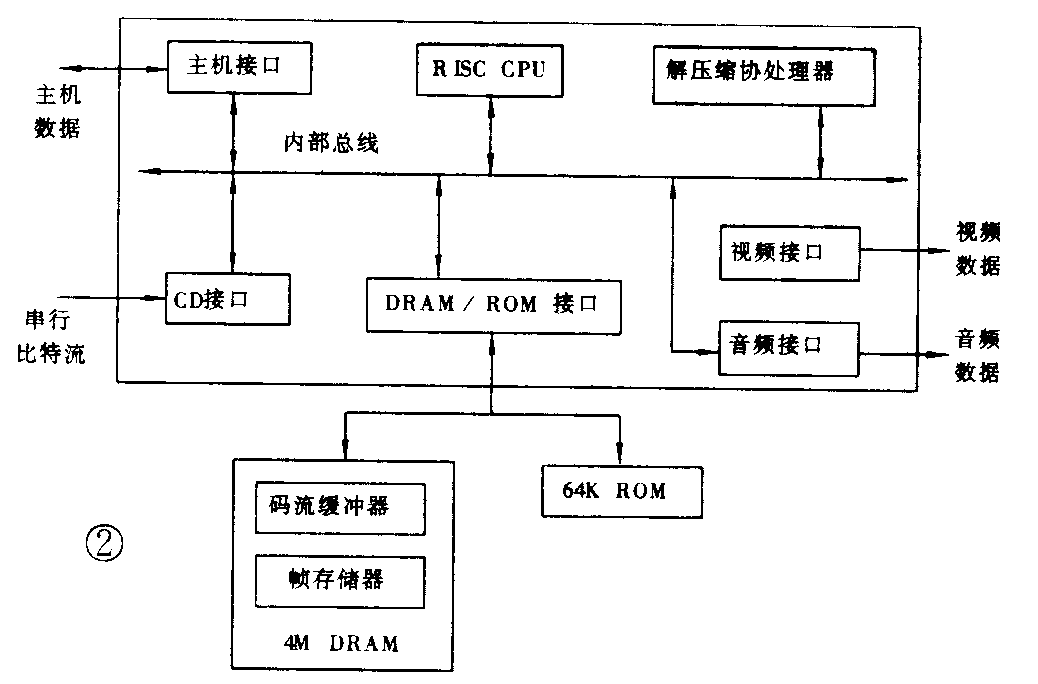

CL480解码器的内部组成框图如图2所示。CL480有五个外部接口:主机接口、CD接口、DRAM/ROM接口、视频接口和音频接口。

主机接口直接与8-bit微处理器相连,用于CL480与 CPU之间的通信。

DRAM接口直接与80ns快速页模式DRAM连接,一般系统采用一片256×16DRAM。DRAM阵列用于存储:压缩的视/音频数据(待解码),正在播放的已解码的音频和视频帧,已解码的上/下参考帧,CL480微码,比特流头参数,FIFO指令。

CD接口用于接收从CD-DSP输出的串行压缩数据。CL480可接收的数据有CDDA、CD-ROM、CD-ROM/XA、CD-I、MDEG系统码流及MDEG视频/音频码流。CL480以搜索扇区标记来选择操作模式,如果什么也没找到,则自动切换到CD-DA模式。

视频接口输出解压缩后的数字视频信号。它从DRAM接收数据,以24/15bit RGB模式,或16-bit Y Cb Cr模式,或8-bit Y Cb Cr模式输出。在 Y Cb Cr模式时Y:Cb:Cr为4:2:2。

音频接口输出解压缩的音频PCM采样信号,它可编程设定,可适用于任何通用音频DAC。

压缩的视/音频数据通过CD接口送入CL480内部的FIFO缓存,DRAM接口从FIFO中取出数据写入码流缓冲器。码流缓冲器像一个很大的FIFO,当解压缩过程处理的数据在一较宽范围变化时,它能允许CD以一相对恒定的速率提供数据。解码器自动控制缓存器的满溢。

中央处理单元和协处理器从码流缓冲器得到压缩数据,完成解码过程,并将解码后的数据写入DRAM。协处理器进行例如Huffman解码等解压缩算法操作,中央处理器在解码过程中实现控制作用。解码后的像素经彩色空间变换器进行变换,最后通过视频接口数据总线输出。

CL480通过执行微码(C-Cube提供)完成解压缩过程。微码存储于DRAM中,当需要时装入片内存储器。从主机直接接收,并在CL480的CPU上进行微码操作的方法叫微码指令,它们是主CPU写入DRAM的功能码和参数值。

3.解码器接口

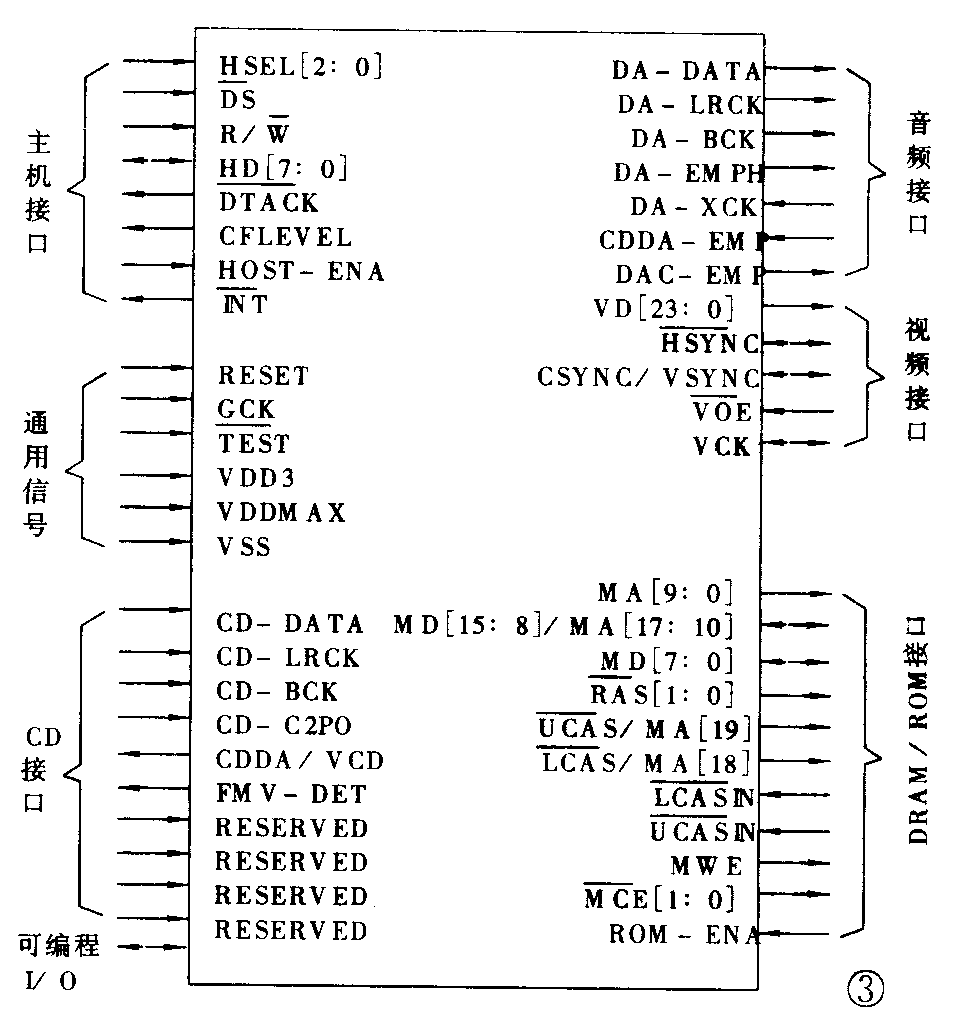

VCD的解码器是以CL480为核心组成,现把它的接口(见图3)作些介绍,供看图时参考。

CL480的通用信号线包括:电源线VDD3、VDDMAX可以接5V电源;地线VSS;硬件复位线RESET与主CPU端口连接;通用时钟线GCK接40/40.5MHz的晶振;测试线TEST。

CL480的DRAM接口信号线包括:地址总线MA[9:0]为DRAM、ROM复用地址线;数据总线MD[15:0],其中MD[7:0]为ROM数据线,MD[13:8]为ROM高位地址线,行地址选通线RAS-[1:0]用于两片DRAM时,与DRAM的RAS线连接;高低端列地址选通线UCAS-、LCAS-与 DRAM的LCAS-、UCAS-分别相连;UCASIN、LCASIN-为高低端数据锁存线;写允许线MWE-与DRAM的W-相连; MCE-为ROM片选线与CE-相连;ROM-ENA为高电平时, CL480采用 ROM中bank0的数据进行初始化。

CL480的主机接口信号线包括:主机地址线HSEL[2:0],它们与CPU的端口连接;CPU数据线HD[7:0],它们与CPU的PI口连接;数据选通信号线DS-,与CPU端口相连; CPU数据请求线DTACK-、读写线R/W-,与CPU端口相连;中断请求信号线INT-与CPU中断管脚连接; HOST-ENA为主机允许信号线。

CL480的CD接口信号线包括:CD-BCK bit时钟线; CD-DATA串行数据线;CD-LRCK左/右声道时钟线;CDDA/VCD允许信号线;用于接收CD-ROM数据的信号线CD-C2P0。它们与CD-DSP输出信号线相连。

CL480的视频接口信号线包括:像素数据总线VD[23:0],其中VD[7:0]为R信号线,VD[15:8]为G信号线,VD[23:16]为B信号线,它们输出到视频A/D变换器;场同步信号VSYNC-与行同步信号HSYNC-,与视频编码器相连接;视频输出允许信号线VOE;视频时钟线VCK与视频解码器相连。

CL480的音频接口信号线包括:串行数据线DA-DATA;比特时钟线DA-BCK;左右声道时钟信号DA-LRCK;外部音频时钟DA-XCK。它们与卡拉OK电路相连接。

对于视频处理部分,视频D/ A转换器可采用CXD1178,它是用于视频带宽内的8-bit高速D/A转换器,分为RGB三个通道,可把8-bit全数字RGB信号转换为模拟RGB信号。它的输入端R[0:7]、B[7:0]、G[7:0]分别与CL480的VE[23:0]连接。输出R/0/R0、G/0/G0、B/0/B0到模拟视频编码器。其RCK、GCK、BCK与VCK相连接。

模拟视频编码器可采用CXA1645芯片。从CXD1178输出的模拟RGB输入到RIN、GIN、BIN引脚;SCIN连接视频副载波4.43MHz晶振;从CL480输出的场同步信号VSYNC-输入SYCIN引脚;CXA1645由Cvout输出混合视频信号到电视机。 (关池)