CD4518是一片CMOS双二——十进制加计数器。所谓“二——十进制”是指用二进制数来代表十进制数;“双”的意思是一个芯片上集成了两个相同的计数器(电源共用)。

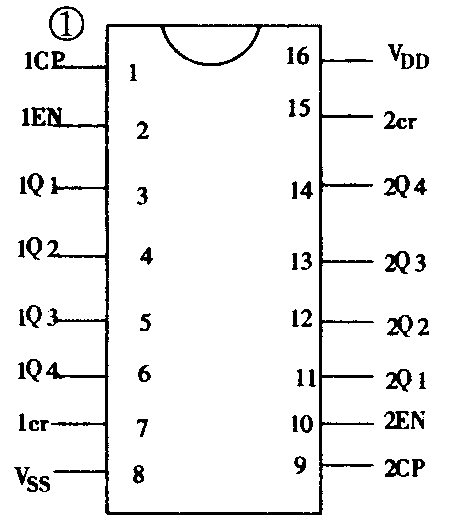

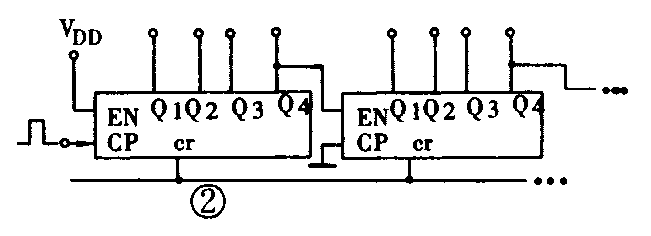

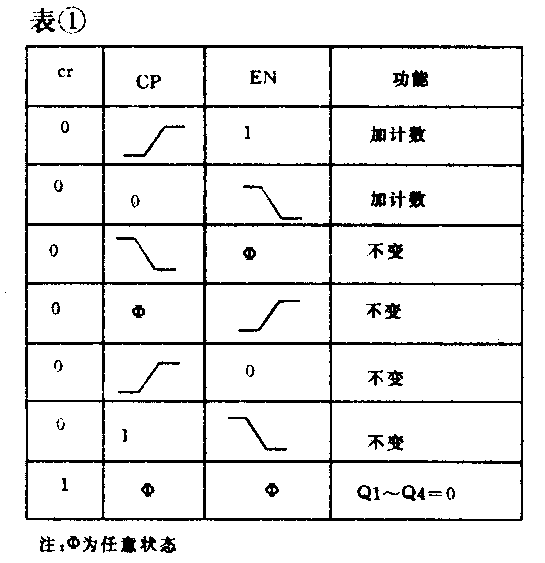

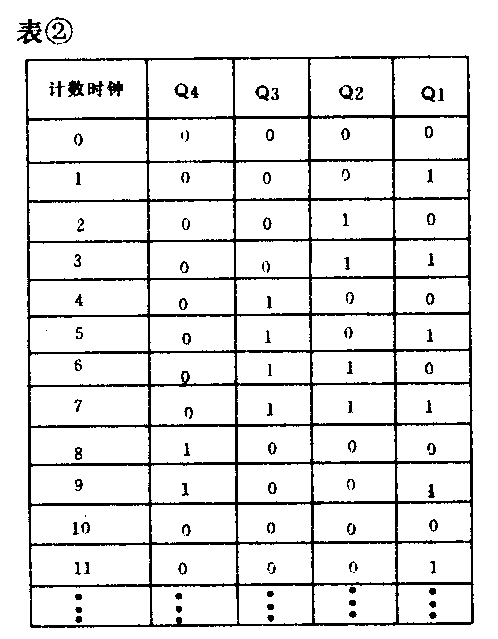

CD4518引脚排列如图1所示。它有两个时钟输入端CP和EN:如果要用时钟的上升沿触发计数,则信号由CP端输入,并使EN端接高电平;如果要用时钟的下降沿触发计数,则信号由EN端输入,并使CP端保持为低电平。Q1~Q4是4位二进制输出端,Q1是最低位,Q4是最高位。cr是清零端,当在cr端加高电平或正脉冲时,Q1~Q4全部为0。CD4518的输入输出关系如表1所示。做加计数时,Q1~Q4从状态0000至1001(相当于十进制的0~9)变化并循环,显然,由1001变为0000时Q4由高变低,产生一个下降沿脉冲,所以Q4可做为多级计数器级联时的上一级输出,因为是下降沿有效,所以Q4应接至下一级的EN端。图2是CD4518级联时的电路。仿此电路可组成多级计数电路。表2是计数器状态变化表(假定初始状态为0000)。需要说明的是,图2中每一级计数器代表一位10进制的数字,左边是最低位,右边是最高位,在一般的应用中,还应增加译码显示电路,此时要正确安排显示数码管的位置,使左边为最高位,右边为最低位,以便与我们通常使用数字的习惯相同。有关译码、显示部分的原理,我们将另文介绍,并希望读者将计数、译码、显示部分结合在一起阅读。(李洪明)