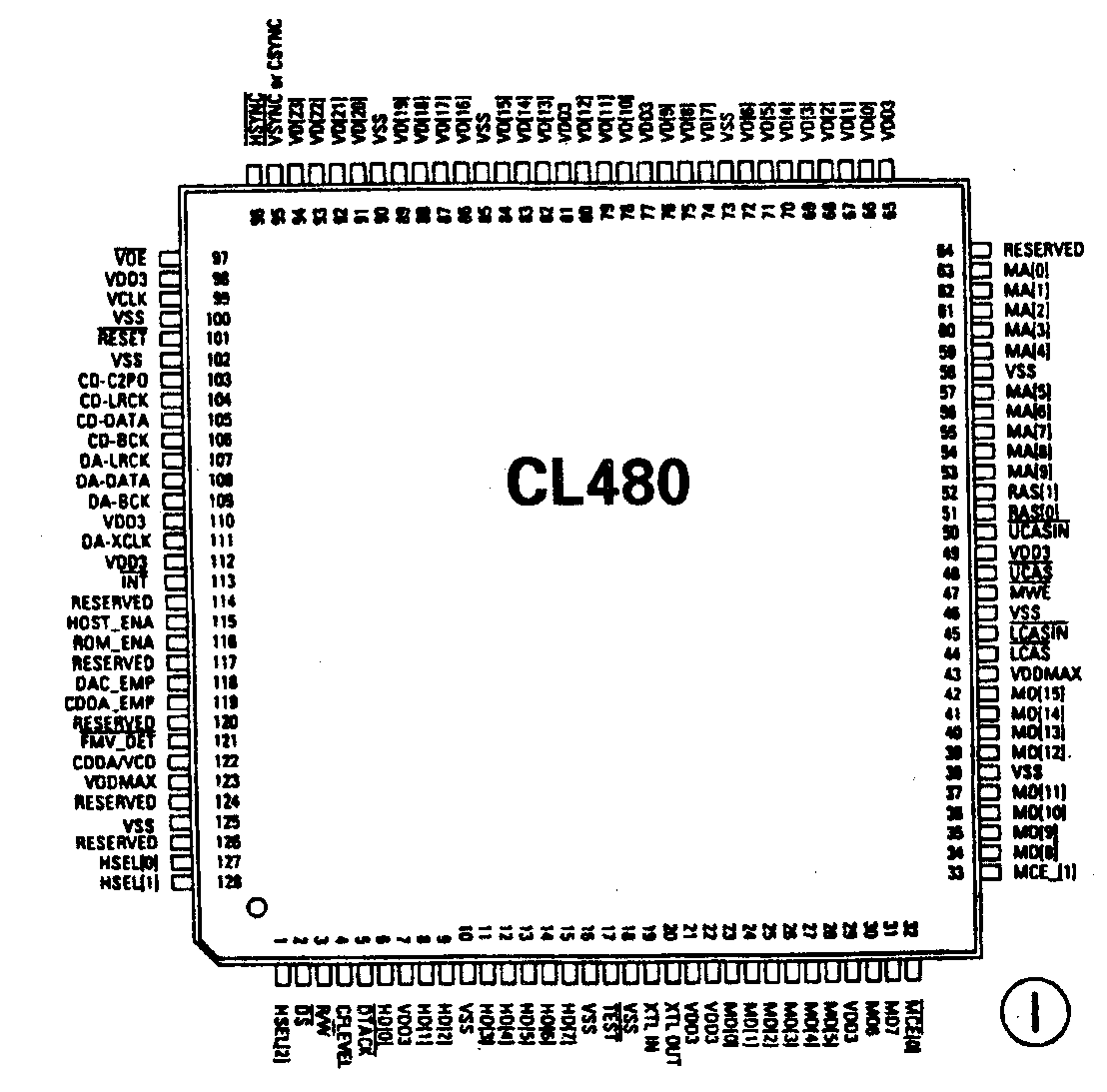

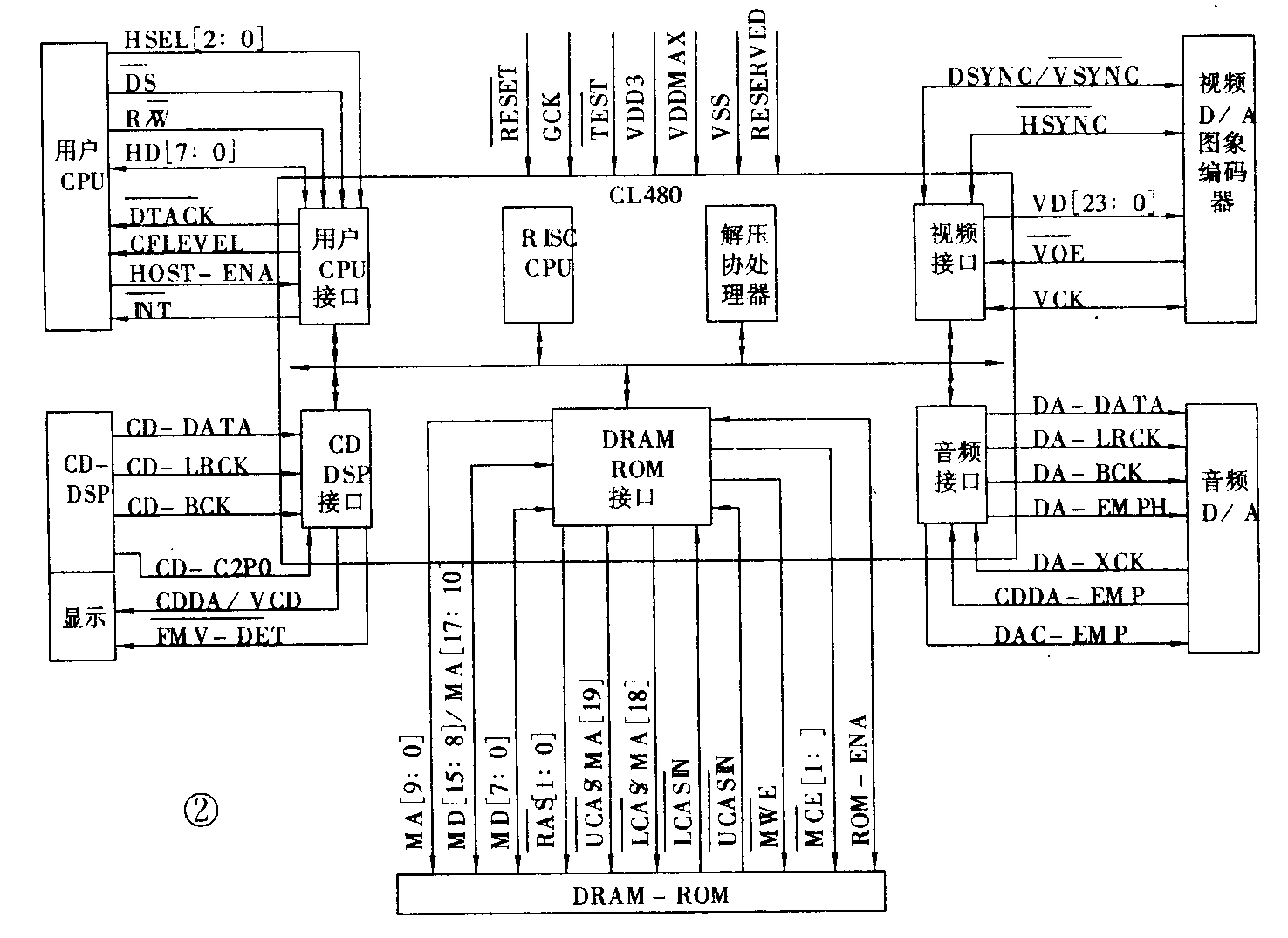

CL-480是一个具有128脚的大规模集成电路,其主要功能是将以MPEG-1标准压缩编码的CD格式和CD-ROM格式的复合数码信号解压处理成音频数码信号和视频数码信号,以便经音频和视频D/A还原为模拟的音频和视频信号,以CL-480为核心构成的MPEG-1解压板主要用于VCD小影碟播放机和多媒体个人电脑,作为音频和视频解压缩处理器,CL-480的引脚图见图1。为便於理解和应用,图2给出了其内部原理框图以及其与相应外围电路的连接示意图,供读者参考。

下面就以图2为线索,按分属不同口逐个介绍其引脚功能。

1.HSEL[2:0]—用户CPU地址总线,输入端,这三根地址线用以选择CL-480内部五个用户CPU接口寄存器。

DS-—数据选通脉冲,输入端。用户CPU通过DS-通知CL-480进行读或写操作,DS-为下降沿有效。

HD[7:0]—用户CPU数据总线,双向传输,用户CPU通过HD[7:0]这8位数据线实现与CL-408数据交换,其传输方向由R/W-信号确定。

R/W-—用户CPU对CL-480读写标志信号,为输入端,高电平时用户CPU对CL-480的用户CPU数据总线执行读操作,低电平时执行写操作。

DTACK-—CL-480准备好与用户CPU进行数据交换的标志信号,为输出端。用户CPU在对CL-480执行读或写操作期间,CL-480维持该信号低电平。当CL-480响应读请求时,DTACK变为高电平,直到数据准备好后才变为低电平,当CL-480响应写请求时,DTACK-维持低电平,直到数据接收完毕并被锁定为止。DTACK-要求1.5kΩ的上拉电阻。

CFLEVEL—已编码的数据FIFO(先进先出寄存器)状态标志,为输出端。当CFLEVEL为低电平时,表明CL-480中的FIFO已为压缩数据让出至少44bytes的空位。该端子要求1.5kΩ的上拉电阻。

INT-—CL-480对用户CPU中断请求信号,为输出端,中断过程由“置中断标志”寄存器中的宏指令命令确定,该端子也要求1.5kΩ的上拉电阻。

HSOT-ENA—用户CPU接口的使能端子,为输入端,当该端子为高电平时,用户CPU接口所有端子执行正常的功能,当为低电平时.CL-480不需外接用户CPU,用户CPU接口的端子可以用作其它控制端子。

2.与CD的数字信号处理器DSP接口部分

CD-BCK—位时钟,为输入端,CL-480可以接收6种比特率的BCK信号。

CD-DATA—由CD-DSP来的串行数据,输入端。

CD-LRCK—左右分离时钟,输入端,CL-480通过编程,可以接收不同极性的LRCK(左右声道哪个是高电平)。

CD-C2P0这是错误标志位,CD-ROM格式数据时使用,当发生错误时,会变为高电平,为输入端,CD-DA格式时无用。

CD-DA/VCD—CD和VCD识别指示端,输出端,进来的数据流是CD-DA时输出高电平,是VCD时输出低电平。

FMV-DET-—FMV检测,输出端,这是CD-1数据格式指示端,当FMV标志被检出到时,该引脚输出低电平。

3.与DRAM接口部分

MA[9:0]—10位存储器地址总线,输出端。CL-480重复使用这些地址总线作行和列地址,最多可以寻址至1Mbytes,DRAM,这10位地址线亦用于ROM的寻址。

MD[15:0]—16位存储器数据总线,为双向传输,这16位数据线用于CL-480与外接DRAM/ROM之间的数据传输,当与DRAM交换数据时,全部16位均作数据线;当与ROM交换时,MD[7:0]8位用作ROM数据线,MD[15:8]8位作ROM高位地址MA[17:10]。

RAS-[1:0]—行地址选通,为输出端,CL-480通过这2位信号将行地址锁进DRAM区,RAS-1锁定1区,RAS-0锁定0区。

UCAS-,LCAS-—高、低位列地址选通,输出端,CL-480通过这2位信号将列地址锁进DRAM区,UCAS-锁定高8位MD[15:8],LCAS-锁定低8位MD[7:0]。

UCASIN-,LCASIN-高、低位数据门闩使能,输入端,当CL-480从DRAM中读数据时,MD[15:0]中的数据将在CASIN-的上升沿被锁进CL-480内,UCASIN-锁定高8位,LCASSIN-而锁定低8位。通常该二引脚都接到UCAS-和LCAS-上。

MWE-—写使能,输出端,在CL-480将数据写进DRAM期间,MWE将维持低电平,在读DRAM期间,将维持高电平。

MCE-[1:0]—片选使能。输出端,当CL-480在读ROM期间,这2位信号将维持低电平。

ROM-ENA—自引导ROM初始化使能,输入端,当该引脚为高电平时,CL-480将自动从ROM中0区读出数据自行初始化。

4.视频接口部分。

VD[23:0]—像素数据总线,共24位,输出端,CL-48O用这些信号线传送像素数据到视频子系统,这些信号线的定义不同于RGB和YCbCr。

HSYNC-—水平同步,为双向传输。CL-480在HSYNC-的上升沿之后第一个HSYNC-时输出一行水平像素数据。HSYNC-必须与VCK同步。

VSYNC-—垂直同步,双向传输,CL-480在VSYNC-的上升沿之后第一个HSYNC-时输出一帧新图像的顶部边界。VSYNC-可以与VCK不同步。

VOE-—视频输出使能端,输入,VOE-必须维持低电平CL-480才能驱动像素总线VD[23:0],当VOE-为高电平时像素总线将变为高阻态。

VCK—视频时钟。双向,VCK由GCK导出,但不必要与GCK同步。

5.与音频接口部分,

DA-DM—解压后串行音频数据,输出端。

DA-LRCK—左右分离时钟,为输出端。

DA-BCK—位时钟,输出端,为串行输出的基准时钟,它由DA-XCK 8分频而来,可以是取样频率的32或48倍。

DAC-EMP—输出信号加重标志,输出端。在CD-DA直通格式时,该信号被送到音频DAC作标志。

DA-XCK—外接音频时钟,输入端,用以产生DA-BCK和DA-LRCK,DA-XCK可以是取样频率的256或384倍(11.2896MHz或16.9344MHz)。

CDDA-EMP—输入加重标志,输入端。在CD-DA直通格式时,该输入端直接连到DAC-EMP输出端。

此外, CL-480还有整体性的引脚,如RESET-GCK,TEST-以及电源等。(陈海波)