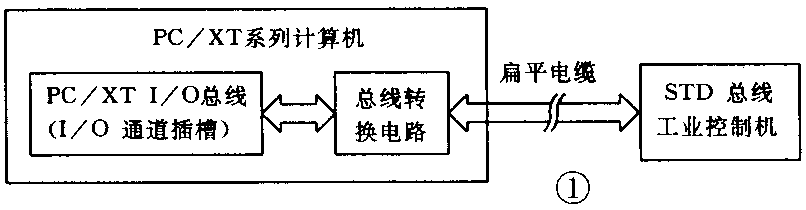

IBM-PC/XT系列计算机有丰富的系统软件和应用软件。当前流行的STD总线工业控制机结构紧凑,抗干扰性能好,但是PC/XT系列计算机的I/O总线结构和 STD总线结构不同,不能把 PC/XT系列计算机直接连接于STD总线的工业控制机。使用PC/XT I/O总线与 STD总线转换电路后,利用PC/ XT系列计算机既可作STD总线工业控制机的开发工具,又可取代STD总线CPU板,直接管理STD总线工业控制机进行现场自控。如图1所示。在图1系统中,可以使用编译代码短、运行速度快、移植性强、操作方便的TURBO C和TUBRO PASCAL等语言编写控制程序,也能使用大家熟悉的BASIC语言和8088汇编语言。

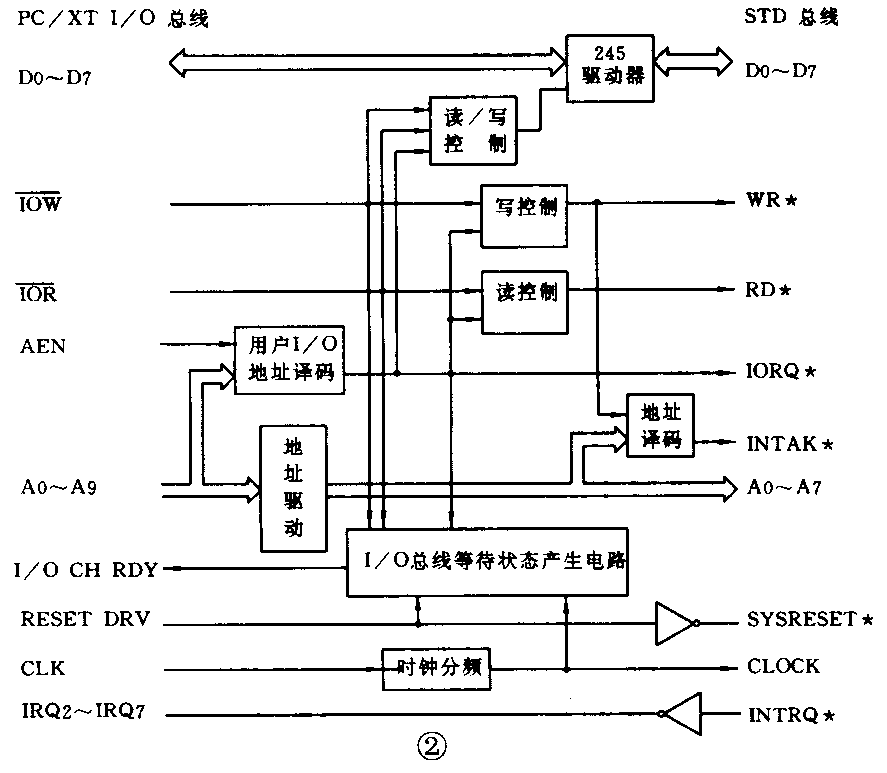

PC/XT系列计算机8位数据I/O总线主要由时种信号CLK、复位信号RESET DRV、地址信号A0~A9、数据信号D0~D7、I/O读信号IOR、写信号IOW、中断请求信号IRQ2~IRQ7、通道准备好信号I/O CH RDY等组成。 STD总线除需要把上述部分信号映射过来外,还需要I/O地址选择信号IORQ\(^{*}\)、中断确认信号INTAK*等。有了这些信号以后,就可以对STD总线工业控制机进行基本的操作了。总线转换电路原理如图2所示。

PC/XT的低256个I/O地址是留给用户的。图2电路中用户 I/O地址译码输出(IORQ\(^{*}\))有效表示选中I/O地址0~255。把此256个地址中的一个译码得出INTALK*信号,用于PC/ XT计算机响应STD的中断请求后,向STD工业控制机发出中断确认信号。时钟分频的倍数可根据实际需要确定。

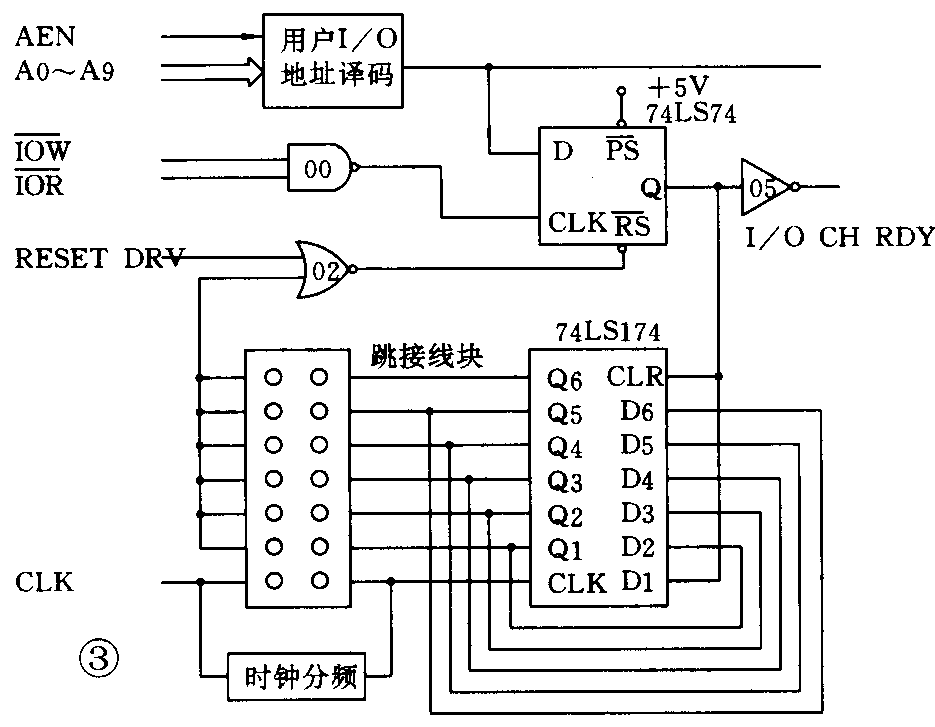

有些I/O设备,如光电耦合器等速度比较慢,这时计算机就要等待这些慢速I/O设备动作的完成。当计算机主频过高时也需要等待I/O动作的完成。I/O总线等待状态电路能实现等待功能。图3给出了PC/ XT计算机在I/ O读写周期中产生 1~ 5个时钟周期(分频后)额外等待状态的电路。用户 I/O地址译码用来确定需要产生多余等待状态的I/O地址范围。IOR或IOW信号的下降沿,用于对译码器的输出进行采样,并将74LS74锁存器置位。锁存器置位使I/O CH RDY起作用, PC/ XT计算机 CPU进入等待状态。74LS174是移位寄存器,用来计数时钟周期,它的输出复位74LS74锁存器之前产生的等待。锁存器 74LS74被清零,I/O CH RDY信号变低,CPU的READY信号被激活,I/O总线周期就结束了。(付兰英 傅成钢)