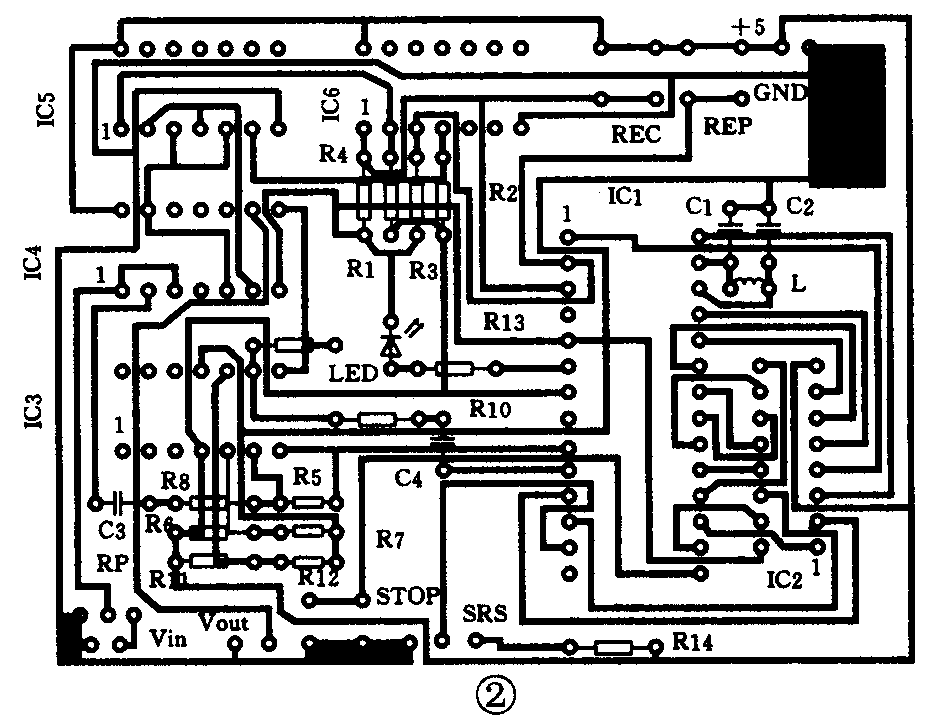

UM93520A是台湾联华公司(UMC)生产的语音处理器,它使用自适应增量调制即ADM方式处理声音数据,录音时将声音信号进行A/D转换变换成数字信号存放在外接存储器DRAM41256中,放音时则从DRAM中取出数据经内部D/A转换器变换成模拟信号输出,其过程可表示为:模拟量输入→数字量存储→模拟量输出。它内置动态RAM刷新电路,存储容量大,存取波形数据电路简单。它能对频率范围为0.1~5.9kHz的语音进行A/D输入和D/A输出,它当然也能对在此频率范围内的其它非语音信号进行A/D和D/A处理。基于这种思想,我们可以在其基础上附加一些其它电子元件构成简易波形存储器。将它安装在普通示波器的输入探头之前,即可使普通示波器具有存储示波器的功能。该装置电路原理图如图1所示。

整个电路由三大部分组成:由UM93520A和DRAM41256构成的波形A/D、D/A部分;由运放LM324A构成的波形输入、输出部分;由CD4011、CD4069及CD4066构成的信号流向切换开关部分。

整个电路接通电源后,并不立即进入A/D转换过程,而是处于守候状态。当按下REC键时,CD4069的1脚为高电平,2脚输出低电平,迫使由CD4011构成的RS触发器的输出状态为Q=1,Q=0,它控制CD4066的IC4:A和IC4:B两个电子模拟开关闭合,IC4:C断开。输入信号在经过IC4:B电子开关送到示波器探头的同时,也经LM324A的IC3:B运放传送到UM93520A的AUD1端即模拟信号输入端。同时UM93520A的REC端(3脚)即录音开始触发端得到高电平触发而启动芯片内的ADM分析电路开始A/D转换,将从AUD1端输入的模拟信号以ADM方式转换成数字信号存储在DRAM41256中。每存入一位数字,存储单元地址计数器自动加1,指向下一个存储单元。当UM93520A中的地址计数器达到DRAM41256的最大地址后,A/D转换过程自动结束,电路又进入守候状态。由于存储容量是固定的,因而启动一次A/D转换所能持续的采样时间由所采用的采样速率来决定。

当按下REP键时,CD4069的3脚为高电平,4脚输出低电平,迫使CD4011构成的RS触发器的输出状态翻转为Q=0,Q-=1,使电子开关IC4:A和IC4:B断开,IC4:C闭合。同时UM93520A的2脚REP端即再生触发信号输入端得到高电平触发而启动D/A转换,将DRAM41256中存储的波形的数字量转换为模拟量从AUDO即模拟信号输出端输出,经运放LM324A的IC3:C和电子开关IC4:C送到示波器显示。

UM93520A的13脚SRS端接一只单刀双掷开关,它控制A/D采样和D/A重放的速率。当SRS端接高电平时,A/D和 D/A的速率为16kbps(BitPerSecond),接低电平时为22kbps。UM93520A只外接一片DRAM41256,其容量为256k位,因而采用16k bps的采样速率进行A/D转换,它可以存储16秒钟以内的波形;采用22kbps则只能存储11秒钟的波形。当然,采样速率越高,重放的波形越接近原输入波形,重放波形时能观察到的细节也就越丰富,这对频率较高的信号比较合适。如果用22kbps的采样速率存储波形,然后用16kbps的速率重放,就可以看到重放出的波形在时间轴上被扩展,从而能方便地观察到波形的一些细节部分。

按下IC115脚上的STOP键可以在任何时候中止UM93520A的存储或重放波形的操作而使电路进入等待状态,但它不改变电路其它部分的原有状态。UM93520A第6脚BUSY端外接LED用于指示UM93520A的当前工作状态。LED点亮表明电路正在进行存储波形或重放波形的工作,否则表明电路正处于守候状态。

CMOS电子开关的输入信号的幅度要求不能超过电源电压,因此当输入信号的幅度较大时,一定要用电位器衰减下来。为减小电子开关的导通电阻值,通过电子开关的输入信号的幅度在3V左右比较适宜。UM93520A的9脚AUDI端要求外接电路的中心电平为1/2Vcc,因此LM324A的5脚必须接到R6、R7构成的分压电路的中心点。R3、R4分别是REP和REC触发端的下拉电阻,保证在无REP或REC 键按下时,UM93520A不会误动作。

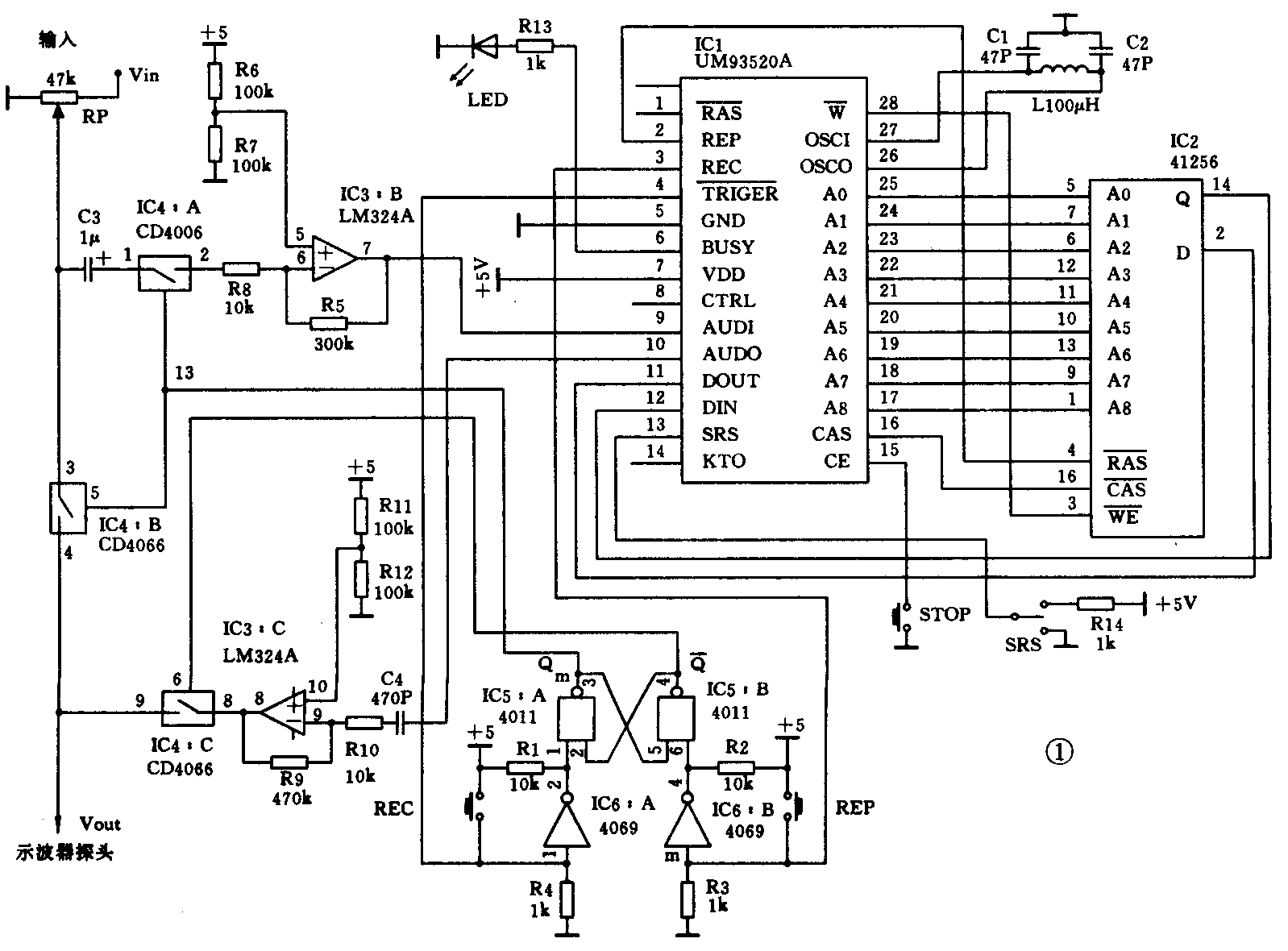

在需要存储某一段时间的波形时,如在观察某个稍纵即逝的波形时,只需按下REC键。按下此键后DRAM中原有的波形数据将被新的波形数据所取代,原有数据不复存在。按REP键可使存入的波形被反复重放输出,通过示波器仔细分析。只要不掉电,所记录的波形信息就不会丢失。由于最高采样速率为22kbps,依据香农采样定理,所能存储的信号的最高频率为10kHz。整个电路的印制版图见图2。(张红兵)