本文向大家介绍用晶体管制作的模拟转折电压单向开关二极管和它的一种特殊用途即降低压敏电阻的残压比。

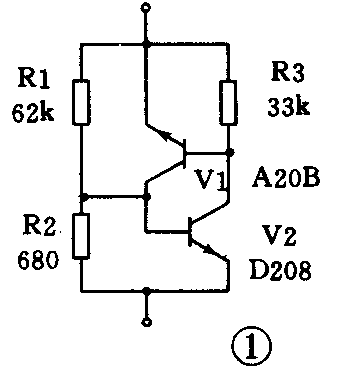

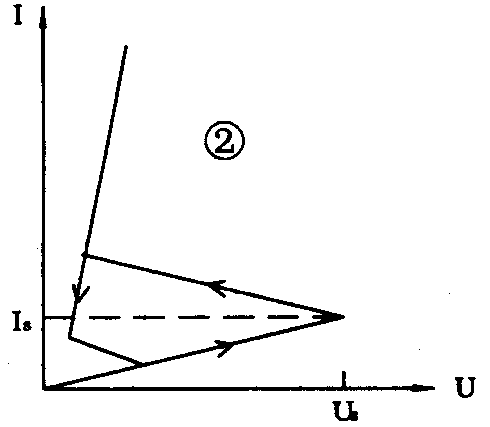

图1是模拟转折电压单向开关二极管(以下简称为FLD)的电路图,图2是它的正向伏安特性曲线。当FLD端电压较低时,V1、V2处于截止状态。若其端电压逐渐升高,R2上的电压降随之升高,至使V2从截止转为导通。并通过V1、V2间的正反馈使电路状态突变为V1、V2饱和导通。改变R2,可以改变导通电流I\(_{s}\),改变R1就可以改变转折电压Us。按图1所示选择元件参数,I\(_{s}\)=0.9mA,Us=52V。

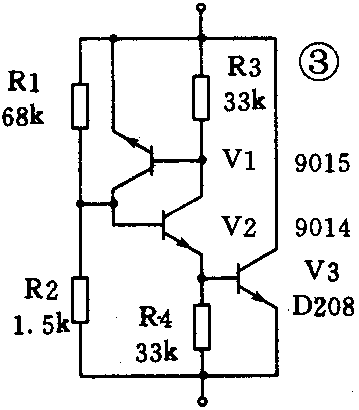

图3是基本电路图1的一种变型电路。图3使用了3只晶体管,V1、V2是小功率管,V3用大功率管,在不易找到图1中的V1大功率晶体管时可选择图3方案。

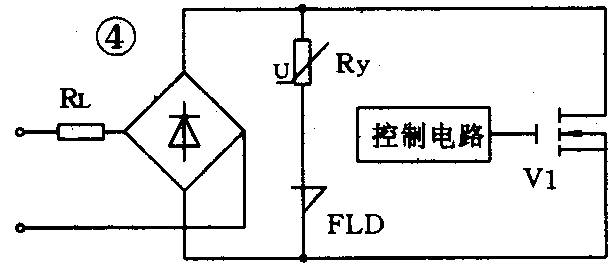

图4是一种实际的模拟FLD应用电路。图4中V1是串接在主回路中的开关元件, V1控制负载R\(_{L}\)的得电情况。当V1从导通突变为截止时,V1两端会激起较高电压。压敏电阻RY和V1并接,吸收尖峰电压,保障电路安全。现选择VMOS管的耐压值为650V(≥650V),考虑到压敏电阻的残压较大,选用压敏电压(U1mA)为430V的压敏电阻做保护元件,此时最高允许工作电压按430×0.8÷1.4计算为245V,未达到设计要求(设计要求最高工作电压为260V)。若选用压敏电压为470V的压敏电阻,则要求相应地提高VMOS管的耐压值。这样不但会增加成本,而且VMOS管的导通电阻也会增大。因此考虑采用压敏电阻串接模拟FLD的方案(如图4所示)。

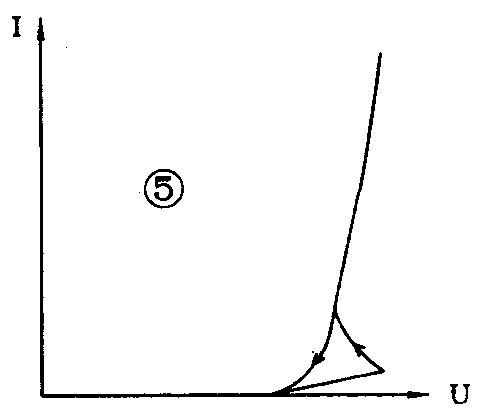

用晶体管图示仪测试压敏电阻串接模拟FLD总伏安特性曲线如图5所示,串联元件的正向特性和反向特性是不一样的。在正向,当串联元件的端电压增加到U\(_{1mA}\)+Us(U\(_{1mA}\)是压敏电阻的压敏电压,Us是模拟FLD的转折电压)时,达到转折点,模拟FLD导通,压敏电阻的端电压急增,支路电流急增,在反向,曲线沿压敏电阻自身的伏安特性曲线下降。当支路电流减小到0.9mA以下时,模拟FLD恢复截止状态。

虽然串联元件的回扫特性未改变,但由于转折电压提高了50V,在此应用中按(430V+50V)×0.8÷1.4≈274V来确定最高允许工作电压,达到了设计要求。

压敏电阻串接模拟FLD使支路允许通过的浪涌电流值下降,在一些特定场合,此项参数下降对应用无碍。(丘双安 )