在有些电路中需要高分辨率的脉冲移相器。脉冲移相的原理就是在一个连续的脉冲序列中插入或减去一个脉冲,使经此处理后的脉冲序列相对于原脉冲序列在相位上超前或滞后360°,如再经过N次分频,则相位的超前或滞后量就会减小N倍。所以若希望在频率为f\(_{0}\)的脉冲序列中得到相位移动分辨率为360°/N,则要在频率为N×f0的脉冲序列中完成插入或减去一个脉冲。下面结合我们实际工作情况,介绍一种在频率为20MHz脉冲中插入半个脉冲或等价于减去半个脉冲的实用电路。

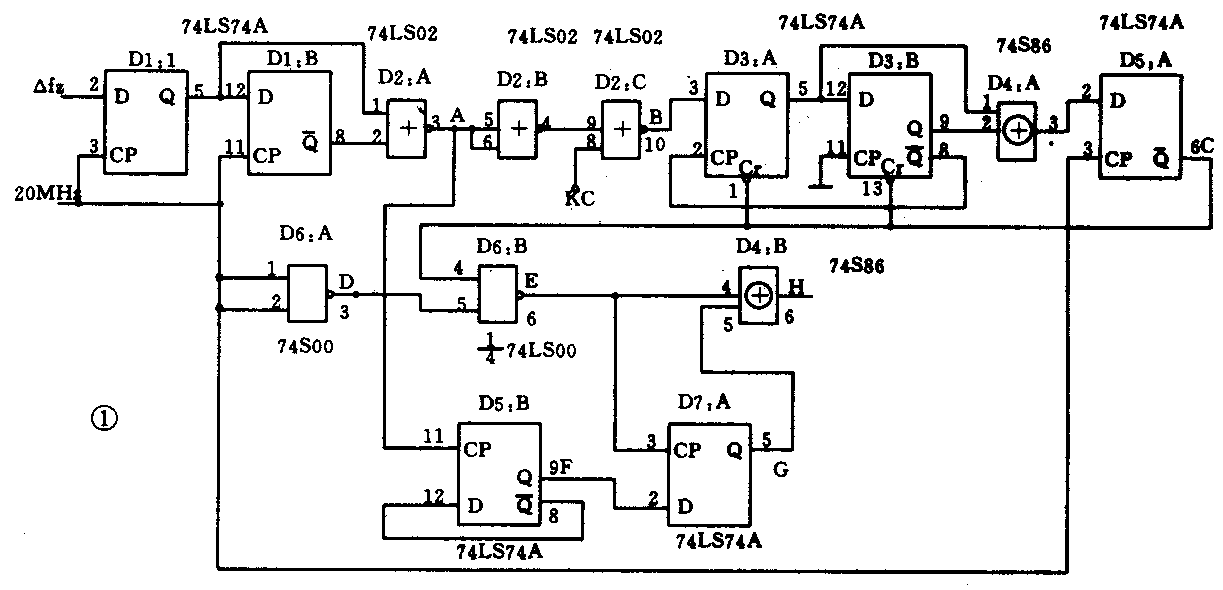

在20MHz脉冲中插半个脉冲不是一件容易的事情,其难点在于20MHz的半个周期为25nS,而74LS系列集成电路的典型延迟为10到15nS,所以在电路中不经过严格的同步和采用一些电路上的技巧是很难实现的。图1给出了移相电路原理图,图2、图3给出了电路各点时序及波形图。

Δfz是同一个20MHz频标分出来待插入脉冲序列(频率<5MHz,脉冲宽度>50nS)。为适应它是任意脉宽,任意频率的特性,所以先经两个D触发器D1:A、D1:B和一个或非门D2:A整形为脉冲宽度为50nS的序列(点A为Δfz整形后的波形)。从A点输出的信号一路经D2:B、D2:C和由D3:A、D3:B、D4:A、D5:A组成的R—S触发器后与20MHz基准频率再次同步,以取得与基准频率的严格时序关系,另一路经二分频电路实现半个脉冲的加或减,但F点的信号必须再经同步电路D7:A和D6:B输出信号(E点)同步,保持严格的相位关系,最后由D4:B的异或门完成整个电路的功能。以上功能的实现在电路中有几个关键点:

1.巧妙的利用了D7:A(74LS74A)触发器约15nS的延迟;

2.利用D4:B高速异或门(74S86)将15nS的延迟检测出来;

3.D3:A、D3:B、D4:A、D5:A的R-S型触发器置位为沿触发,而复位为电平复位,使电路提高了抗干扰能力。

电路中的KC为相位左、右移(加减脉冲)控制逻辑信号,D6:A为反相器,它使C点输出与20MHz基准有特定逻辑关系,在我们实际工作中,将H点的移相(超前或滞后180°)脉冲送到分频电路从而获得高分辨当量脉冲。

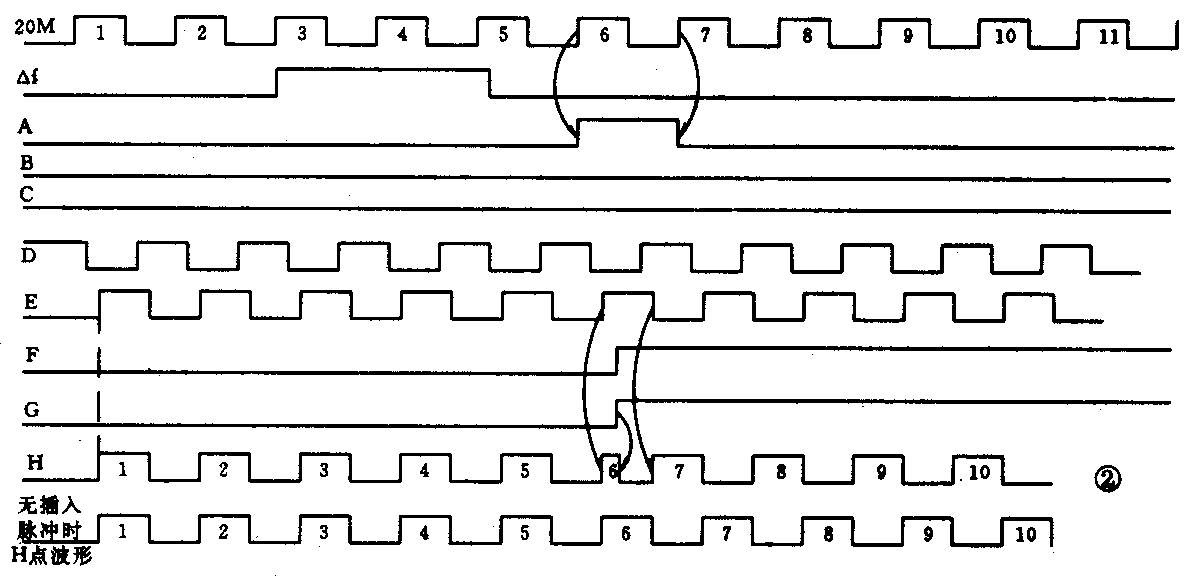

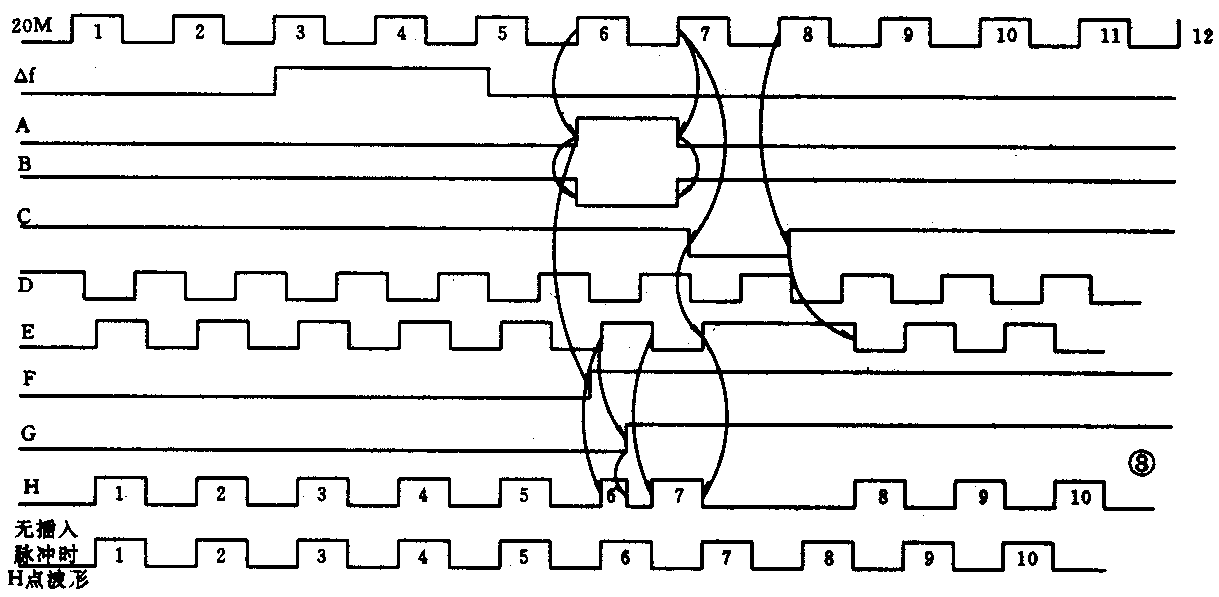

从图2到图3可看出电路中各标注点的波形及相互时序。图2表示在没有插入脉冲时的情形,可以注意到由于各集成电路的延时累积,使H点波形相对基准波形有一点相移(延迟),这在应用中并不重要,因在电路组成固定后相移是确定的。从图2可看出H点信号在第7个脉冲开始相位超前了180°。图3表示了H点波形在第8个脉冲开始相位滞后了180°。( 姚进 吴洪 顾文权)