CD4046是CMOS 微功耗锁相环集成电路。在电路设计中有很大的应用价值。

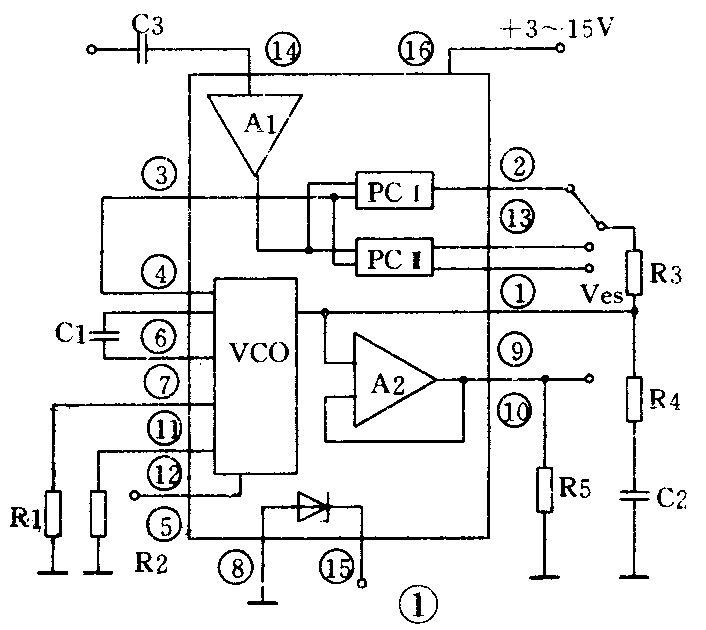

它的内部框图见图1。由图可知它内部含有一个线性压控振荡器(VCO)、两个具有公共输入端的相位比较器(PCⅠ,PCⅡ)、一个信号放大器(A1),一个电压跟随器(A2)、一个5.2V的齐纳二极管。压控振荡器需要外接一个电阻R1或者两2个电阻R2、R1和一个电容C1。R2和C1决定压控振荡器的最低频率,不接R2时最低频率为直流。中心频率近似按公式f≈1/2π R1·C1计算。压控振荡器的电压输入端输入电阻很高,达10\(^{12}\)Ω,这在设计锁相环路的低通滤波器时很方便。如果低通滤波器还要带外接负载,电路中还设有一个电压跟随器A2,负载电阻大于10kΩ。5脚是微功耗控制端,高电平时压控振荡器停振,电路处于微功耗状态,一般使用时接地。相位比较器的信号输入端(14脚)可以直接与CMOS电路相接,在非CMOS电平时应加入一个耦合电容。相位比较器Ⅰ(PCⅠ)是一个异或门电路,它要求输入信号的占空比是50%,并且没有噪声,用该相位比较器锁相后的波形与原信号有90°固定相位差。相位比较器Ⅱ(PCⅡ)是一个前沿触发数字相位比较器,锁相后与原信号同相,对输入波形无特殊要求,只是要求信号幅度应大于200mV,无信号输入时该输出频率取决于R2、C1。低通滤波器截止频率设计时可按公式f\(_{c}\)=1/2π\(\sqrt{2πf}\)/(R3+R4)C2计算,其中f是压控振荡器的中心频率,实际中常省去R4,这时fc=1/2π2πf/R3·C2。图中①脚是锁相指示。应用举例如下。

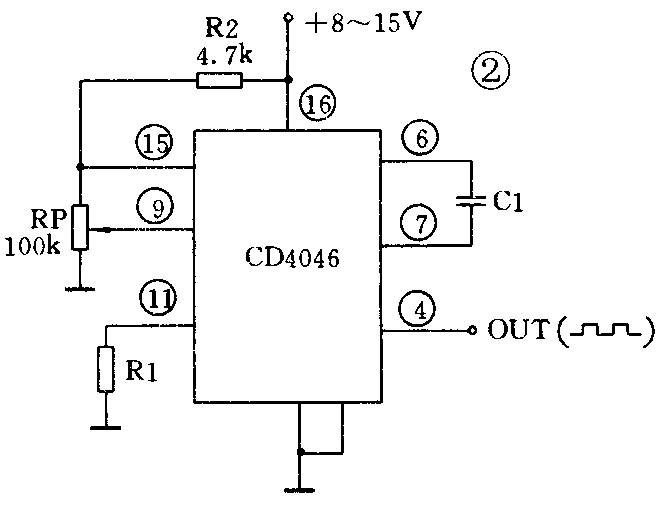

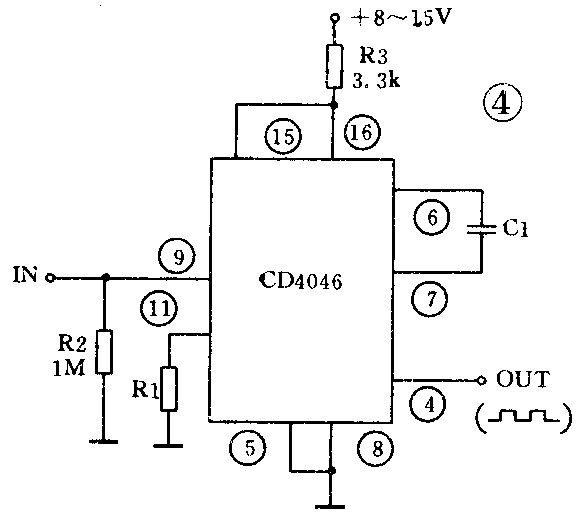

一、微功耗方波信号发生器,见图2。调节RP可以改变输出频率,频率范围取决于R1和C1。为使输出频率稳定,电路利用了内部稳压二极管进行稳压。

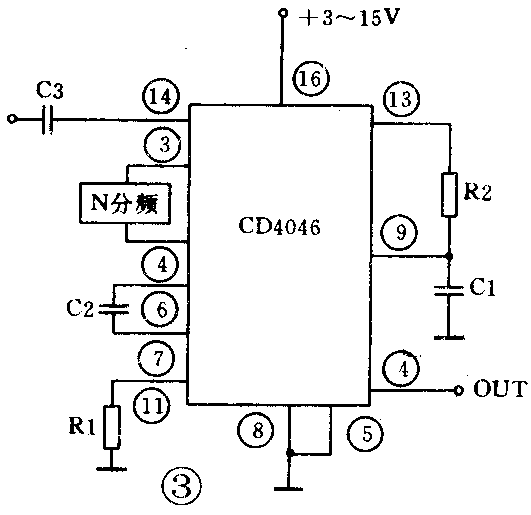

二、N倍频器,见图3。分频器也可用CD4040、CD4024、CD40192、CD40193等CMOS数字集成电路。注意中心频率应设在倍频附近才有很好的锁定性。

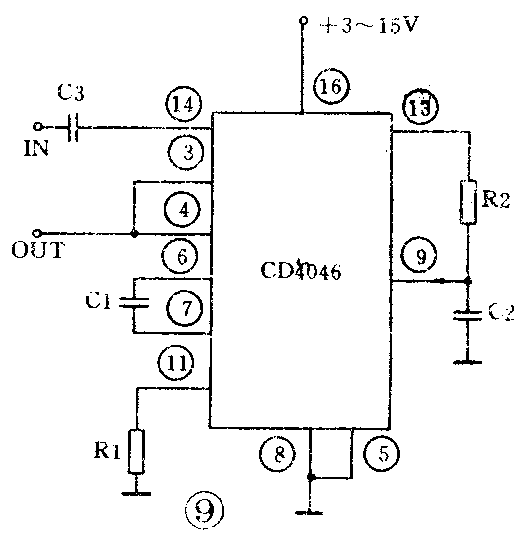

三、V—F变换器,见图4。输入电压应小于5.2V。该电路采用了内部的稳压管作为基准电源,可以根据需要外接。

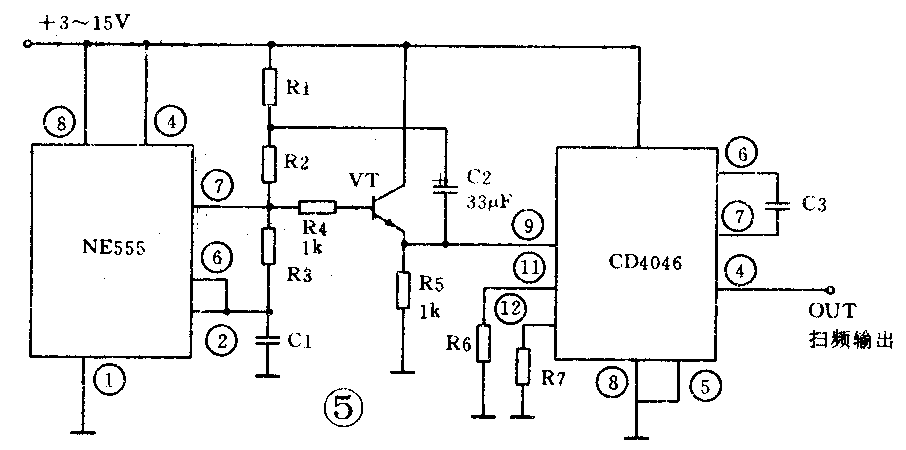

四、扫频信号发生器,见图5.该电路中的NE555用来产生线性良好的锯齿波,锯齿波的频率(即扫频频率)取决于R1、B2、R3和C1,按f=1/ ( 1.41(R1+R2+2R3)) C1进行计算。扫频范围取决于R6、C3、R7。

五、频率调制器,见图6。频率调制度取决于R1、R2、C1。

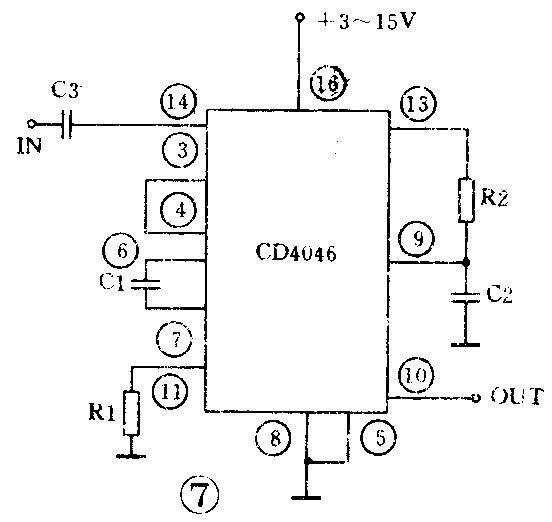

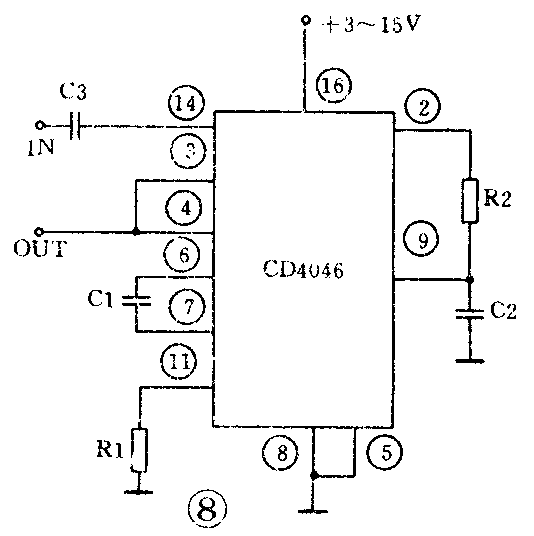

六、频率解调器,见图7。其实该电路就是一个锁相环路,当输入是调频波时,从低通滤波器输出的就是解调后的波形。

七、90°移相器,见图8。该电路利用了相位比较器 Ⅰ( PCⅠ)锁相后有90°相移的特性。

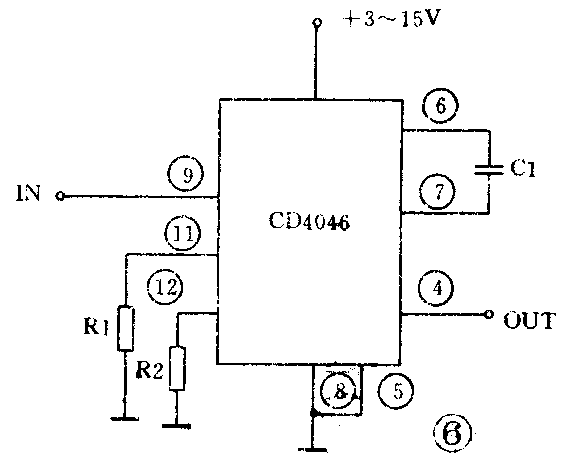

八、波形变换电路,见图9。 该电路利用相位比较器Ⅱ(PC Ⅱ)对输入波形锁相。不管输入何种波形及任意占空比,锁相后输出的都是频率不变,占空比为50%的方波。注意输入信号的幅度应大于0.2V,噪声峰值小于 0.1V。(曹福新)