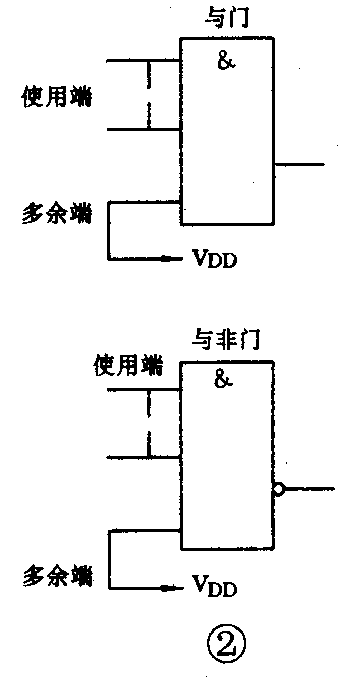

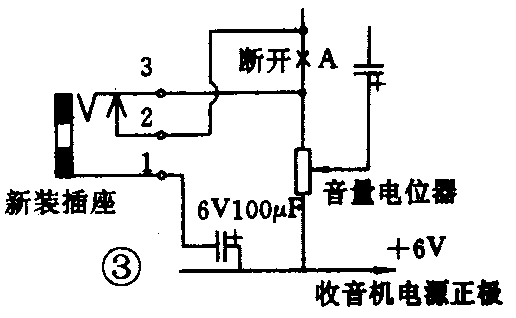

CMOS门电路的余引脚一般有3种:空脚(NC)、输出端和输入端。对空脚及输出端,通常不用连接,任其闲置。但多余的输入端必须作适当连接,否则因CMOS门电路输入阻抗极高,非常容易引入足以影响电路正常工作的外界干扰。多余输入端的连接要以不影响其它输入端逻辑功能的原则来处理。根据门电路的逻辑关系可以得到这样的结论,即:或门和或非门的多余输入端应接至V\(_{SS}\)(地)端,如图1所示。与门和与非门的则接至VDD(电源)端,如图2所示。也可以将多余输入端与使用的输入端并联起来,如图3所示。但并接输入端会影响门电路的开关门阈值电平和导致输入电容增大。前者对制作阈电平较讲究的电路(如施密特电路)需加以注意;后者在工作速度较高的电路中要加以考虑。不过一般初级电子制作很少涉及这类问题,故并接输入端方法也是很常用的。

如果应用一块CMOS门电路,多余出一个或数个门时怎么办?这种情况十分常见,例如应用CC4069六非门,只用了四个非门,就多出了两个非门。对此,处理的方法大体上和上述相同,不同处有两点:一是多余门的输入端既可接V\(_{DD}\),又可接VSS,任选其一。因为多余门不工作,不必考虑其逻辑关系,但抗干扰仍应虑及。二是并接输入端方法不适用多余门。因多余门中无使用的输入端。所以,对有多个输入端的多余门电路,应将多个输人端并联后再接V\(_{DD}\)或VSS。(轶奇)