调试数字电路时常常需要观测单次数字信号,用一般的示波器难于反复观测瞬现即逝的单次信号。本文介绍的单次数字信号存储电路能够捕捉(写入)和反复输出(读出)单次数字信号。

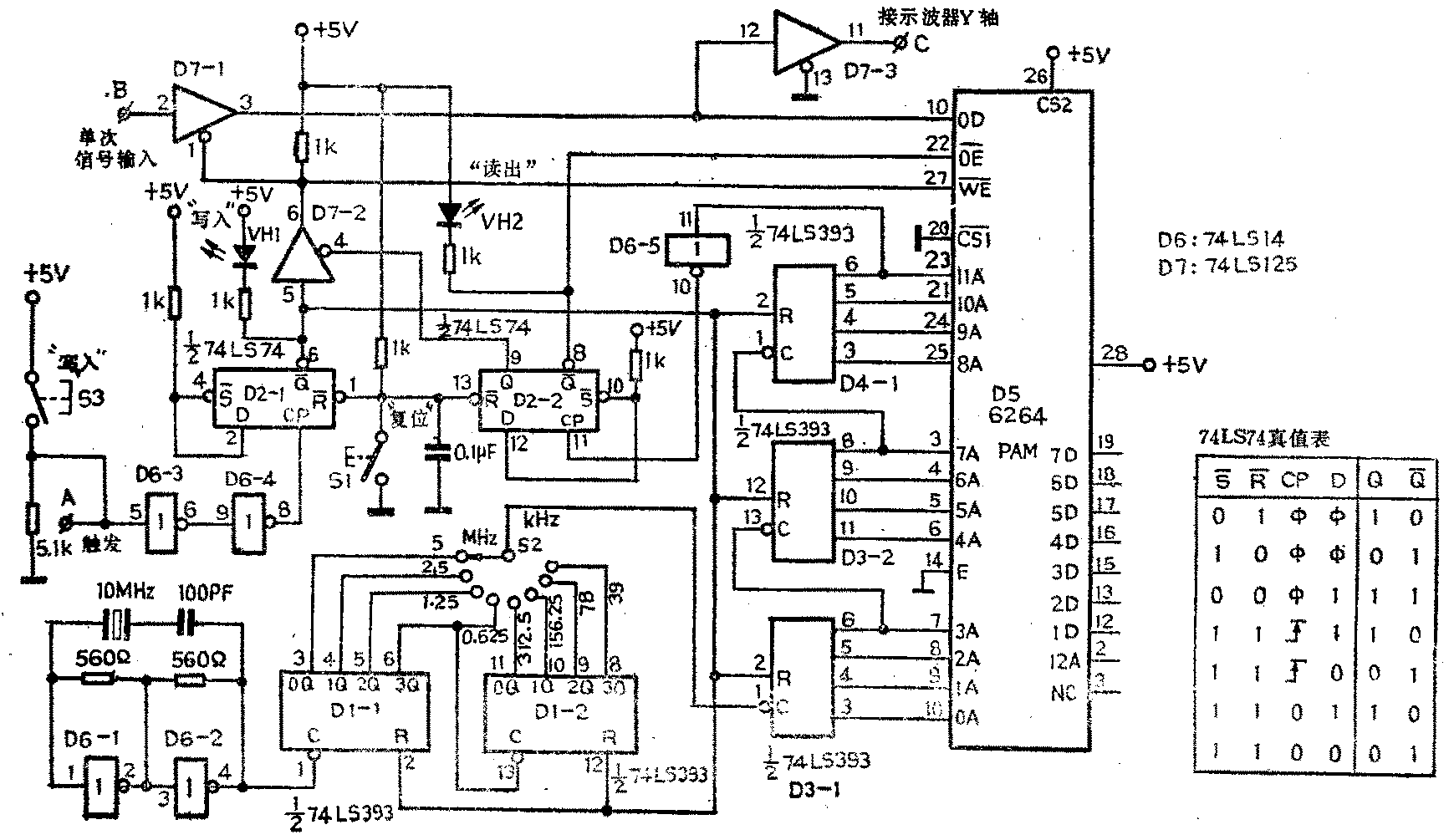

电路原理图见附图,图中,由B端输入的单次信号通过D7-1送入6264 RAM(8k×8bit,即8192×8bit)的数据端0D(1D~7D未用),同样,6264RAM的0D端可通过DF3向C端输出单次信号。D3-1、D3-2及D4-1(双4位二进制计数器74LS393)等组成地址发生器,为6264RAM提供地址计数值。D1-1、D1-2(74LS393)用作10MHz晶振频率的分频器,产生39kHz~5MHz采样频率,供给地址发生器作计数时钟。6264RAM的写入或读出由D2-1、D2-2及周围电路来控制,过程如下:①按下复位关S1,D2-1的Q-端为“1”,D2-2的Q、Q-端为“0、1”。由于D2-1的Q为“1”,使5个\(\frac{1}{2}\)74LS393清零,它们所有的Q端均为“0”。由于D2-2的Q端为“0”,三态门D7-2开通,5脚(即D2-1Q-端)高电平“1”通过D7-2使6脚亦为“1”,故D7-1的1脚也为高电平,D7-1被封锁,此时B端输入单次信号不能通过D7-1送往6264 RAM的0D端。②按下S3或在A端出现触发正脉冲时,D2-1的Q-端由原来的“1”变为“0”,使D7-2的6脚变为“0”,即D7-1的1脚变为“0”,三态门D7-1被开通,B端输入的单次信号可通过D7-1送往6264的0D端;由于D7-2的6脚变为“0”,所以6264RAM的WE-端为低电平,RAM处于写入状态;同时,由于D2-1的Q-端为“0”,5个1;274LS393的R端变低电平,停止复位开始计数;6264RAM得到地址计数值,便逐个单元存入B端输入的单次信号瞬时值。

6264RAM中存储的数据含义是什么呢?设在采样频率为2.5MHz时,15号地址单元0D=1,而其它地址单元0D均为“0”,则说明该输入脉冲宽度为1/(2.5×10\(^{6}\))=400×10-9(s)=400ns。

由于没接6264RAM的12A地址线,所以只用了它的一半存储空间,即4096个存储单元,此时0A~11A起作用。当写入B端送来的单次信号时,地址计数到2048个单元后,11A电平由“0”变为“1”,由于反相器D6-5的作用,在D2-2的C端出现由“1”到“0”的负跳变。从74LS74真值表中看到,D2-2并不发生反应,电路各种状态不变。当地址计数到4096个单元后,11A端由“1”变为“0”,经D6-5反相后,D2-2的C端产生“0”→“1”的正跳变,使D2-2Q端由“0”变为“1”(Q-变为“0”),D7-2的控制端4脚变为高电平使该三态门关断,其6脚电平不再受5脚控制,而是被接于+5V的1kQ电阻上拉为高电平,故D7-1又被关断,停止采样。由于D2-2Q-端为“0”,故6264RAM的OE-(读出允许)变为低电平有效,RAM可向外读出数据。地址发生器不停地计数,6264RAM通过0D向C端反复放出单次数字信号,这样一个不易观察的单次数字信号就被清晰稳定地显示在示波器上。

使用时,A端可接到被测电路中的启动信号。按下S1复位后,按S3或A端有触发信号时,电路进入采样,采满4096个单元后,自动反复重放存入的单次信号。采样频率选择开关S2可根据被测脉冲宽度决定。如果示波器上出现的脉冲信号过窄,可提高采样频率以展宽信号。

本电路实际上是对6264RAM的地址线、控制线及数据线进行控制,完成数字量存储的功能。(徐玉麟)