(俞鹤飞)前面介绍的是TTL集成逻辑电路。由于它是利用电子和空穴两种载流子导电的,所以也叫做双极型电路。除了双极型电路外,还有一类只用一种载流子导电的电路,这就是MOS电路。其中用电子导电的称为NMOS电路;用空穴导电的称为PMOS电路;如果是NMOS和PMOS复合起来组成的电路则称为互补MOS或CMOS电路。

MOS管的工作原理

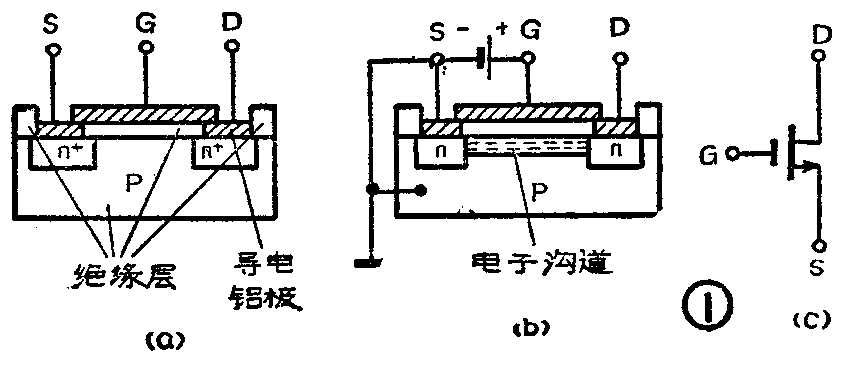

在一块P型材料衬底上做成两个n区,这两个n区之间的表面覆盖一层二氧化硅绝缘层,绝缘层上引出一个铝电极,这个电极称为栅极(G)。再在两个n区上引出两个电极,一个叫源极(S),一个叫漏极(D),这样就得到一个有3个电极的MOS管,如图1(a)。由于栅极和基片之间有一层绝缘层,它又是利用电场原理工作的,所以它叫做“绝缘栅场效应管”。从工艺上讲,它是由金属、氧化物和半导体材料组成的,所以也可以叫做“金属—氧化物—半导体场效应管”,简称MOS场效应管或MOS管。

现在让我们来看看MOS管的开关作用。

当栅极G上的电位是零时,两个n区之间因为有P体阻挡,源极S和漏极D之间总有一个P-N结是反向而不能导电,S和D两点是不通的。这时S和D好象开关的两个断开的接点。

当栅极加上正电位时,栅极下面氧化层中产生电场,把P体中少量电子吸引到这里,形成一个导电层,使两个n区连通而导电,如图1(b)。这个导电层被称为沟道。由于它是通过电子导电的,称为n沟道。这种MOS管就叫做n沟道MOS管或NMOS管。这时如在D、S之间加上正电压,使D的电位比S高,就会有电流从D流向S,这个电流称为漏电流I\(_{DS}\)。这时S和D好象是开关的两个闭合的接点。可见,MOS管和晶体管一样,也可以成为一种电子开关,它是用改变栅极电位的方法控制开关的闭合或断开的。

对MOS管来说,刚开始形成沟道而使D、S导通的最小栅极电压值称为开启电压V\(_{T}\)。因为MOS管的绝缘层有极高的绝缘电阻,它的输入阻抗极高,一般为几十兆欧,它的栅极电流极小,可以认为是零。所以MOS管是一种电压控制元件,很象以前广泛使用的电子管。因此它和电子管一样,也是用跨导(Gm)来说明它的特性的。跨导的含义是指栅极电压每变化1伏引起漏、源之间电流的变化量。MOS管的跨导一般是几百微安/伏。

NMOS管的符号表示如图1(c)。S极上箭头的方向表示它的电流是从D流向S。

栅极电压为正时形成导电沟道的NMOS管,称为增强型NMOS管。由于制造工艺的不同,另一种NMOS管是在栅极电压为零时已经形成导电沟道,必须在栅极加上负电压才使沟道消失,这种NMOS管就称为耗尽型NMOS管。

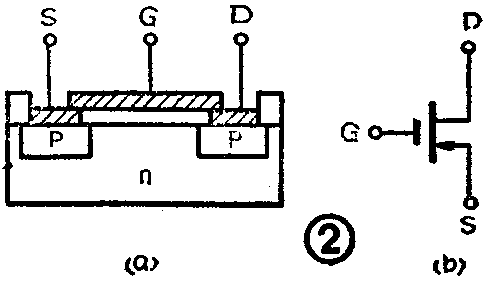

如果改变使用的材料,例如用n型材料作衬底,在衬底上做两个P区作为源极和漏极,得到的就是PMOS管,如图2(a)。PMOS管是用空穴导电的,它的栅极和漏、源极之间加的是负电压,电流方向是从S流向D,因此它的符号中S极上的箭头是从外向里的,如图2(b)。有的时候,当整个电路使用的只是一种MOS管,例如全部是PMOS管或全部是NMOS管时,这个箭头也可以省略不画。同样,PMOS管也有增强型和耗尽型两种。

MOS集成逻辑电路

MOS集成逻辑电路就是用MOS管作基本元件组成的,例如:

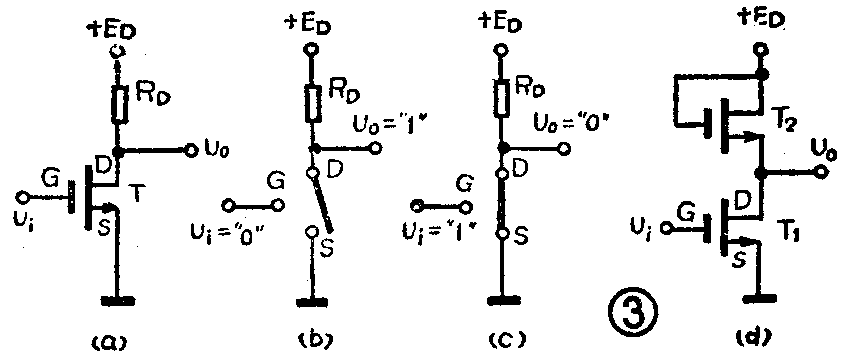

(1) NMOS非门

用一个NMOS管和一个电阻可以组成非门,如图3(a)。图中T是n沟道增强型MOS管,R\(_{D}\)是漏极负载电阻,栅极G是输入端,漏极D是输出端。假定电源电压是+10伏,栅极开启电压是2伏,高电平“1”是10伏,低电平“0”是0伏。

①当输入为低电平,即U\(_{i}\)=0伏时,T截止,D、S间不通,相当于开关断开。这时输出为高电平,即Uo=10伏,如图 3(b)。

②当输入为高电平,即U\(_{i}\)=10伏时,T导通,D、S间有电流流通,相当于开关闭合。这时输出为低电平,即Uo=0伏,如图3(c)。

可见这个电路能完成非门的逻辑功能。

为了工艺制造上的方便,实际电路中的负载电阻是用MOS管代替的,如图3(d)。因为T\(_{2}\)的栅极和电源相连,所以T2总是导通的。在这种情况下,T\(_{2}\)称为负载管,T1称为开关管或驱动管。

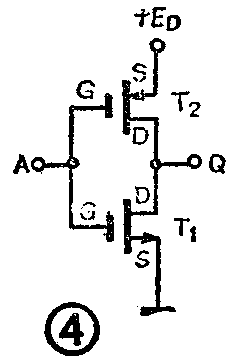

(2)CMOS非门

用一个PMOS管替换图3(d)中的负载管T\(_{2}\),把两个管子的栅极并接在一起作为输入端A,T2的源极接到电源正端,T\(_{1}\)的源极接地,T2和T\(_{1}\)的漏极并接在一起作为输入端Q,就得到一个CMOS非门,如图4。因为这个电路既有PMOS管又有NMOS管,两者是互补关系,称为互补MOS非门或者简称CMOS非门。

①当输入A为低电平“0”时,对T\(_{1}\)来说,Ugs1=0,T\(_{1}\)截止;对T2来说,由于栅极电位比源极低:U\(_{gs2}\)=-ED,│U\(_{gs2}\)│>│VT│,所以T\(_{2}\)导通。于是P端为电源电压+ED,即输出成为高电平“1”。

②当输入A为高电平“1”时,对T\(_{1}\)来说,Ugs1>V\(_{T}\),T1导通;对T\(_{2}\)来说,栅极电位和源极相等:Ugs2=0,T\(_{2}\)截止。于是Q端为地电位,即输出是低电平“0”。

可见从逻辑功能上分析,这是一个非门。

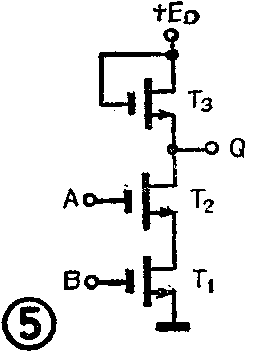

(3)NMOS与非门

用两个NMOS管串联起来作驱动管,一个NMOS管作负载管,可以组成一个NMOS与非门,如图5。两个驱动管的栅极就是与非门的输入A、B。

这个电路只有当输入A、B都是高电平“1”时,T\(_{1}\)、 T2才都导通,输出Q为低电子“0”。因此这是一个与非门,它的逻辑表达式是:

Q=A·B-

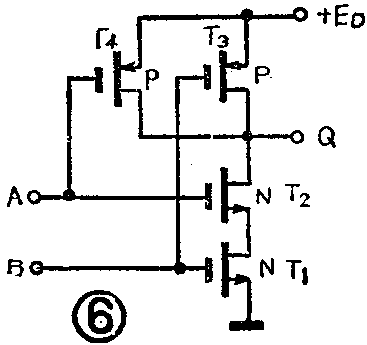

(4) CMOS与非门

用两个并联的PMOS管作负载管,两个串联的NMOS管作驱动管,负载管和驱动管的栅极分别接到输入端A、B上,如图6,就得到一个CMOS与非门。

当电路的输入端A和B都是高电平时,T\(_{1}\)、T2导通,T\(_{2}\)、T4截止,输出端Q为低电平。输入端A、B中只要有一个是低电平时,T\(_{1}\)、T2中必有一个不通,T\(_{3}\)、T4中必有一个导通,使输出端Q成为高电平。因此这是一个与非门,它的逻辑表达式是:

Q=A·B-

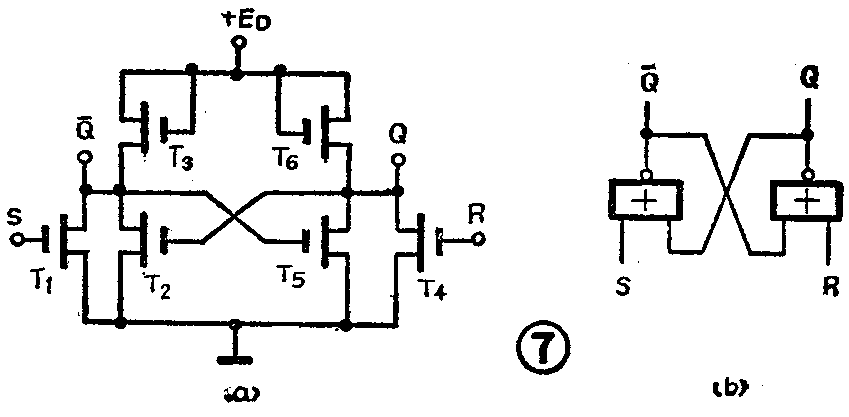

(5)NMOS R-S触发器

用6个NMOS管就可以组成一个基本R-S触发器,如图7(a)。图中T\(_{1}\)、T2、T\(_{3}\)组成一个或非门,T4、T\(_{5}\)、T6组成另一个或非门。把T\(_{2}\)的栅极连到Q端,T5的栅极连到Q-端,使两个或非门交叉连接成一个基本R-S触发器,如图7(b)。

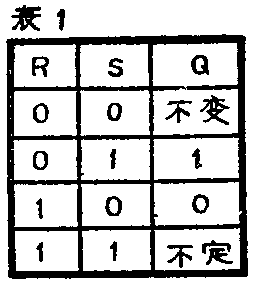

这个电路是用正脉冲触发的,它的逻辑功能:

①R端、S端加低电平,即R=0,S=0时,T\(_{1}\)、T4截止,触发器维持原态不变。

②R=0, S=1时,T\(_{4}\)截止,T1导通。由于T\(_{1}\)导通,使Q-=0,Q-交叉连接到T5栅极,使T\(_{5}\)截止(R=0也使T4截止),使Q=1。因此触发器置1。

③R=1,S=0时,T\(_{4}\)导通,T1截止。结果是Q=0,Q-=1,触发器置0。

④ R=1,S=1时,T\(_{1}\)、T4都导通。当触发脉冲拆除后由不平衡电流决定触发器的状态。所以触发器是“不定”状态。可见这是一个基本R-S触发器,它的特性见表1。

从以上介绍可见,MOS集成逻辑电路只需少量几个管子就可以组成门电路和触发器,它的集成度要比TTL电路高得多。

MOS集成逻辑电路的优点

下面通过CMOS和TTL电路部分性能的比较,可以看出MOS电路有许多优点。

(1)静态功耗低。TTL电路的静态电流较大,每个门消耗的功率大约是2~20毫瓦,而CMOS电路因为工作电流很小,每个门消耗的功率只有0.01毫瓦,相差一百多倍。

(2)输出高、低电平的差值大。例如当使用电源电压是10伏时,CMOS电路的输出高电平U\(_{QH}\)=9.9伏,输出低电平UQL=0.1伏。不仅电源电压得到充分利用,也提高了抗干扰能力。

(3)抗干扰性能好。说明抗干扰性能的参数叫做噪声容限。我们习惯上常把干扰电压叫做噪声电压,所以噪声容限实际是指容许的干扰电压的幅度。噪声容限数值大说明电路的抗干扰性能好。TTL电路的噪声容限只有零点几伏,大约是电源电压的16%。CMOS电路因为用较高的电源电压,高、低电平差值大,它的噪声容限可达到电源电压的30~45%。

(4)开关速度较高。MOS电路的速度一般比TTL电路为低。目前CMOS电路的速度已接近中、高速TTL电路的速度。

(5)扇出系数大。CMOS电路因为输入阻抗高,输出阻抗低,所以它的负载能力很强。TTL电路的扇出系数N\(_{0}\)一般为10,CMOS电路则在50以上。

(6)集成度高。由于MOS电路比TTL电路简单,所以集成度高,适宜于制作大规模和超大规模集成电路。

通过以上比较可以看到,CMOS电路除了在速度上还比不上TTL电路外,其它性能都超过了TTL电路,所以得到了广泛的应用。

与使用有关的3个特殊问题

(1)电波电压的极性和数值。TTL集成电路的电源是统一的+5伏。而MOS集成电路的电源电压和极性却是随着电路的类型而变化的:PMOS电路使用负电源,一般为-20伏;NMOS电路使用正电源,一般为+5伏;CMOS电路也是正电源,所用的电压有+5伏、+10伏或+15伏。因为TTL电路是正电源,所以一般都喜欢使用正电源的MOS电路,这样电路连接问题简单。

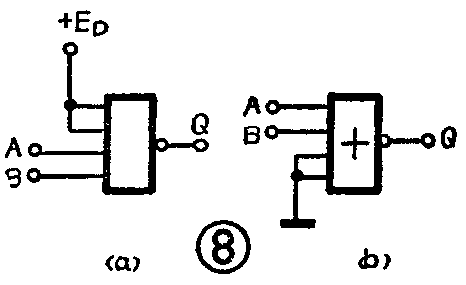

(2)安全问题。MOS管的输入阻抗极高,因此MOS集成电路中不使用的空余端子是不允许悬空的。因为输入端悬空会感应静电或受到外界的干扰,轻则使MOS电路工作失常,重则使栅极击穿损坏片子。所以对MOS集成数字电路多余的输入端应该接到电源端或高电平上(与门、与非门)。如图8(a);或者接到地端或低电平上(或门、或非门),如图8(b)。

由于同样的原因,在存放和运输时,应该把MOS集成片用铝箔包好放在屏蔽盒内;在焊接时应使用功率不大于20瓦的烙铁并保证电烙铁有良好的接地;在测试时要使仪表外壳可靠接地等等。有时为了防止栅极击穿,也可以在输入端增加各种防护电路。

(3)电路连接问题。当MOS电路和其它电路连接时要注意并解决电平转换和驱动能力问题。

例如当TTL电路和CMOS电路连接时,TTL电路的输出高电平在电源电压是+5伏时,V\(_{OH}\)=2.4伏。CMOS电路的最小输入高电平在电源电压是+5伏时VIH=3.5伏,电源是+10伏时,V\(_{IH}\)=7.0伏。因此必须把TTL电路的输出高电平提高到CMOS电路所要求的数值上才能使电路正常工作。提高的方法可以用电平转换电路或者采用能把电平值提升起来的CMOS集成接口电路。在驱动能力方面,因为TTL电路的驱动能力比CMOS电路大,所以可以不去考虑。

当CMOS电路和TTL电路连接时,因为CMOS电路输出电流小,带动TTL电路负载有困难,所以除了要解决电平转换问题外,还要考虑增大CMOS电路的驱动能力。具体方法可以使用带缓冲驱动器的MOS电路或者在CMOS电路后面加晶体管驱动级。

同样,在不同类型的MOS集成电路互相连接时以及MOS电路和显示器、晶体管电路、机电开关等连接时,也要考虑这些问题。

复习思考题

1.MOS管是怎样工作的?为什么把CMOS电路叫做互补MOS管电路?

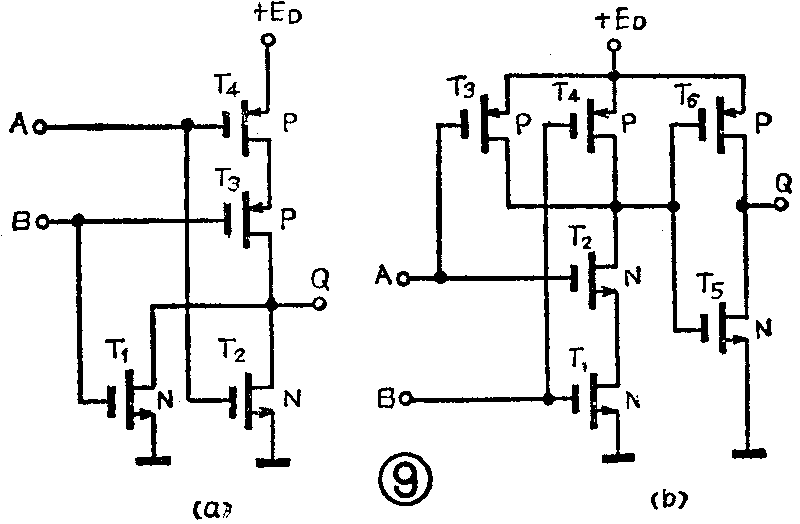

2.分析图9中的CMOS集成逻辑电路,写出它们的逻辑表达式。

上期答案

2.T=1微秒,f=1兆赫。