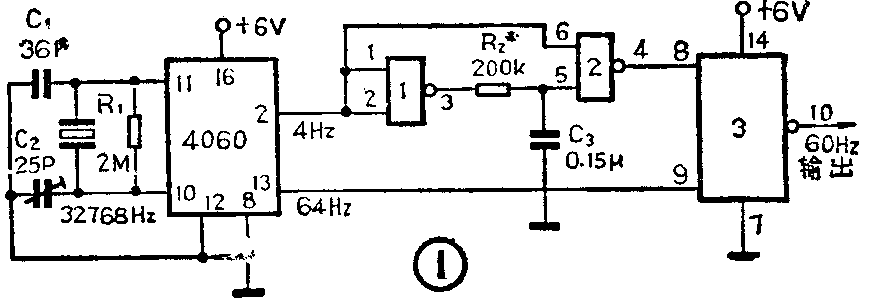

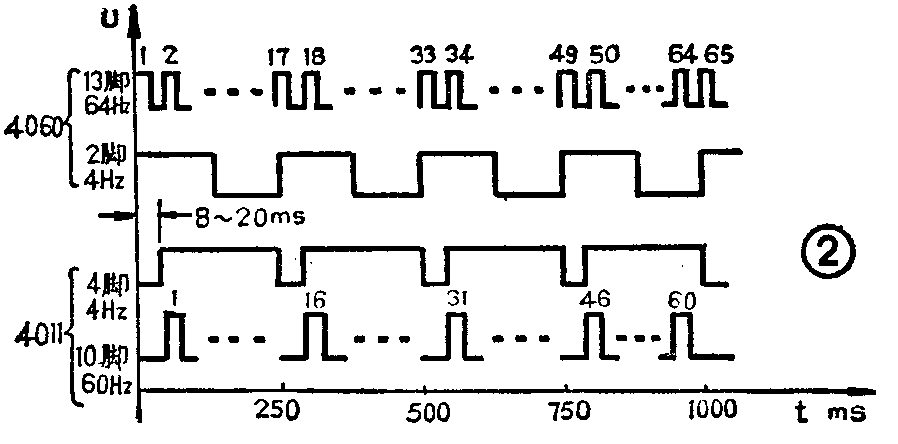

笔者只用两块IC制成了高精度的60Hz时基信号发生器,其原理电路如图1。我们知道,32768Hz信号经9级2分频后变为64Hz,如果将此64Hz信号周期地每秒去掉4个脉冲就变成了60Hz的信号,尽管脉冲分布不均匀,但对电子钟来说无任何影响。图1中,4060担任振荡和分频,这部份以前的文章均有介绍,不再详述。由4060的13和2脚分别输出64Hz和4Hz的信号送入下级处理。四双输入端与非门4011中的两个与非门1、2构成单稳电路,其暂稳时间常数t取为64Hz信号一个脉冲的宽度,即t=12×64≈7.8125ms。与非门3作为输出控制门。各点波形如图2所示,由图2中可看出,单稳电路每被触发一次,它就将控制门3封住一次,从而使输出丢掉一个脉冲。单稳每秒共被触发4次,64个脉冲就丢掉4个,变成60个,输出就变为60Hz了。当然,脉冲间隔是不等的,但这种脉冲作数字钟的时基时绝不影响其计时精度。调节电路中的R\(_{2}\)、C3可改变暂稳时间常数(t=R\(_{3}\)×C3),经实验,t调在8~20ms电路均可正常工作。(河北深泽县邮电局 贾聚中)