十进制计数器

我们日常习惯使用的是十进制数。4个触发器组成的计数器可以表示0~15共16种状态。要完成对十进制数的计数,一是只能使用BCD码,二是必须从连接上想法,使计数器从0计到9,在第10个cp到来后,计数器又复原成0(同时向高位进位),完成1位十进制数的计数任务。

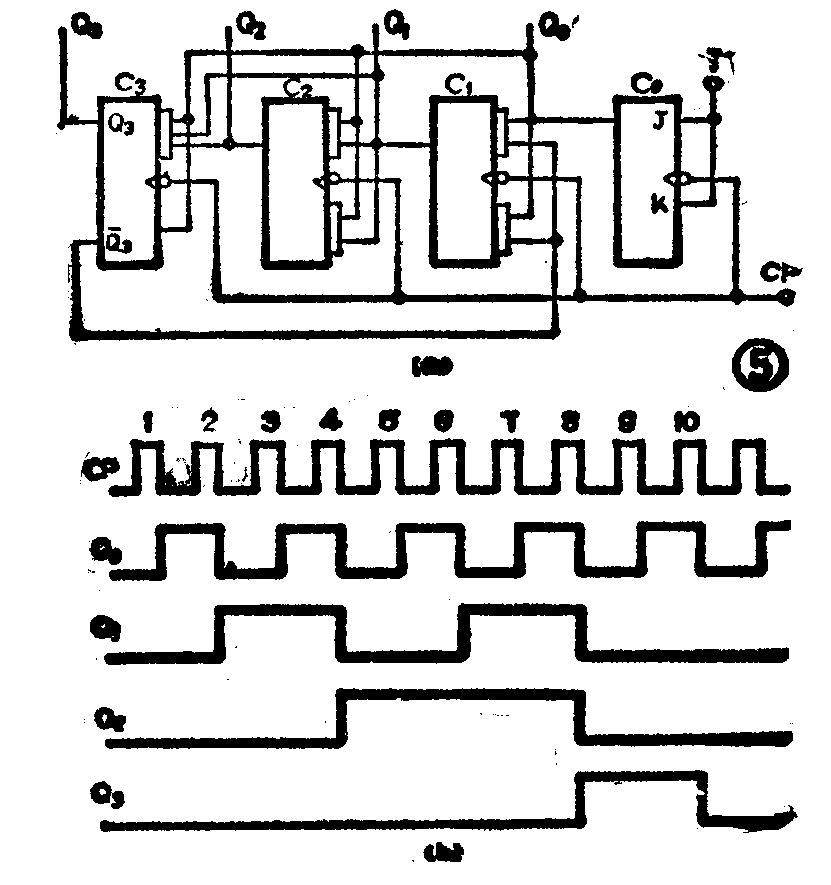

图5(a)是一个8421-BCD码的计数器。它能从0计到9,当连续输入9个脉冲后,计数器状态为1001,如果再输入1个脉冲,它就会回到0000的状态。按图中各个端子的连接,可以列出4个触发器输入端的逻辑式:

J\(_{0}\)K0=1

J\(_{1}\)K1=Q\(_{0}\)Q-3

J\(_{2}\)=K2=Q\(_{0}\)Q1

J\(_{3}\)=Q0Q\(_{1}\)Q2, K\(_{3}\)=Q0

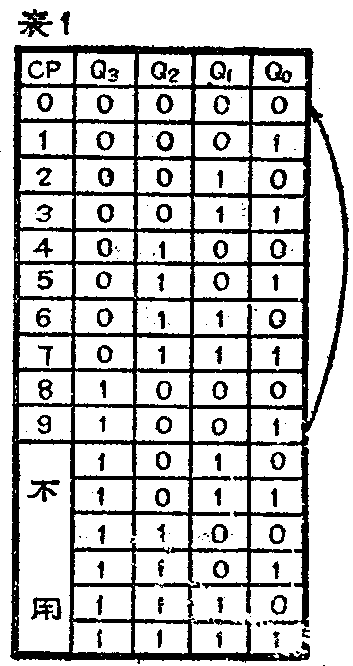

现在让我们用逻辑关系来说明它的工作原理。为了说明的方便,同时给出了计数状态真值表,见表1。

(1)按J\(_{0}\)和K0的逻辑式,触发器C\(_{0}\)是每个cp翻转1次。(2)按J1和K\(_{1}\)的逻辑式并对照计数状态表,在0~7这8种状态下,Q3=0,即Q-\(_{3}\)=1,所以触发器C1只在Q\(_{0}\)=1时才翻转,即每2个cp翻转1次;而在8~9这两种状态时,因为Q-3=0,所以触发器C\(_{1}\)维持原态不变。(3)按J2和K\(_{2}\)的逻辑式,只有在Q0和Q\(_{1}\)都是1时,J2=K\(_{2}\)=1,所以触发器C2是每4个cp翻转1次。(4)按J\(_{3}\)和K3的逻辑式并对照计数状态表,在0~6的计数状态时,因为Q\(_{0}\)、Q1、Q\(_{2}\)这3个值中至少有1个是0,所以J3=0,K\(_{3}\)=Q0。按J-K触发器的真值表:K=0时,触发器维持原来的0态;K=1时,触发器置0,因此触发器C\(_{3}\)仍维持原来的0态。当计数状态是7时,J3=Q\(_{0}\)Q1Q\(_{2}\)=1,K3=Q\(_{0}\)=1,所以当第8个cp来到后,触发器C3翻转成1,使计数器成为1000状态。在第9个cp来到前,因为J\(_{3}\)=0,K3=0,所以第9个cp来到后,触发器C\(_{3}\)仍维持原来1态不变。在第10个cp来到前,因为J3=0,K\(_{3}\)=Q0=1,所以当第10个cp到来后,触发器C\(_{3}\)被置成0, 计数器成为0000状态。从计数状态表看到,它从9又回到了0,计数状态表中从10~15这6个状态是不出现的。

从以上整个工作过程看,这个计数器能完成从0~9的计数工作,并且它的计数过程是符合8421BCD码的计数规律的。所以它被称为8421BCD码计数器,简称十进制计数器,用这样的一组触发器可以计1位十进制数。如果用2组触发器,把第1组的Q\(_{3}\)接到第2组的cp端上,就可以组成2位十进制数的计数器,可以从0一直计数到99。

计数器除了有同步和异步的区别外,还有加法计数器、减法计数器和可逆计数器等不同种类。前面介绍的都是加法计数器,它们在工作时,是每输入1个cp脉冲,计数器就加1,它的计数顺序是0、1、2、…。另一种减法计数器是每输入1个cp脉冲,计数器就减1,它的计数顺序是从15、14…一个个递减的。如果是既可作加1,又可作减1的计数器就称为可逆计数器。此外,除了二—十六进制和二—十进制计数器,也还有一种对任意进位制进行计数的计数器,称为任意进制计数器或N进制计数器。它可以按要求连接成我们需要的N进制计数器。

计数器电路一般是用D触发器或J-K触发器组成的,目前已有中规模集成产品可供选用。例如,T210是二—十进制计数器,T217是二—十进制同步可逆计数器,T214是二—十六进制同步计数器,T215是二—十六进制同步可逆计数器,等等。

分频器

为了保证数字电路能协调有序地工作,需要有统一的指挥信号,即时钟脉冲或cp脉冲。它对整个数字系统来讲,可以认为是一个标准信号或者称为时基信号。因此对这个cp脉冲的要求是:脉冲周期应该稳定不变,脉冲宽度应该严格相等。由于电路工作的需要,有时需要有各种不同周期的标准信号,通常它是用一个频率较高的标准脉冲经过分频以后得到的。

我们知道周期的倒数是频率:f=1/T。假定数字系统中有1个标准脉冲,它的周期是:T=1微秒,即频率f=1MHz(兆赫)。现在还需要有1个周期T=10微妙(f=100kHz)的标准脉冲。那么,只要把f为1兆赫的标准脉冲通过1个10分频的分频器,就可以得到f为100千赫的标准脉冲。

前面介绍的十进制计数器,每到第10个cp脉冲到来时,就从1001的状态回到原始的0000状态,同时从Q\(_{3}\)输出1个脉冲(进位脉冲),也就是每10个cp输入,才输出1个脉冲。从分频的观点,输入如果是1兆赫的cp脉冲,输出得到的是100千赫的脉冲,因此1个十进制计数器同时也是1个10分频的分频器。这种分频器被称为脉冲分频器。如果这个计数器是8421BCD码计数器,那么从Q0端得到的是2分频的脉冲,从Q\(_{1}\)端得到的是4分频的脉冲,从Q2端得到的是8分频的脉冲。根据分频的要求,从N进制计数器的输出端就可得到N分频脉冲。

复习思考题

1.寄存器和计数器是怎样寄存数码和对数码进行计数的?

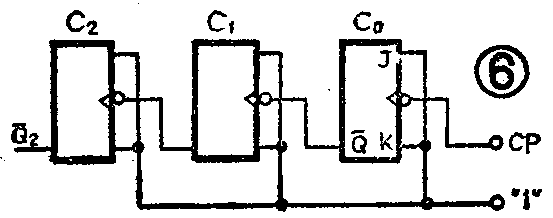

2.图6是一个异步3位二进制计数器,它由TTL的J-K触发器组成。试分析它的工作过程,列出计数状态表,说明它是什么样的计数器?

第5期答案

2.这是1个2位二进制计数器,第4个cp脉冲到来后,两个触发器都处于0态。 (俞鹤飞)