触发器有可控和不可控两大类,前面介绍的基本R-S触发器就是不可控的。它的状态除由输入信号R-\(_{D}\)、S-D和触发器原来所处的状态决定外,不受其它信号的控制。而可控触发器则不同,它的状态不仅由输入信号和触发器的原来状态决定,还要受时钟信号的控制。有时尽管输入信号已经是使触发器翻转的状态了,但在时钟信号没有到来前,触发器却不能翻转。只有在时钟信号到来之后,触发器才能翻转成新的状态。由于这个原因,我们把这种可控触发器叫做钟控触发器。常用的钟控触发器有:R-S触发器、D触发器、J-K触发器、T触发器等。

为什么需要时钟信号

数控装置和计算机电路的动作时间是极短的,一般都是以微秒(10\(^{-6}\)秒)、毫微秒(10-9秒)计算的。在这样快速动作的情况下,就要求组成数控装置和计算机的所有单元电路必须紧密配合,严格按规定的时间顺序进行工作,才能保证整个机器正常运行。为了做到这一点,就必须有一个统一的指挥信号,用这个信号去控制各部分电路协调有序地工作。通常我们把这个信号叫做时钟信号。又因为它是以脉冲形式给出的,所以也把它叫做时钟脉冲,有时也用英文缩写字母CP表示,称为CP信号或简称CP。

因为CP信号是严格按时间先后给出的一系列脉冲,每个脉冲的时间间隔是严格相等、准确可靠的,所以在对电路进行分析时也可以当作时间的基准。

钟控R-S触发器

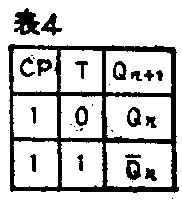

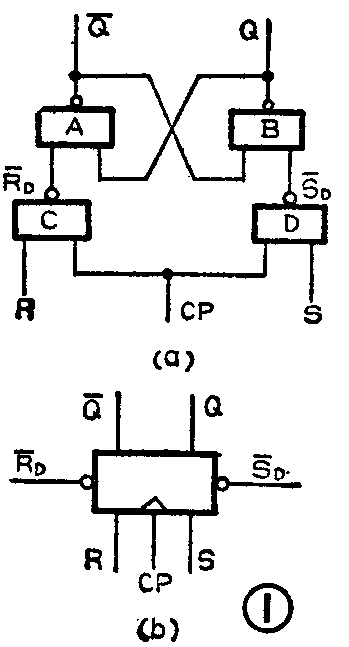

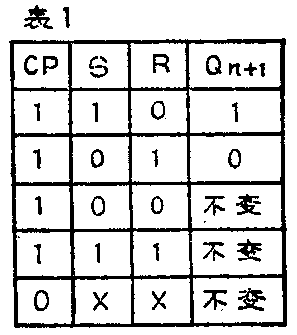

钟控R-S触发器,简称R-S触发器。它是在基本R-S触发器的基础上发展而来的。图1(a)是它的电路图。由此图可见,它的上半部分电路由两个与非门A、B组成,这部分是一个基本R-S触发器。下半部分两个与非门C、D起着传送和引导作用,被称为传送门或引导门。R-S触发器有R、S、CP 3个输入端,它们都是用高电平触发的。图1(b)画出了R-S触发器的逻辑符号图。

表1是R-S触发器的特性表。从特性表看到,R-S触发器的逻辑功能是:(1)不管触发器原来处干什么状态,只要S=1、R=0,CP到来,即CP=1时,触发器成为1态。(2)不管触发器原来是什么状态,只要S=0、R=1、CP=1时,触发器成为0态。(3)当S=0、R=0、CP=1时,触发器保持原状态不变。(4)当S=1、R=1、CP=1时,触发器状态不定,这种情况在使用时是禁止出现的。(5)在CP=0的情况下,不管S和R是什么状态,触发器都不改变原状态。由此可见,CP就象是下达命令的信号,只有在CP到来后,触发器才能按逻辑功能作出反应。

R-S触发器逻辑符号的两侧画有R-\(_{D}\)和S-D两个端子。平时R-\(_{D}\)=S-D=1,对触发器的状态没有影响。如果在S-\(_{D}\)端加低电平、R-D端加高电平(S-\(_{D}\)=0、R-D=1)时,则不管触发器处于什么状态,都会立即变成1态。而当R-\(_{D}\)端加低电平、S-D 端加高电平(R-\(_{D}\)=0、S-D=1)时,可使触发器立即变成0态。这个过程叫做预置。S-\(_{D}\)和R-D分别称为置1端和置0端。在工作中,我们可以根据需要利用S-\(_{D}\)和R-D端把触发器预置成1或0状态。

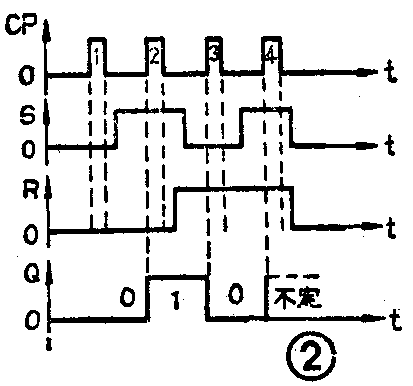

图2是R-S触发器的波形图。在这里假定触发器原来处于0态。当第一个CP脉冲到来时,因为S=0、R=0,触发器保持原来的0态不变。当第二个CP脉冲到来时,因为S=1、R=0,触发器由0态翻转成1态。第三个CP脉冲到来时,因为S=0、R=1,触发器又翻转成0态。第四个CP脉冲到来时,正是S=1、R=1,触发器出现不定状态,这种情况在实际应用中是不允许出现的。

D触发器

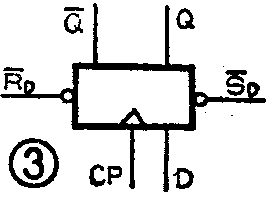

D触发器只有1个信号输入端D和1个时钟信号输入端CP。它的逻辑符号图见图3。在逻辑符号图中两侧的R-\(_{D}\)和S-D是预置端,它们的作用和R-S触发器中的相同。

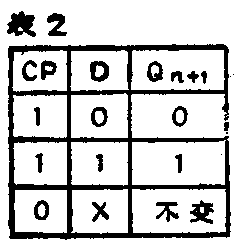

表2是D触发器的特性表,它概括了D触发器的逻辑功能:(1)当D=0,CP到来后(CP=1),不管触发器原来是什么状态,立即会成为0态。(2)当D=1,CP=1时,触发器立即成为1态。这说明D触发器的状态是由CP到来之前输入端D的状态决定的。(3)当CP=0时,不管输入端D是什么状态,触发器都保持原状态不变。从特性表可以看到,D触发器不存在不定的状态,说明它的性能更完善,更稳定可靠。

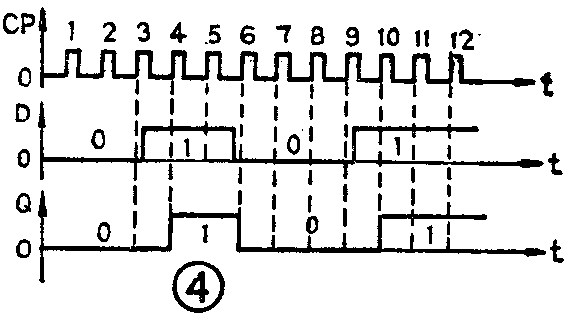

图4是D触发器的波形图。从图中看到,D触发器每次翻转都发生在CP脉冲的上升沿来到的时刻,因此我们常说D触发器是在CP脉冲的上升沿触发的。

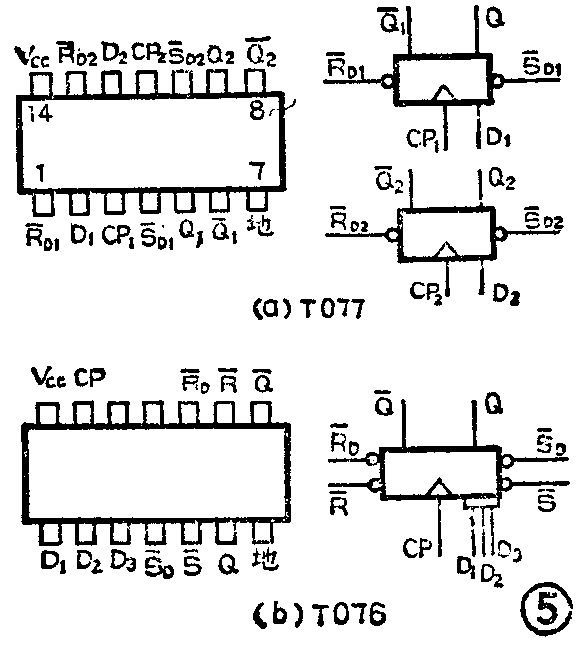

国产TTL集成触发器产品T077是一个双D触发器,在一个片子里有两个D触发器。T076是单D触发器,它有D\(_{1}\)、D2、D\(_{3}\) 3个输入端,它们之间是逻辑“与”的关系。这两种产品的引脚排列和逻辑符号图见图5。图中的R-D和S-\(_{D}\)都是预置端。此外还有R-和S-端。它们的区别是:在用R-、S-端给触发器置0或置1时,必须是在CP=0的情况下进行,而用R-D、S-\(_{D}\)预置时,则不管CP是什么状态都能把触发器置成0或1。

J-K触发器

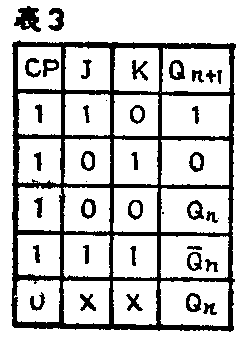

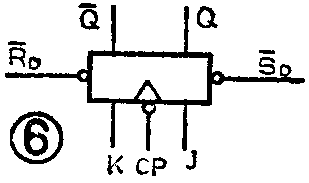

集成触发器中性能最优的是J-K触发器。它有J和K两个输入端、一个CP输入端,两个预置端R-\(_{D}\)和S-D。它的逻辑符号图见图6。特性表见表3。

从表3可看出J-K触发器的逻辑功能是:(1)CP=1、J=1、K=0时,不管触发器原来是什么状态,它都被置成1态。因此J端相当于置1端。(2)CP=1、J=0、K=1时,不管触发器原来是什么状态,它都被置成0态。因此K端相当于置0端。(3)CP=1、J=0、K=0时,触发器保持原状态不变。(4)CP=1、J=1、K=1时,触发器翻转1次。因此在保持J=1、K=1的情况下不断地送入CP脉冲,就可以使触发器每来一个CP脉冲翻转一次。我们把这种工作状态叫做计数状态。(5)当CP=0时,不论J、K是什么状态,触发器都保持原状态不变。从表中看到,J-K触发器没有不定状态,这是J-K触发器的优点之一。

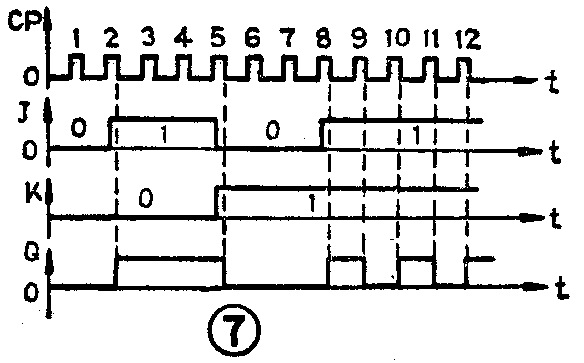

图7是J-K触发器的波形图。从波形图中看到,J-K触发器是在CP从1变为0的瞬间开始翻转的,因此我们说J-K触发器是下降沿触发,或者说是后沿触发的。

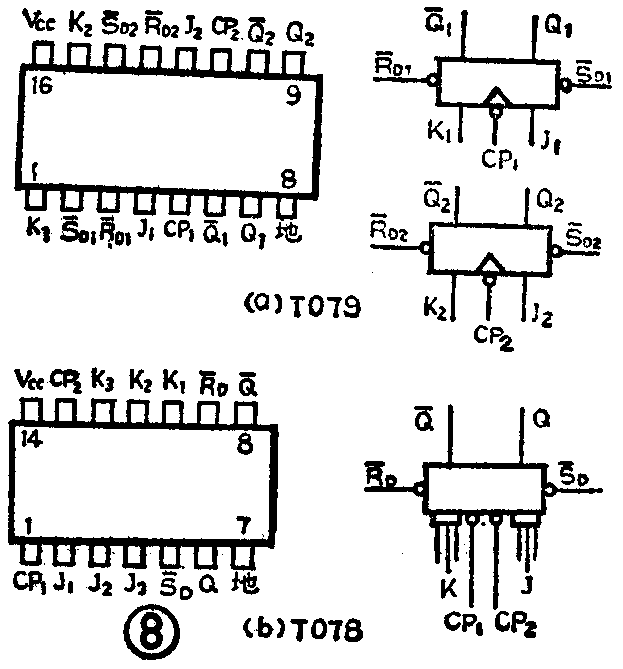

国产TTL集成触发器T079是1个双J-K触发器,T078是1个单J-K触发器。T078有J\(_{1}\)、J2、J\(_{3}\)3个J输入端和K1、K\(_{2}\)、K33个K输入端。J输入端之间以及K输入端之间是逻辑“与”的关系。上述两种产品的逻辑符号图和引脚图见图8。因为J-K触发器是下降沿触发的,所以在CP输入端加画一个小圆圈。

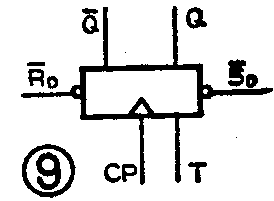

T触发器

T触发器的逻辑功能是:(1)当T=1时,CP到来后(CP=1),触发器翻转1次。(2)当T=0时,即使CP到来,触发器也不翻转而保持原状态不变。根据这个特性,如果一直保持T=1,那么每来1个CP脉冲,T触发器就翻转1次。因此可以用T触发器做计数工作。通常我们把T=1时的T触发器叫做T′触发器,或称为计数触发器。

触发器之间的转换

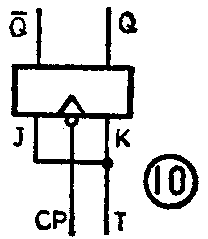

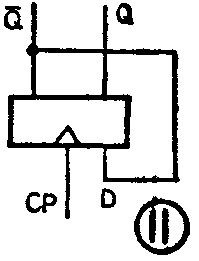

在实际应用中可以根据需要,经过适当的连接,把一种逻辑功能的触发器变换成另一种逻辑功能的触发器。例如把J、K两个输入端连在一起作为T输入端,就可以把J-K触发器变换成1个T触发器,如图10。也可以把D触发器改接成T触发器使用,如图11。只要把D触发器的D输入端和Q-端连接起来,这样,每来1个CP脉冲,触发器便翻转1次,它的逻辑功能就成为计数触发器,即T′触发器。

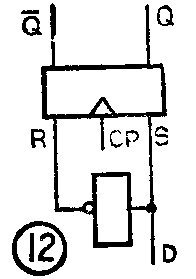

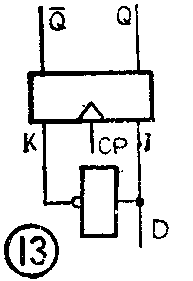

同样,经过改接可以把其它触发器变换成D触发器。例如在R-S触发器的输入端加接1个反相器,就可以变换成D触发器,如图12,在J-K触发器的两个输入端加一个反相器也可以变换成D触发器,如图13。

触发器之间的转换是简便的,但必须注意的是:用一种触发器转换成另一种触发器后,它的触发方式仍然应用原来触发器的触发方式。例如,由J-K触发器变换成T触发器后,仍然是在CP脉冲的下降沿触发。用D触发器变换成的T′触发器,仍然是在CP脉冲的上升沿触发。

复习思考题

1.D触发器和J-K触发器各有什么样的逻辑功能?它们对触发脉冲的要求有什么不同?

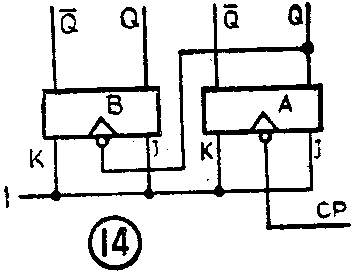

2.将两个J-K触发器的J、K端连接在一起接高电平“1”,并将触发器B的CP端和触发器A的Q端相连,如图14。设两个触发器的起始状态为00,从触发器A的CP端输入CP脉冲。问当第4个CP脉冲到来后,两个触发器处于什么状态?

上期答案

2.用或非门组成的基本R-S触发器的特性见表5。(俞鹤飞)