“小天才”(或“任天堂”)家用电视游戏机系统结构框图如图1所示,下面介绍几个主要部分的电路原理。

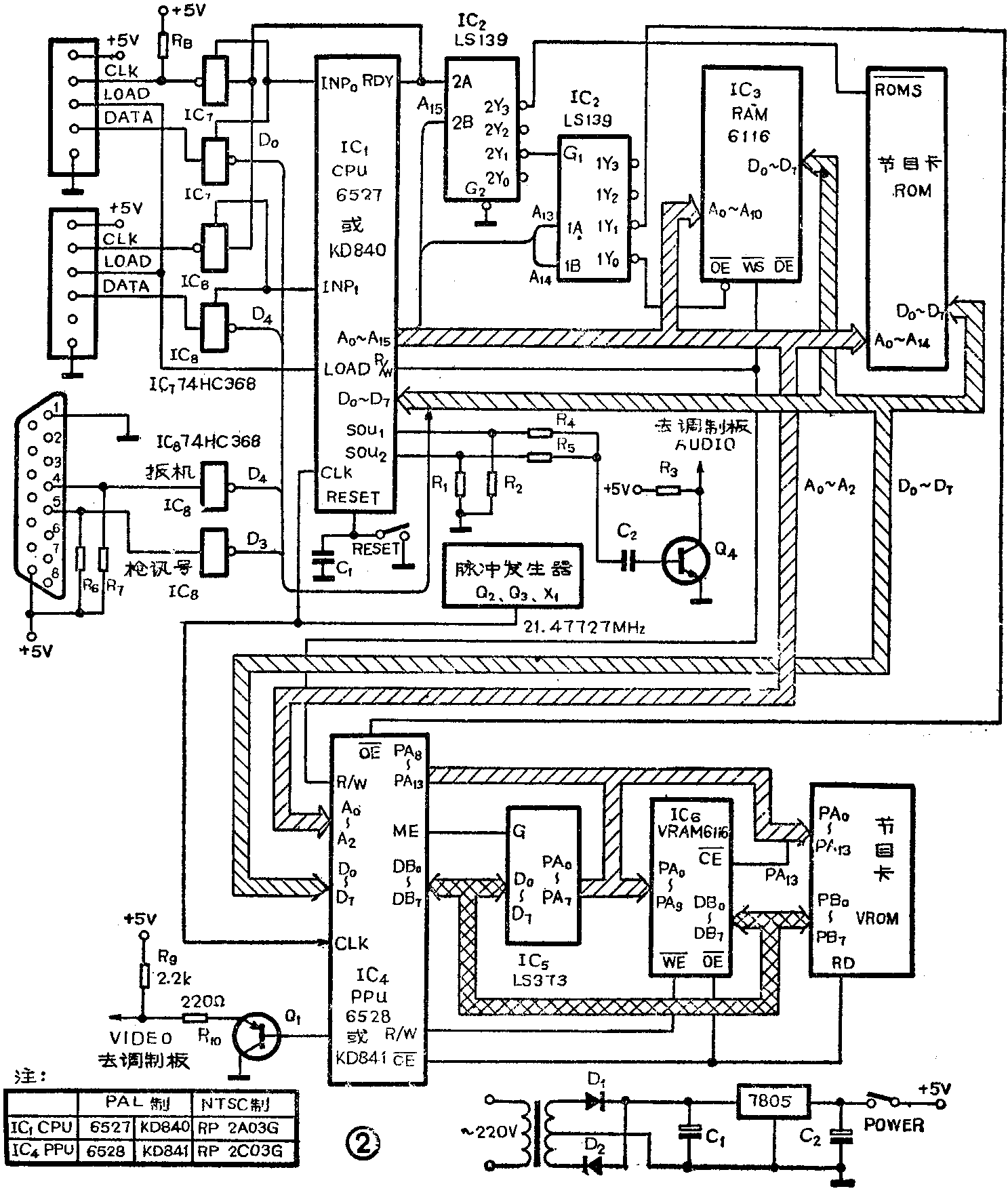

电脑板

1.处理机部分:见图2,三极管Q\(_{2}\)、Q3与晶体X\(_{1}\)组成脉冲发生器,它产生21.47727MHz脉冲,用作CPU中央处理器和PPU视频处理器的时钟。6527CPU为8位单片微型计算机,其地址线A13~15和RDY信号作为IC\(_{2}\)双2线-4线译码器74LS139的输入端。当地址在$8000~$FFFF 32 kB之间(选通RDY为高电平)时,选通节目卡ROM;当地址在$0000~$1FFF 8 kB之间时,IC3RAM有效,现电脑板上RAM只有2KB;当地址在$2000~$3FFF 8 KB之间时,IC\(_{4}\)PPU生效。

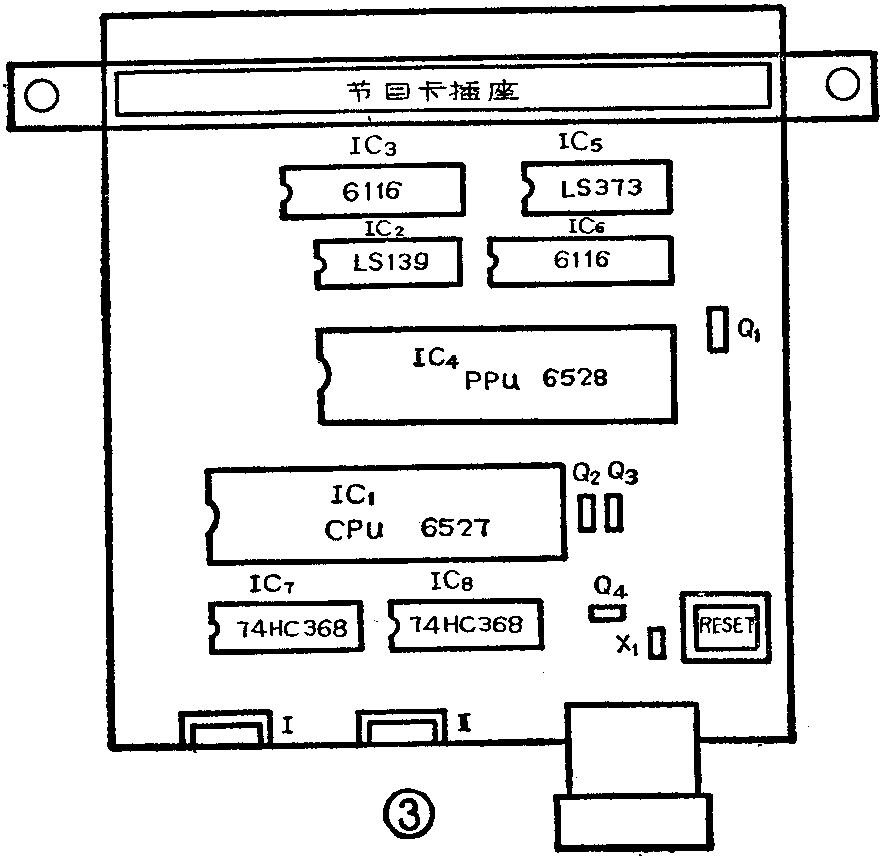

当电脑板接通电源时,主机复位,CPU开始执行节目卡ROM中的游戏监控程序;PAM用来寄存CPU数据;CPU把图象数据送给PPU,由PPU转换为PAL制全电视视频信号;音频(模拟)信号由CPU的SOU\(_{1}\)、SOU2脚输出,经R\(_{4}\)、R5及由Q\(_{4}\)送出音频信号。IC7、IC\(_{8}\)用来接收Ⅰ、Ⅱ控制盒或手枪控制信号,并在INP0、INP\(_{1}\)协调下送到CPU数据端口。图3是电脑板装配略图。

2.图象发生器部分:见图2。视频处理器PPU将CPU送来的图象数据转换成地址信号作VRAM(IC\(_{6}\),视频随机存储器)及VROM(视频只读存储器)的地址信号,由DB0\(_{7}\)8\(_{13}\)送出(DB0\(_{7}\)作输入时,接收VROM送来的数据)。当PPU读写VRAM时,首先PPU的ME变为高电平,此时,DB0\(_{7}\)出现地址信息低8位,地址锁存器74 LS 373(IC5)接收PPU的地址信号低8位,并在ME变为低电平时锁存,这样地址信息低8位便出现在VRAM地址端口上;VRAM的高2位地址PA\(_{8}\)9由PPU\(_{8}\)9给出;PA\(_{13}\)经与门IC9作为VRAM的片选信号,故VRAM选通地址在$0000~$0FFF之间;VRAM的读、写由PPU的R/W及CE-控制。VROM地址为$2000~$3FFF之间,由PPUCE-控制读出;PPU从VROM中读出并行数据,经内部并/串转换,由Q\(_{1}\)驱动输出PAL制全电视视频信号。(待续)(韩永生)