编者按:随着数字化语音处理、合成技术的发展,各种语音处理集成电路相继问世。为在国内推广此新技术,我刊曾于87年10、11两期介绍了一种处理器芯片UM5101,并组织了大奖赛,这一新技术深深地吸引了广大读者。为此,我们再介绍一种更高级的处理器芯片以飨广大读者。

近年来笔者接触过近十种语言处理器芯片,从功能上讲当首推东芝公司的T6668。如果说UM5101以其简练的外电路倍受宠爱的话,那么东芝公司的T6668在功能和性能/价格比上则名列前茅。与各位已知的UM5101相比,T6668的主要优点在于设计时将其外存容量增至1M位,并设有完善的手动控制逻辑及计算机驱动接口。

T6668的功能

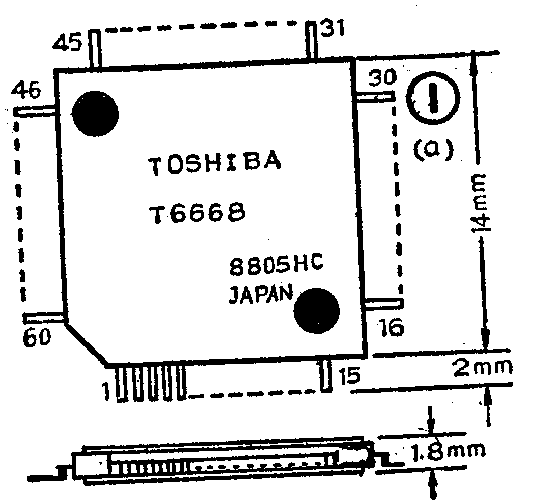

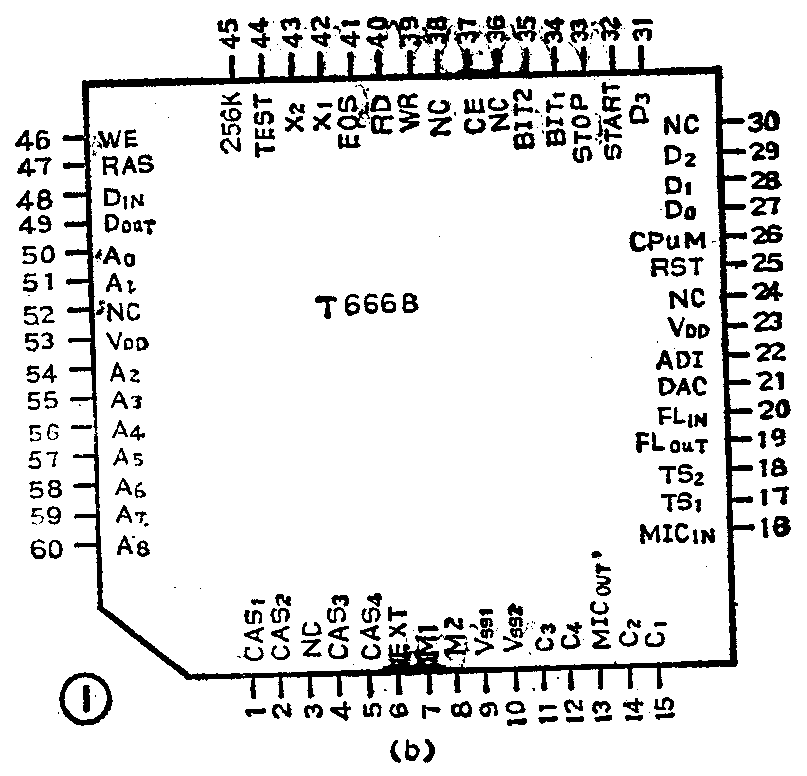

T6668为东芝公司研制,采用标准的60脚扁平塑料封装,图1为它的外型及引脚排列图。图2绘出了其内部功能框图。由图可知,T6668内部主要包括以下功能块:

1.话筒放大器:由CMOS反向器构成,但取消了外接高阻值反馈电阻,简化了外电路设计。

2.ADM分解合成回路、D/A变换器:负责模拟信号的分解和数字信号的合成。采用的语音分解方法为ADM法。

3.时钟、计数器及DRAM接口:为外接存储器提供地址及控制信号。

4.电压跟随器及带通滤波器:数字信号合成时用于提高语音信号的质量,此部分大大减化了外围电路的设计。

5.计算机接口:此部分使得该芯片可直接与CPU联络,无需再外加锁存、控制等芯片,为配接计算机使用创造了条件。

下面按序号详细分析一下T6668各引脚的功能:

CAS\(_{1}\)~CAS4(1、2、4、5脚):第一至第四块存储器的列地址选通信号输出端,依所接DRAM的个数从CAS\(_{1}\)开始依次使用。低电平有效。

EXT(6脚):外接存储器扩展输出端。此端输出T6668内部地址计数器最高位的溢出信号,供扩展外接存储器容量时使用。

M\(_{1}\)、M2(7、8脚):外接DRAM个数编程输入端。当M\(_{1}\)、M2为0、0时,外接一块DRAM,此时只有CAS\(_{1}\)有效。同理,M1、M\(_{2}\)为1、0时,接两块DRAM;为0、1时,三块DRAM工作;为1、1时,四块DRAM全部接入使用。

V\(_{SS1}\)、VSS2(9、10脚):这两脚分别为集成电路内部数字部分和模拟部分的电源地线。

C\(_{3}\)、C4(11、12脚):内部运放用基准电压发生电路去耦电容的连接端。

MIC\(_{out}\)、MICin(13、16脚):内部话筒放大级的输出与输入端。输出端直流电平为1/2电源电压,此脚的输出信号既可以直接送到ADM回路的输入端,也可经RC网络滤波后再送到ADM回路。

C\(_{2}\)、C1(14、15脚):内部话筒放大级的耦合电容连接端。

TS\(_{1}\)、TS2(17、18脚):芯片的测试脚。电路芯片出厂检验时用。

FL\(_{out}\)、FLin(19、20脚):电路内部重放用带通滤波器的输出及输入端子。

DAO(21脚):ADM合成(D/A)电路的模拟输出端。此端经RC网络连至带通滤波器的输入端。

ADI(22脚):ADM分解(A/D)电路的模拟输入端,当直接从此端向ADM回路输入语言信号时,应注意此脚需加1/2电源电压的直流电平,且信号峰值必须限制在1.6V以下。

V\(_{DD}\)(23、53脚):供电电源正输入端,需向此端提供+5V±10%的电源电压。

RST(25脚):复位信号Reset输入端。低电平有效,触发此脚可使电路重新进入初始状态。

CPU(26脚):计算机控制/手动控制选择端。当此脚为高电平时,电路由外部计算机信号控制。此时25、27~40脚均与外接计算机做适当连接构成计算机接口。当此脚是低电平时,电路处于手动控制状态。

D\(_{o}\)~D3(27~31脚):存储器分段选择输入端。通过这4个脚输入的四位BCD控制码,存储器控制电路将把外接存储器划分为16等分来分别工作。这样,通过改变D\(_{o}\)~D3的电平即可分别使用各段存储器进行录放。当D\(_{o}\)~D3各端均悬空时存储器不分段,可连续使用。

START(32脚):起动输入。当从此脚输入20ms以上宽度的正脉冲时,电路开始录放操作。

STOP(33脚):停止输入。当从此端送入20ms以上宽度高电平信号时,电路停止录放。

BIT\(_{1}\)、BIT2(34、35脚):采样比特率选择输入端。根据录音时对音质的不同要求,可通过这两脚来选择采样比特率(录放时间)。当选用640KHz晶振时,BIT\(_{1}\)、BIT2取0、0时为8K;0、1为11K;1、0为16K,1、1为32K。若使用4片41256作存储器时相应的录放时间是128S、98S、65S和35S。

CE(37脚):当电路处于手控状态时,此脚为静噪控制输入端。放音时,若此端接高电平,则DAO端(21脚)无信号输出。但需注意此端在录音状态时必须接低电平。

WR(39脚):手控状态时为录、放音转换端。高电平时为录音状态,低电平是放音状态。

RD(40脚):读输入端。此脚只在计算机控制状态下才使用,用来读取CPU送来的脉冲。

EOS(41脚):结束指示输出端。当电路录放开始时是低电平,录放结束后跳回高电平,用它可驱动工作指示灯,并实现连续录放等功能。

X\(_{1}\)、X2(42、43脚):电路内部晶体振荡器的输入、输出端。

TEST(44脚):测试输入端。正常使用时应悬空。

256K(45脚):存储器型号选择端。当使用64KDRAM4164时,此脚接低电平;使用256KDRAM41256时应接高电平。

WE(46脚):写入脉冲输出端。低电平有效,接存储器。

RAS(47脚):行地址选通信号输出端。低电平有效,接存储器。

D\(_{in}\)、Dout(48、49脚):数据输入、输出端,接存储器。

A\(_{o}\)8(50~60脚):地址输出端,接存储器。

NC(3、24、30、36、38、52脚):空脚。这些端子与电路芯片无连接,可任意处置。

T6668的简单工作过程如下:接通电源后,电路自动处于守候状态。若此时录放音选择端WR置录音状态;D\(_{o}\)~D7均悬空,则输入START端一正脉冲后电路开始“录音”:话筒放大器将捡拾的声音信号放大并送至ADM回路,对信号进行分解(量化)。量化后的数据经地址计数器及控制电路控制,依次存入外接存储器。此种状态一直持续到STOP端得到一高电平脉冲或全部存储器用完为止。录完后,电路将自动进入保持状态,对存储器进行刷新(再生)操作。若WR此时换为放音状态,再触发START端,电路将从各存储器中依次读取信号并经ADM回路及D/A变换器、电压跟随器变换成模拟信号,并经RC网络送入带通滤波器滤波,而后输出到外接功率放大器扩声。(赵九泷)