PC—81微计算机RAM只有2k,难于运行较大程序。能不能通过扩展内存使之能存储较大程序?在这里就介绍一种存储扩展板。

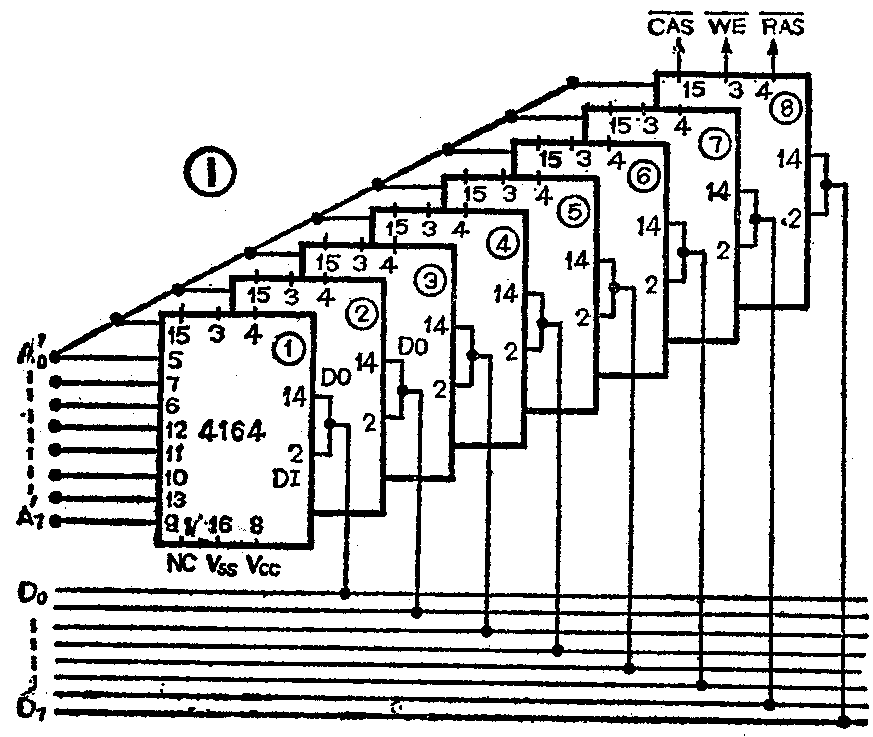

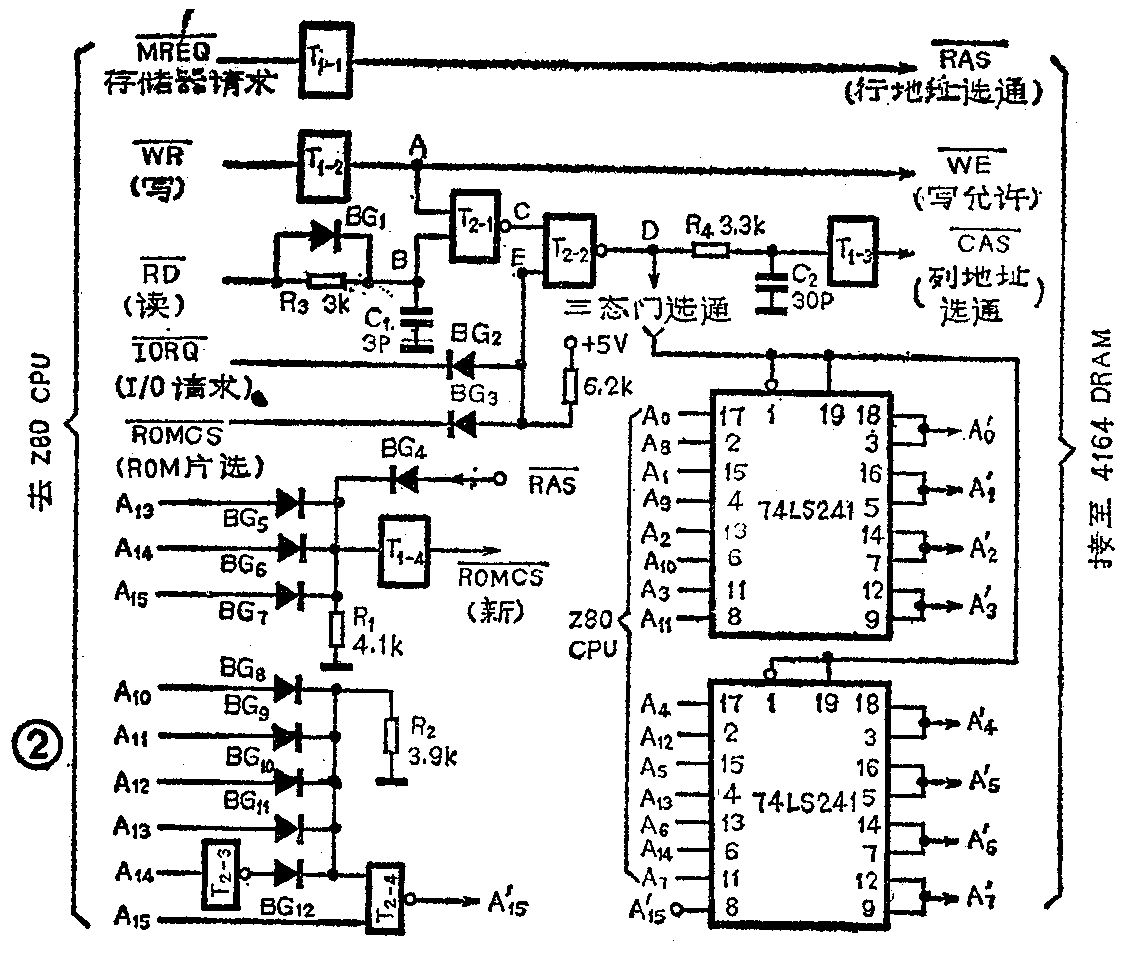

DRAM4164是存储量为64kB×1位的动态随机存储器,在8位机上使用,应将8片4164连成一组,见图1。图中每片4164的数据端都接到相应的数据线上;地址线和控制信号是按图2电路连接到DRAM上的。DRAM4164内部设有行、列地址锁存器,可将分时送入的16位(8行+8列)地址保存起来,以便在选通信号(CAS-,RAS-)到来时,选中某一单元。看图2,我们分析一下CPU是如何对4164DRAM进行读/写操作的。一开始,Z80CPU不发出读(RD-)和写(WR-)信号,WR-、RD-均为高电平,A、B为高电平,C为0,D为1,74LS241允许17、15、13、11脚电平值通过内部三态门送到输出端,即A\(_{0}\)7作为A\(_{0}\)'~A'7输出到动态RAM,注意此时A\(_{0}\)'~A'7并不进入动态RAM的地址锁存器(因RAS-未选通)。CPU读存储器时,首先发出存储器请求(MREQ-=0)信号和读操作RD-=0信号,因MREQ-只经过TH,故RAS-先于CAS-选通,即RAS-=0,原来已浮现在A'\(_{0}\)~A'7端的A\(_{0}\)7信号进入动态RAM的地址锁存器;RD-信号经有延迟和与门作用的R\(_{3}\)、C1和BG\(_{1}\),使B=0,无论A是什么信号C=1,对RAM读操作过程中CPU不会发出IORQ和ROMCS-,故E=1,C,E共同使D=0,D点信号的由高变低,使三态门进行“切换”,列地址(即高八位地址A8\(_{15}\))作为A'0~A'\(_{7}\)输出;D点低电平经R4和C\(_{2}\)延迟再经与门T1—3(匹配作用),使CAS-=0,CAS-选通列地址锁存器;行、列地址都进入了动态RAM便能唯一选中某一单元,此单元数据送入数据总线D\(_{0}\)~D7,CPU进行读操作。我们知道,CPU可对RAM、ROM及I/O接口进行数据传送,为不使数据总线发生冲突,电路设计了BG\(_{2}\),BG3来防止这种冲突,当有ROMCS-=0(或IORQ-=0)信号时,ROM工作(或I/O接工作),使E=0,不论C点出现何值均不影响T\(_{2—2}\)输出0电平,故屏蔽了CPU对RAM的读/写操作。

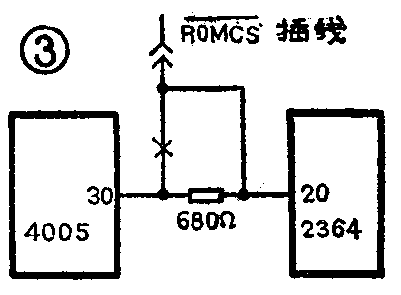

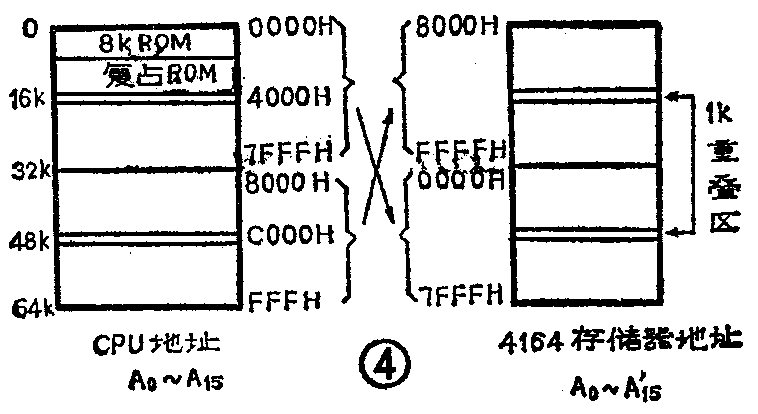

图3是对图4所示的PC—81机8kROM重复占用16k地址空间的改进电路图,加装了BG\(_{4}\)~BG7(见图2)及T\(_{1—4}\)所产生的ROMCS-(新)信号,接图3所示端后,又增加了8kB自由RAM空间。这部分空间除接受PEEK和POKE指令外,拒绝其它BASIC命令的管理。

由于PC—81的BASIC解释程序最大只能管理32kBRAM,故还需对内存做如下安排,才能启动BASIC解释程序。具体做法是引入A'\(_{15}\),产生如图3b所示的1kB重叠区(请自行验证)。

开机正常后,可键入测试程序,它会给出存储出错数,若显示存储有差错,可反复调整CAS-延迟电容,直到消除差错。(凡需文中测试程序者,请汇0.40元向四川省重庆邮电学院电子协会张曹勇邮购。)(张曹勇)