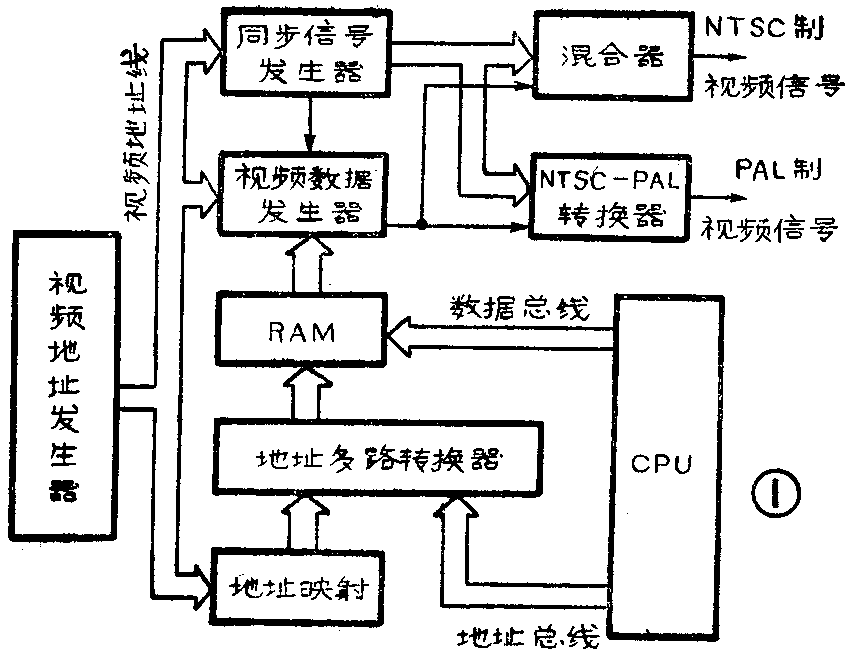

图1是XMF-I型机的视频显示系统结构框图。图中有一块RAM作为资料存储区,亦称显示缓冲区。对显示缓冲区中的资料,CPU可以自由访问,而视频显示系统则以严格的次序读出其内容并送往屏幕。为了使这两方面不致形成冲突,对RAM的访问是分时的:在φ\(_{0}\)期间,CPU占有RAM;在φ1期间,视频系统占有RAM。这个分时工作由地址多路转接器来完成。

在视频系统访问RAM时,系统读出的资料含有文字信息与图象信息。文字信息以ASCII码表示,图象信息由数据在内存中的位置及其本身特点综合表示。这些信息经过视频数据发生器后,变成串行脉冲,再与同步信号发生器产生的行、场图步信号混合,成为显示设备能够接受的视频信号输出。

显示模式及屏幕软开关

由于显示缓冲区内包含的信息形式的不同,就形成了五种不同的显示模式:(1)文本模式;(2)低分辨率图形模式;(3)高分辨率图形模式;(4)文本与低分辨率图形混合模式;(5)文本与高分辨率图形混合模式。

1.文本模式:允许屏幕显示24行、40列字符。每个字符占用显示缓冲区的一个单元。显示缓冲区共有两部分:$400~$7FF部分称为第一页;$800~$BFF称为第二页。

2.低分辨图形模式:允许屏幕显示1920个色块,每行40个色块,共48色块高。它所占的显示缓冲区与文本模式完全一样,不同之处仅在显示方式上:文本模式将每个缓冲区单元的内容以字符形式显示,而低分率模式将每个单元显示成上下相邻的两个色块,该单元的低四位确定上边色块的颜色,而高四位确定下边色块的颜色。

3.高分辨图形模式:允许屏幕显示53760个色点,一行有280个点,共192行。每个色点占显示缓冲区内的一位(bit),每七点占用一个单元(bit0~bit6,bit7另有作用),因此,整个缓冲区共占7680个缓冲单元,地址安排:第一页$2000~$3FFF;第二页$4000~$5FFF;第三页$6000~$7FFF;第四页$8000~$9FFF。

在每个缓冲单元中,bit0~bit6这6个点从左到右显示,bit7不显示,但这一位与显示点在屏幕上的位置共同决定了该点的颜色。当 bit7=0时,若该字节中某点位于屏幕上的奇数列,则该点为绿色;若为偶数列,则为紫色。当bit7=1时,奇数列的点为橙色;偶数列的点为蓝色。若显示点的值为0,则为黑色(不显示)。若相邻两点都为1(显示),则两点都显示成白色。列的奇偶性是这样定义的,屏幕最左边为第0列,最右边为第279列。

4.混合显示模式:混合显示模式是将屏幕分为上、下两部分,下面四行文本区供文本显示模式,上部与低分辨或高分辨显示模式相同。

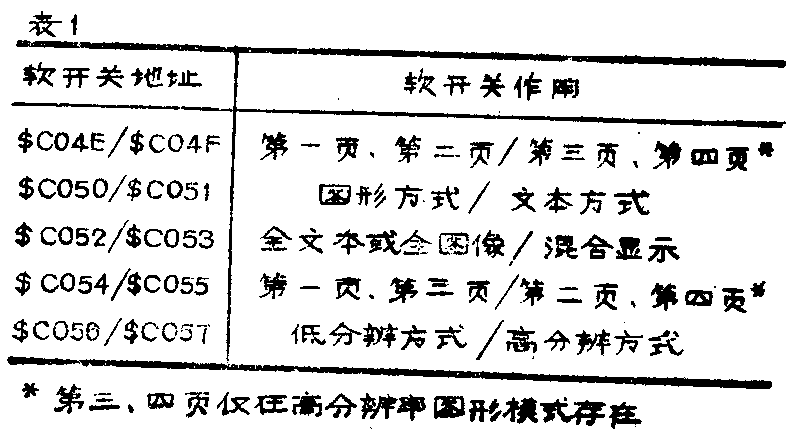

显示模式之间的转换通过软开关管理,软开关地址及作用见表1。对表中五个软开关进行组合,即可得到所需的显示状态。例如,要进入高分辨率全图形模式第四页,可设置软开关$C057、$C052、$C055、$C05F、$C050,依次对它们进行读、写操作即可。

视频地址发生器

前面已经谈到,为了将显示缓冲区的内容送往屏幕,视频显示系统要以一定次序读出缓冲区内容。这项工作由视频地址发生器及地址映射部分来完成。

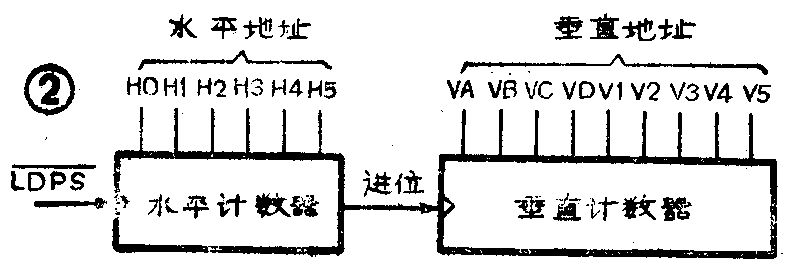

视频地址发生器结构见图2。它分为水平地址产生与垂直地址产生两部分。其中水平地址的一个周期相当于显示器上的一个行周期,而一个垂直地址周期对应显示器的一个场周期。由于没有采用隔行扫描的方式,故它的一个场周期就相当于一个帧周期。

水平地址是对LDPS-脉冲进行计数,LDPS-的平均周期约为0.98μs,共计65次,产生64μs的行周期。由于计数器内部的反馈,“0”被计数两次,因此水平地址被最后计成0~63,由HO~H5共6条水平地址线输出。

垂直地址是对水平周期进行计数的,一个垂直周期应为312个水平周期(场颇为50Hz)或262个水平周期(场频为60Hz)。这是通过改变预置数达到的。当计数计到511(111111111)时、计数器进入预置状态,下一次计数脉冲到来时,若计数器被置成200(011001000),则计数为200~511,共312个水平周期;若置成250,则为262个水平周期。垂直地址由VA~VC及V0~V5共计九根地址线输出。这样,最后得到的视频地址共有15位。

由于15位地址可寻址32k字节,而显式模式中,高分辨率图形也仅需7680字节(192×40),这就出现了浪费。造成这种浪费的主要原因在于消隐期间出现的视频地址是不显示的。为此有必要压缩视频地址的范围,具体措施是:(1)V5去掉不要,因为若取显示状态下垂直计数范围为256~447(共192行),则V5始终为1;(2)把剩下的14根地址线组合成13根,这样就使寻址范围减少到8192字节。组合后的13根地址线为H0~H2、Σ0~Σ3、V0~V2、VA~VC。其中Σ0~Σ3由H3~H5、V3及V4组合而来,其表达式为Σ0=V3+H3+1,进位=CO;Σ1=H4+V4+CO,进位=C1;Σ2=H3+H5-+C1,进位=C2;Σ3=H5-+V4+C2,进位不用。

地址多路转接与视频地址映射

在φ\(_{0}\)期间,CPU占有RAM,此时RAM的地址线应接在系统地址总线上;在φ1期间,视频系统占有RAM,此时RAM地址线应接在视频地址线上。

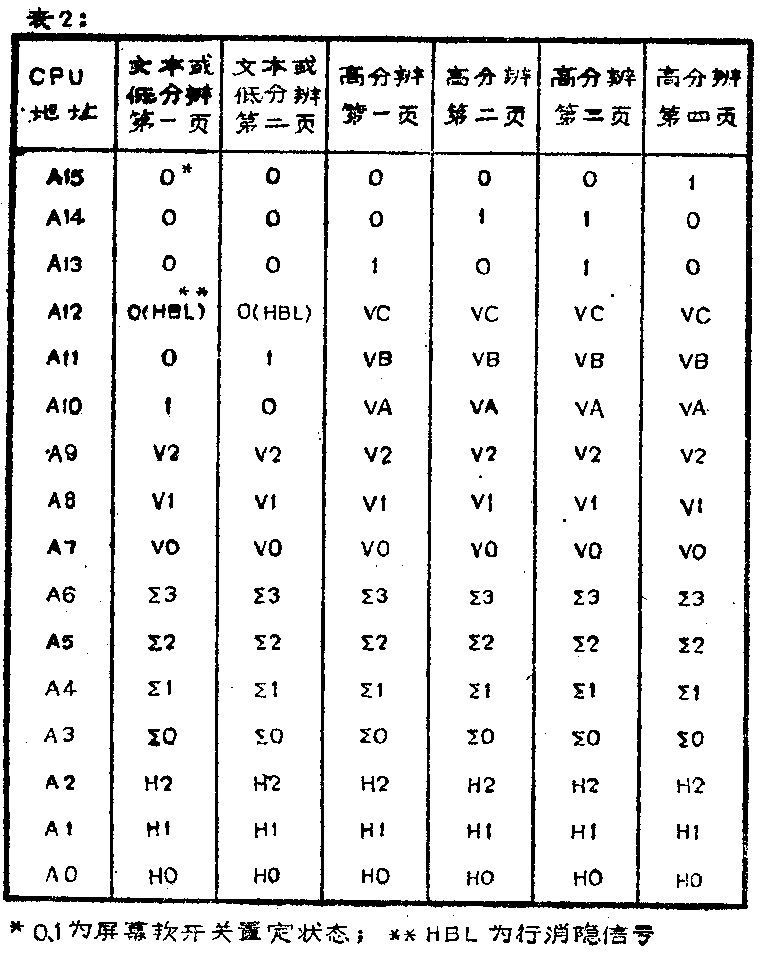

由于RAM地址线分时接通CPU或视频地址线,因此视频地址与CPU地址有一对应关系,即视频地址映射,这个映射关系见表2。

视频信号产生电路

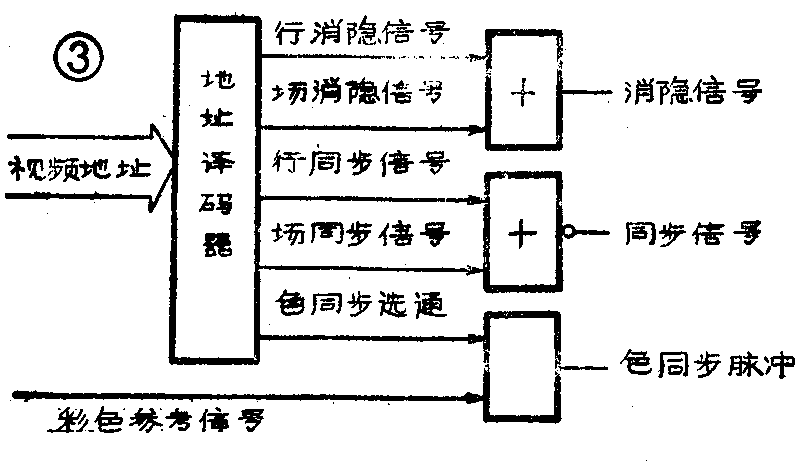

视频信号产生电路可分为同步信号与消隐信号发生电路及视频数据信号发生电路。同步信号中包含了行、场同步脉冲及色同步信号,视频数据信号中包含了亮度与色度信号。

1.同步与消隐信号发生电路 本电路的框图如图3。由前述可知,水平地址范围为0~63,其中需要显示的地址为40个,其余均为消隐期。故消隐期定为0~23共25个计数,24~63这40个计数为显示期。由此可见,行消隐信号HBL只是将水平地址0~23译码出来而已,其逻辑表达式为HBL=H3·H4+H5-。同样,垂直地址范围(200~511或250~511)中的显示部分为256~447,行消隐信号分为两段,一段为200~255(50Hz),另一段为448~511。由于不考虑V5,后一段可认为是192~255,故只需将192~255译码出来就形成场消隐信号,其逻辑表达式为VBL=V3·V4。将HBL与VBL进行逻辑或即得到总的消隐信号。

根据上述,可以得到同步信号的逻辑表达式:

色同步选通脉冲:HBL·H4·H2-,对应的水平计数为16~19,脉冲宽度约4μs。

行同步脉冲:HBL· H3-,对应的水平计数为8~15,脉冲宽度约8μs。(未完待续)(陈光梦)