1973年,中东战火骤起。埃及利用苏制萨姆导弹击落了一批批以色列飞机。于是美国迅即向以运送了一批最新式武器,其中的灵巧炸弹制导系统采用了美国贝尔实验室刚刚在1970年发明的一种新型半导体器件——电荷耦合器件(Charge-Coupled Devices,CCD)。这也许是CCD第一次在国际舞台上“亮相”。

时至今日,CCD以其独特的功能在摄象、模拟信号处理和数字存储等领域发挥着日益重要的作用。除了MOS和双极型这两类器件和集成电路,CCD可能是最重要一类半导体器件。CCD不仅在军事和高科技方面有重要应用,而且已开始进入日常生活。SONY的TV摄象机以及Canon的自调焦相机都以CCD作为关键部件。不久的将来,彩电将不仅能调节彩色鲜艳度,还能分别调节三基色的相对强度,这个新功能也是利用了CCD。

一、CCD的基本工作原理

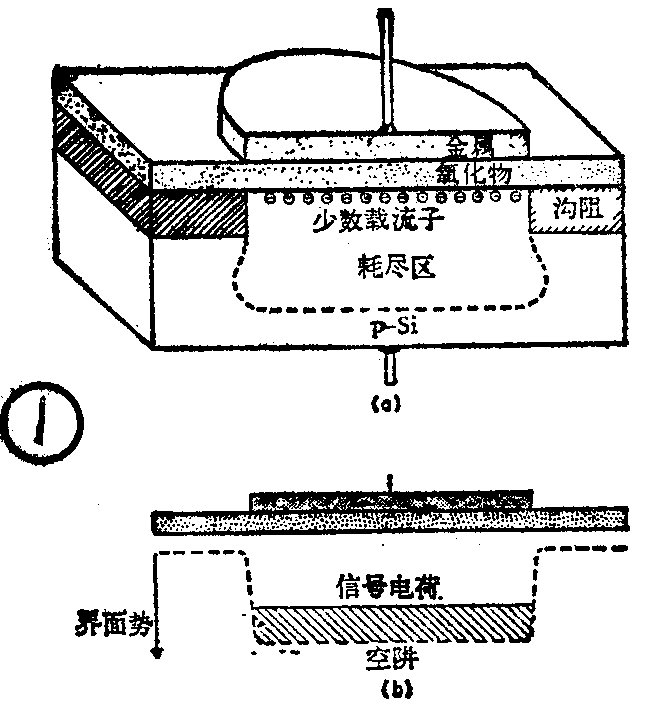

组成CCD的基本单元是MOS(金属—氧化物—半导体)电容器,如图1所示,(a)为MOS电容器剖面图;(b)为有信号电荷的势阱。金属电极称为栅,也可以用掺杂多晶硅制成。二氧化硅氧化物起电介质的作用。MOS电容器的下极板不是一般导体,而是半导体。

所有电容器都能存储电荷,MOS电容器也不例外,但是方式有所不同。假定所用半导体是P型硅,其中空穴比电子多。如果在栅上加一个正的栅电压(衬底接地),靠近SiO\(_{2}\)的硅表面层中,带正电的空穴将遭排斥,或者说被耗尽。而对于电子,正栅压将把它们吸引到Si-SiO2界面处,因为那里的电子势能较低。我们形象化地说: 半导体表面形成了势阱,使电子陷落在阱内。通常称这里为一电荷包。

与其它半导体器件相比较,CCD最突出的特点在于它以电荷作为信号,而不是以电流或电压作为信号。因此,掌握CCD工作原理的关键是理解电荷怎样在CCD内进行转移或传输。

CCD的最基本结构是彼此非常靠近的一系列MOS电容器。这些电容器用同一半导体衬底制成,衬底上面生长均匀、连续的氧化层,在氧化层上制作相互绝缘的数目不等的金属化电极(栅极)。相邻电极之间只相隔极小的距离,这是保证相邻的势阱耦合和电荷能够转移的基本条件。

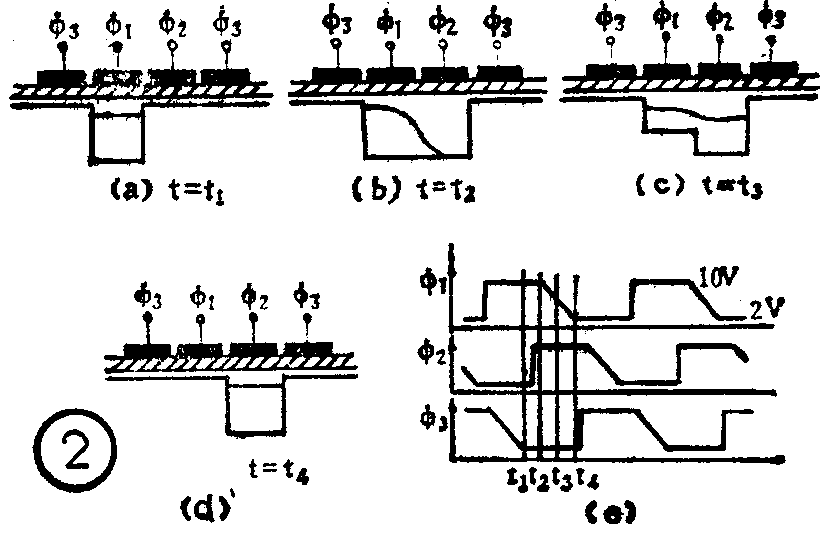

现在我们具体说明电荷如何从一个栅极下面转移到相邻栅极下面。我们以图2(三相CCD中势阱耦合和电荷包运动)中的四个电极为例,分别对它加驱动脉冲(或者叫做时钟脉冲)φ\(_{1}\)—φ2—φ\(_{3}\)—φ1。驱动脉冲φ\(_{1}\)、φ2、φ\(_{3}\)的形状完全相同,只是彼此之间有一定的相位差,如图2(e)所示。图中脉冲的低电平为2伏,要求大于开启电压,相当于在场效应器件中形成沟道所需的条件。高电平为10伏。

在时刻t=t\(_{1}\),φ1处于高电平,φ\(_{2}\)和φ3处于低电平,因此在φ\(_{1}\)电极下Si-SiO2界面处出现势阱,陷入了电子,如图2(a)所示。接着φ\(_{2}\)电压上升,到了时刻t=t2,φ\(_{2}\)也处于高电平,于是φ1和φ\(_{2}\)电极下Si-SiO2界面处都有势阱。由于电极间隙很小,φ\(_{1}\)和φ2 下面的势阱互相连通,形成一个大势阱,于是原来在φ\(_{1}\)势阱中的电子向φ2方向转移,如图2(b)所示。接着,φ\(_{1}\)电压开始下降,下面的势阱相应地变浅,到了时刻t=t3,有更多的电子转移到φ\(_{2}\)下面势阱内,如图2(c)所示。

在时刻t=t\(_{4}\),φ1 电压已经下降到2伏,φ\(_{1}\)势阱消失,只有φ2电极下面还有势阱,而原来在φ\(_{1}\)势阱内的电子几乎全部转移到了φ2势阱内,如图2(d)所示。

这样,在驱动脉冲的控制下,势阱的位置可以作定向移动,信号电荷也随之转移。上面我们解释了信号电荷从φ\(_{1}\)电极转移到φ2电极的过程。只要驱动脉冲加在电极上,信号电荷还将从φ\(_{2}\)电极转移到φ3电极,再转移到下一个φ\(_{1}\)电极。

在实际的CCD中,转移电极很多。我们将电极加以编号,把第1、4、7……个电极并联,加驱动脉冲φ\(_{1}\);把第2、5、8……个电极并联,加驱动脉冲φ2;把第3、6、9……个电极并联,加驱动脉冲φ\(_{3}\)。假定在起始时刻,第1、4、7……个电极,即φ1相电极下有数量不等的信号电荷,那么,在驱动脉冲作用下,这些电荷同步地向φ\(_{2}\)相电极转移,第1电极下的电荷向第2电极转移,第4电极下的电荷向第5电极转移,如此等等。接着,这些电荷分别转移到φ3相各电极下。经过驱动脉冲的一个周期,这些电荷又进入到φ\(_{1}\)相电极下,但每包电荷都向前转移了,第1电极下的电荷进到第4电极,第4电极下的电荷进到第7电极……。

我们把分别加脉冲φ\(_{1}\)、φ2和φ\(_{3}\)的相邻三个MOS电容器作为构成CCD的一个基本单元,或者叫做一“位”。显然,单元数或位数越多,CCD的规模越大,工艺难度也就越大。这种用三组彼此有相位差的时钟脉冲驱动的器件叫做三相CCD。常见的还有二相和四相CCD,它们分别用彼此有一定相位差的两组和四组时钟脉冲驱动,每个单元(每位)分别有两个和四个栅极。

我们在上面曾经指出,电极间隙必须很小,以保证相邻的势阱连通,这样电荷才能不受阻碍地进行转移。电荷耦合器件中的“耦合”一词,就是指相邻势阱完全连通。显然,如果电极间隙比较大,间隙处下方的电势不能由栅极电压控制,相邻势阱不能完全耦合,例如间隙下方的势阱底部出现一个“小丘”,它将阻止电荷全部转移,于是器件便无法正常工作。对于图2所示的CCD结构,电极间隙通常应该小于3μm。一般情况下,1μm的间隙可以保证耦合条件。

二、各种类型的CCD

电荷耦合器件种类繁多,它们具有不同的工艺流程,性能差别很大,因而用途也各不相同。一个CCD的结构,包括它的电极结构,信号转移沟道,电输入结构和信号检测结构,以及产生为CCD工作所需的时钟脉冲发生器等外围电路。下面我们对此作一简单介绍。

1、电极结构:CCD的衬底一般采用轻掺杂的硅,例如电阻率10\(^{3}\)Ωm左右。氧化层厚度通常为0.1μm左右。根据驱动脉冲的相数不同,常见CCD有二相、三相和四相之分,下面对每种相数的CCD介绍若干典型的电极结构。

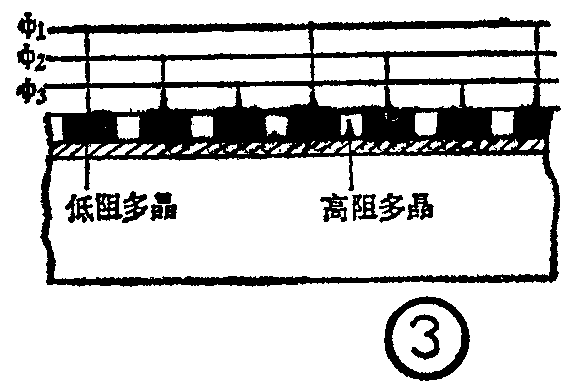

(1)三相电阻海结构:最早制成的CCD是采用如图2所示的单层铝电极结构。它的主要缺点是电极间隙处氧化物直接裸露在周围气氛中,使得下方界面电势变得不稳定,影响转移效率。此外,电极间隙很窄,对于规模较大的器件,光刻工艺有相当大的难度。因此,实用CCD不采用三相单层铝电极结构。三相电阻海结构避免了这些缺点,如图3所示。在氧化层上淀积一层连续的高阻多晶硅,然后对电极区域进行选择掺杂,形成三相电极图案。所需的引线和焊点都在附加一层铝上形成。这种电极结构的成品率高、性能稳定,不易受环境气氛影响。它的缺点是每个单元的尺寸较大。

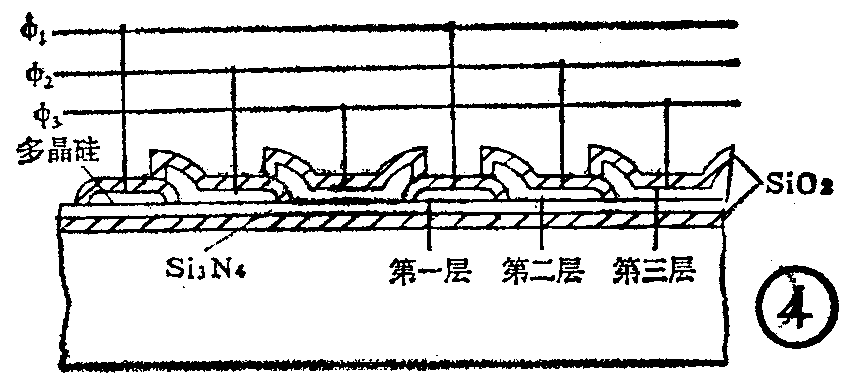

(2)三相交叠硅栅结构:这种电极结构利用三层多晶硅,如图4所示。它的特点是,电极间隙仅为电极间氧化层的厚度,只有几百纳米(10\(^{-9}\)m);而且单元尺寸小,沟道又是封闭式的,因而被广泛采用。它的主要问题是高温工序较多,而且必须防止层间短路。

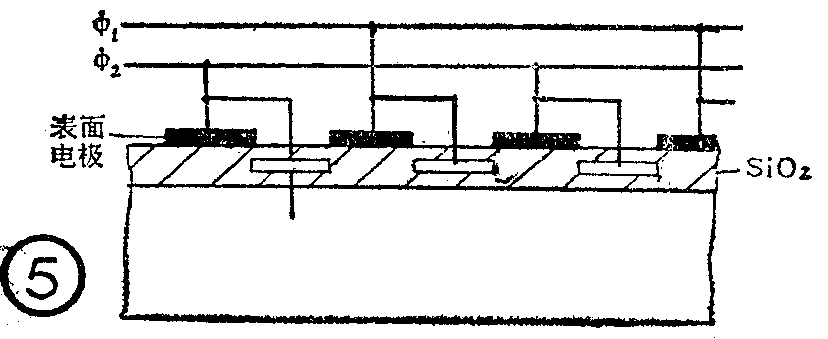

(3)二相硅—铝交叠栅结构:这种电极结构的第一层电极采用低电阻率多晶硅,第二层电极采用金属铝。两层栅极下绝缘层厚度不同,如图5所示。

二相CCD的优点是驱动脉冲比较简单,在相同的工艺水平下,布线比较简单,所需芯片面积较小。它的不足之处是每个单元所能容纳的信号电荷量比较少。

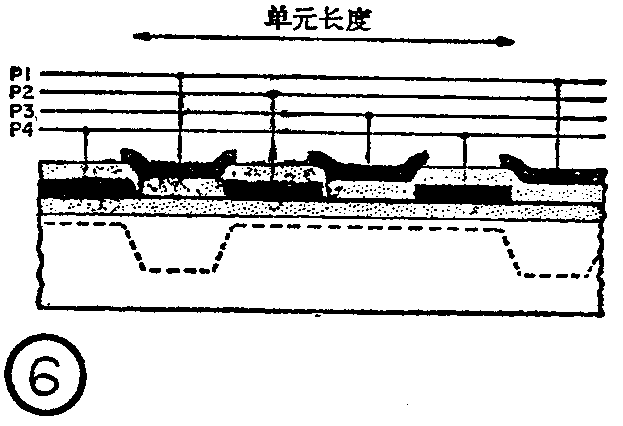

(4)四相CCD:采用两次金属化的电极结构,如果所有电极面积大致相等,栅绝缘层厚度也基本相同,以致所有电极的电荷存储能力相差无几,则可以用四相方式操作。例如,图6是两层金属(例如钼),中间用100纳米厚度的淀积二氧化硅绝缘。

2、信号转移沟道:信号电荷在半导体中转移时,是贴着界面运动,还是离开界面一段距离呢?信号电荷的位置取决于它们的电势能,总是在势能最小处。如果是在均匀掺杂的衬底上直接制造CCD,那么在Si-SiO\(_{2}\)界面处势能最小,信号电荷在界面层内运动。这种器件称为表面沟道CCD(SCCD)。

在SCCD中,由于界面处存在陷阱,信号电荷在转移过程中将受到影响,从而降低转移效率和工作速度。为此,可以在衬底内用离子注入方法改变势能最小值的位置,使信号电荷不是贴着界面而是在衬底体内运动,从而避免了界面陷阱的问题。信号转移沟道在体内的器件称为体内沟道CCD或埋沟CCD(BCCD)。

此外,与MOS器件一样,作为信号电荷的少数载流子可以是电子或空穴,于是,CCD的沟道也有n型的或p型的。一般地说,在大致相同的条件下,n沟CCD的性能比p沟CCD的性能好,其主要原因是电子迁移率比空穴迁移率要大,二者在体内大约相差三倍左右。表面迁移率与表面具体情况有关,但是在类似条件下也是电子迁移率比空穴迁移率大几倍。因此, 目前以n型沟道CCD居多,SCCD用p型Si作衬底,BCCD也用p型Si作衬底,再附加n型离子注入表面层。

三、CCD的基本性能

CCD象所有其它半导体器件一样, 具有由器件物 理过程决定的性能极限。但是,CCD具有自己的独特功能,因而具有不同于其它器件的性能参量。

1、信号处理能力:信号处理能力Qmax是CCD能够存储和处理的最大信号电荷量,对于以电荷作为信号的器件来说,无疑是重要的性能参量。信号处理能力基本上由转移电极面积、绝缘物厚度、时钟脉冲幅度、相数和波形等因素决定。 对于栅电极长度为10μm、沟道宽度为20μm、栅极氧化层厚度为0.1μm的典型器件,当用幅度为10V的时钟脉冲操作时,信号处理能力约为6×10\(^{-}\)11库仑,或者说大约3.7×106个电子。这对于大多数应用来说是足够的。如果时钟频率为1MHz,信号电流约为0.6μA。可以通过增加电极面积,减小氧化层厚度和提高时钟脉冲幅度来提高器件的信号处理能力,从而得到较高的信噪比。但是,在一定的条件下,通过改变这些参量来增大输出信号是有限度的。增加电极面积会导致器件成品率和集成度的降低,氧化层厚度受工艺条件和其它因素的制约,时钟脉冲幅度则受到雪崩倍增等效应的限制,不能超过一定限度。

应该指出,在BCCD中,由于信号电荷离开界面有一段距离,相当于绝缘层电容减小,因而信号处理能力将降低。

2、转移效率:CCD的最重要性能就是使电荷所代表的信息在转移过程中不受损失的能力。电荷在CCD中自一个势阱向下一个势阱的转移过程,既不是瞬时的,也不是完全的。为了描述不完全转移的效应,引入转移效率的概念。一个CCD在定时钟频率下的转移效率η定义为一个电荷包中的电荷量在一次转移中被转移的百分比。

应用CCD时,如果有必要,可以设法降低因界面陷阱或体内陷阱对载流子的俘获而引起的转移损失。具体作法是用一个偏置电荷,或者说“胖零”,预先填满空陷阱,这样,当载流子通过时就不会被俘获,从而降低了转移损失率。当然,这会占去一部分信号处理能力。

3.噪声:CCD中存在许多噪声源。噪声叠加在信号电荷上,降低了电荷包所代表的信息复原的精度,并因此而对CCD信号电荷包规定了一个下限。

(1)转移噪声:电荷转移和损失的过程是一种随机过程,转移损失具有随机涨落,于是电荷包也带上了随机涨落,造成了噪声。一个电荷包N\(_{s}\)在N次转移后的噪声等效电子Nn=\(\sqrt{2εNN}\)\(_{s}\)例如,对于三相100单元的SCCD,若ε=10\(^{-4}\),Ns=104至10\(^{6}\),则自由转移噪声约为25至250个电子。

而界面态(假定面密度为N\(_{ss}\))引起的电子数方均根涨落为Nts=(1.4KTN\(_{ss}\)NA)\(^{1/2}\)A为电极面积,K为玻耳兹曼常数。

(2)电输入噪声和输出噪声

输入信号和检测的方法很多,噪声各不相同。这里仅提出理想电输入和检测方法的噪声下限:

N\(_{n}\)≈400\(\sqrt{C}\)EQ〔PF〕

C\(_{EQ}\)是输入或检测结构的等效电容,以皮法(PF)为单位。CEQ的典型值为1(PF),噪声等效电子约为400。实际的输入、输出方法引起的噪声都高于这个数值。(王以铭)