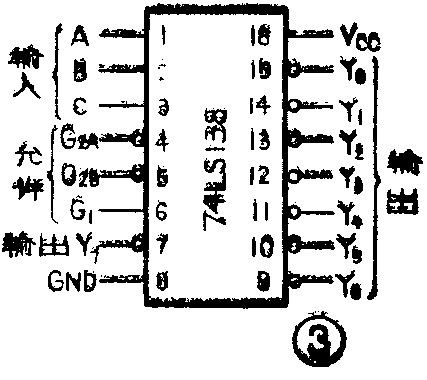

小蜜蜂-I(XMF-I)系统中的I/O接口分为极上 1/O接口和扩充I/O接口插槽两部分。板上I/O接口有收录机I/O接口、游戏棒I/O接口、扬声器接口、键盘接口、打印机接口、监视器接口、电视机接口。汉字系统接口和I/O接口插槽等。扩展I/O接口插槽设在扩展箱内,扩展箱内还设有驱动器及其接口和与APPLE-Ⅱ相兼容的扩展插槽4个。图1是XMF-I系统的I/O接口示意图。

I/O接口地址分配

XMF-l型机分配给I/O接口的地址为$C000~$CFFF,共4k地址,

1.主机板上的接口地址:为了与APPLE-Ⅱ系列机兼容,XMF-1(和CEC-I)型机主机板上I/O接口地址与APP-LE-Ⅱ I/O接口地址相一致,在$C000~$C07F128个地址中安排了14种I/O接口或软开关地址码,地址安排如下:

(1)键盘数据输入接口:接口地址码在$C000~$C00F之间,该地址码由地址译码器译出。键盘读入计算机主机的选通信号为地址码$C00×,它形成上一讲图9中的KB-信号。

(2)清键盘选通接口:接口地址码在$C010~$C01F之间,它用作控制信号,当地址为这16个地址中的任一个时,地址译码器便输出一个地址选通脉冲。使键盘选通寄存器清零 表示键码已被CPU取走。所以清键盘操作是在读键盘代码操作之后进行的,键盘清零信号为上一讲图9中的CLRSTB-信号。

(3)收录机转存输出接口:接口地址码在$C020~$C02F之间,当地址为这16个地址码中的任一个时,地址译码器便输出一个选通脉冲,作为一个触发器的计数触发脉冲,地址译码器每发一个选通脉冲,触发器就翻转一次。

(4)扬声器接口:接口地址码为$C030~$C03F,当地址为这16个地址码中的任一个时,地址译码器便输出一个地址选通脉冲,触发一个触发器,使输出端信号翻转,经功率放大器后接到扬声器上发声。

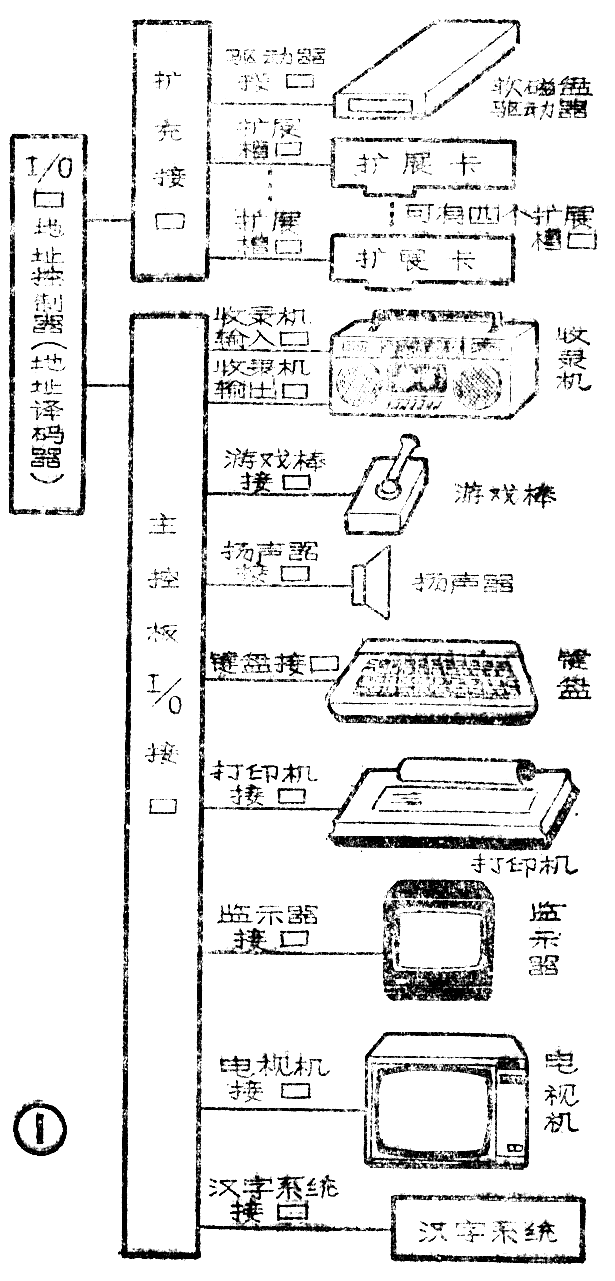

(5)游戏棒接口:游戏棒通过一个16腿插座与主机相接,16腿插座引腿定义见图2(其中NC为空脚)。其中SW\(_{0}\)~SW2是从游戏棒接口插座送往主机的三个开头信号,接口地址码为$C061~$C063;STB-为实用脉冲输出信号,地址码为$C040~$C04F;PDL\(_{0}\)~PDL3是从游戏棒插座送往主机的模拟信号,接口地址码为$C064~$C067;AN\(_{0}\)~AN3是从主机送到游戏机控制器的开关指示信号,地址码为$C058~$C05F。

(6)收录机转存输入接口:接口地址码为$C060,收到这个地址后,计算机从收录机调入文件程序。

(7)CRT监示器控制软件:CRT监示器显示方式有文本、低分辨率图形显示、高分辨率图形显示和混合方式显示等。显示工作方式的选择是通过接口地址码进行的,CRT显示工作方式选择“软开关”的地址码为$C050~$C057,共8个软开关(详细内容在视频显示系统部分介绍)。

XMF-I系统对软开关功能进行了扩充。在$C041~$404F之间的部分地址码被用作特殊功能的软开头。其中$C04F选择第3、4图形页;$C04E选择第1、2图形页;$C04D~$C04A为27256ROM的选体软开关信号。

2.扩展接口地址:扩展接口地址设置在$C080~$CFFF之间、主要有扩展插槽地址(I/OSEL信号)、各个插槽数据、状态信息进出的16个接口地址( I/O DEV-信号)及七个扩展插槽公用的智能控制程序地址(2k)空间。

(1)接口插槽地址:系统可供使用的插槽有七个、其地址码为$C1××~$C7××。每个接口插槽有256个地址单元;作为接口智能控制程序使用。在XMF-I系统中,打印机、汉字系统及软益驱动器等占据了其中的$C1××、$C5××及$C6××,故留给用户使用的有四个接口插槽地址码为$C2××、$C3××、$C4××和$C7××,其地址码选通信号I/O SEL-($C1××~$C7××)分别接到每个对应插槽的1号引腿。而0号扩展插槽的$C0××则被用作RAM由48k扩充到64k的控制信息(地址码)。系统的每个扩展接口插槽都拥有16个地址码,为接口插槽提供数据出入接口的地址,这些地址为$C08×~$COF×,统称为I/O DEV-,分别接对应扩展插槽的41引腿。

(3)公用智能控制程序区:系统规定地址$C800~$CFFF2k空间为智能控制程序可扩展空间,每个扩展插槽都可占用这个空间。当一个扩展插槽被选中时,该2k空间将自动接入系统,同时其它扩展插槽被封堵住。调用该扩展空间的地址为$C8××~$CF××,选通信号是I/O STB-。

地址译码

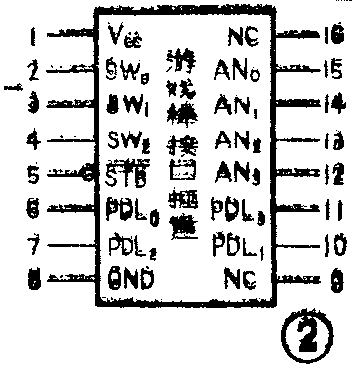

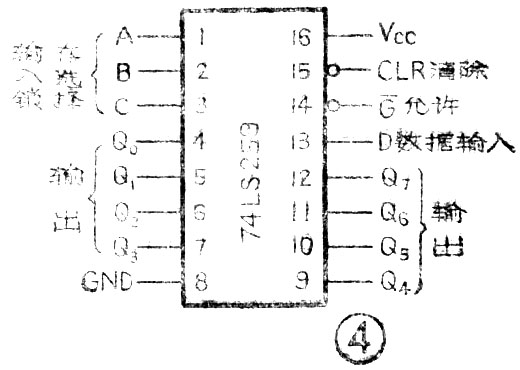

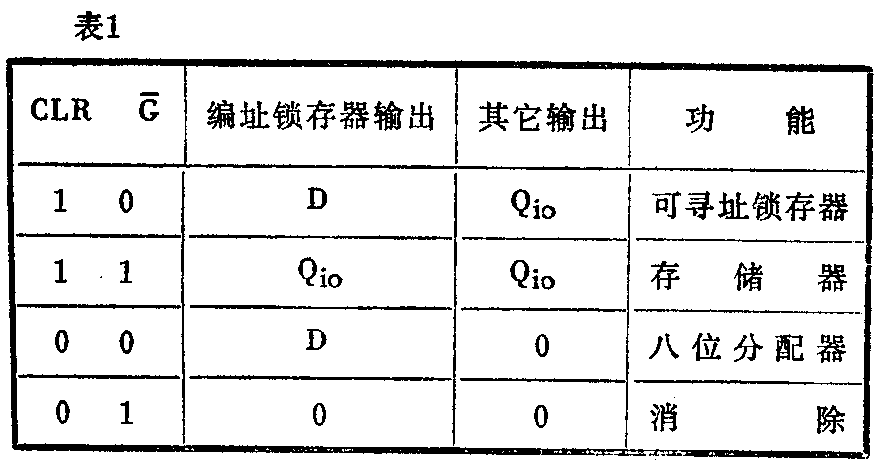

1.地址译码器74LS138和锁存器74LS259:上述各种地址码主要由译码器74LS138和74LS259译码实现的。74LS138引腿功能见图3,其中输入端A、B和C接地址位,G2A、G2B和G1是片选允许端,Y\(_{0}\)~Y7是输出端,低电平有效。74LS259是八位可寻扯锁存器(见图4),其输出电平由数据输入端D的电平确定。当D为低电平时,选中的输出端为低电平;反之,为高电平。输入端CBA从000到111的八种排列选定0~7号编址锁存器。Q\(_{0}\)~Q7的输出电平随输入数据电平而定。G-为片选允许端,与CLR(清除)信号组成表1所示的组合功能。

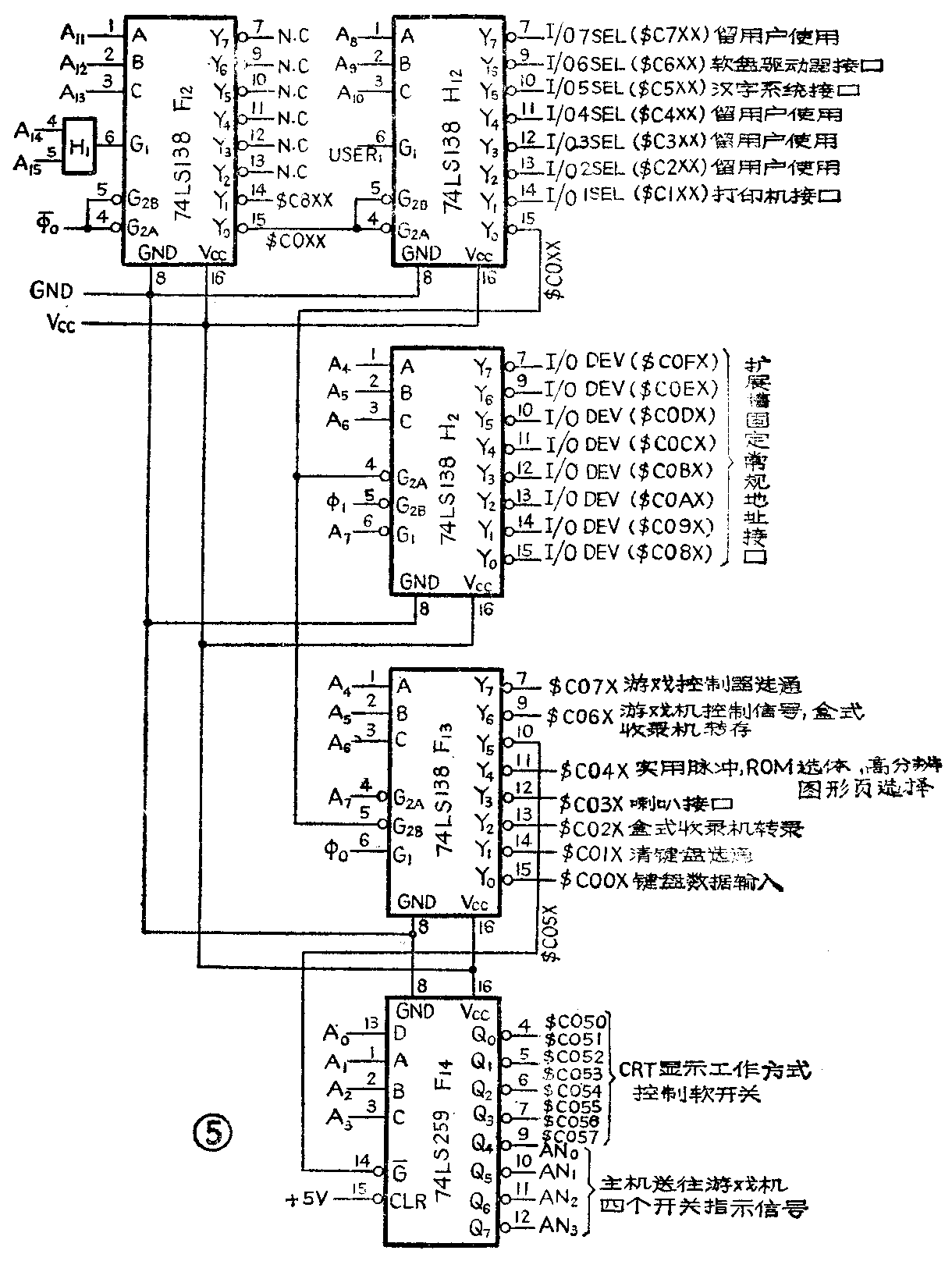

2.地址译码电路:地址译码分五级进行:译出$C0××和$C8××;译出$C1××~$C7××;译出$C08×~$C0F×;$C00×~$C07×:$C050~$C05F。电路见图5。

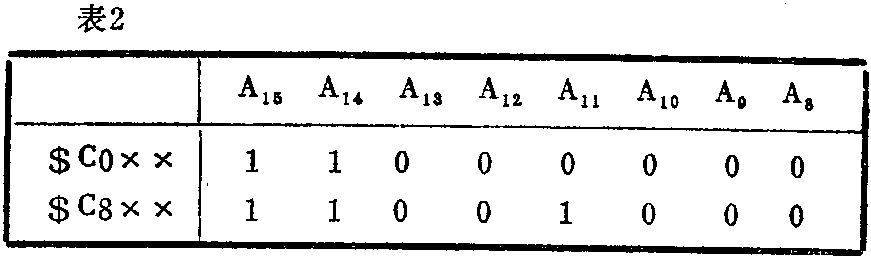

(1)第一级地址译码:用作译码器的F\(_{12}\)是74LS138三一八译码器,译出的地址码为$C0××和$C8××(-I/O STB)。因此只使用了8个输出端中的二个Y0和Y\(_{1}\)。分析上述二个地址码高8位真值,见表2。从真值关系可知,高8位中只有最高5位A15\(_{ll}\)是有关地址位。A15\(_{12}\)必须为1100(16进制C),A11位的变化可保证译出“0”或“8”,所以要求A\(_{15}\)14必须为“1”。电路中使用了A\(_{15}\)14作为“与”门H\(_{1}\)的2个输入端(4、5引腿),只有当A15\(_{14}\)同为“1”时,H1的输出端(6引腿)才为“1”。H\(_{1}\)的6输出端接到F12的G1端,作为片选信号;A\(_{13}\)12\(_{11}\)分别接入译码器选择端,当A13\(_{12}\)11为000码时,选中输出端Y\(_{0}\)呈低电平状态,此时F12的整体地址码A\(_{15}\)14\(_{13}\)12\(_{11}\)10\(_{9}\)8为11000000,即$C0××。当A\(_{13}\)A12A\(_{11}\)为001时,选中输出端Y1呈低电平状态,此时A\(_{15}\)14\(_{13}\)12\(_{11}\)10\(_{9}\)8为11001000,即$C8××,直接接入外设扩展插槽20引腿。F\(_{12}\)器件其它输出端以(Y7~Y\(_{2}\))未用。F12的G\(_{2A}\),G2B片选端要求低电平有效,由于CPU访问存储器在φ--\(_{0}\)的负半周进行,因此将φ--0接入G\(_{2A}\)和G2B。

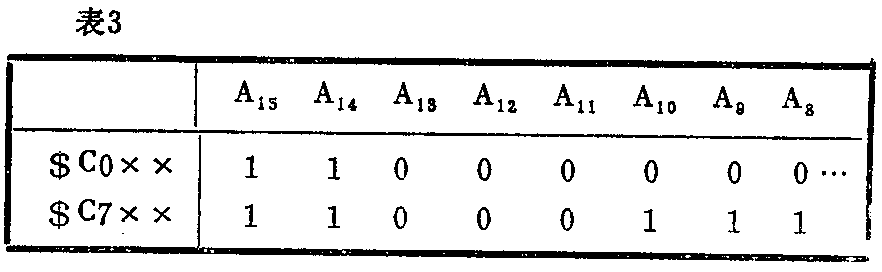

(2)第二级译码:第二级译码采用H\(_{12}\)器件(74LS138)作为译码器。第二级将译出外设7个扩展插槽的地址码$C1××~$C7××。分析高8位真值关系见表3。从真值关系可以看出地址码的最高5位是相同的,正是第一级译码Y0输出端$C0××码,电路中将它接入H\(_{12}\)的4、5端G2A,G\(_{2B}\),作为片选信号,H12的另一片选端(6脚)G\(_{1}\),由外设扩展插槽送来USER1片选控制信号,要求高电平选中。若不使用USER1信号,通常H12的6脚G\(_{1}\)接+5V。H12的地址选择端A、B和C分别接入A\(_{8}\)9\(_{1}\)0,从真值关系可知,A8\(_{9}\)10不同码的变化,将得到$C1××~$C7××的不同地址码。

(3)第三级译码:第三级译码采用H\(_{2}\)器件(74LS138)作为译码器。要求该级译出扩展插槽固定的常规地址接口$C08×~$C0F×。分析其高12位地址真值关系,高8位为$C0××,可从第二级译码器H12的15脚输出端Y\(_{0}\)得到。A7\(_{6}\)5\(_{4}\)的真值关系为1000($C08×)~1111($COF。)。认真值关系分析,要求A7必须为“1”,因此将A\(_{7}\)作为片迷信号,接入H2的6脚C\(_{1}\)端;从第二级译出的$C0××Y0端,输出选中时为低电平,作为H\(_{2}\)的另一个片选信号,接H2的4脚G\(_{2A}\)端。H2的5脚G\(_{2B}\)片选端接φ1,当其为低半周时为H2提供片选选中条件(低电平)。选择端A、B、C,接地址线A\(_{4}\)5\(_{6}\),由A4\(_{5}\)6地址码的变化,将在Y\(_{0}\)~Y7输出端得到$C08×~$C0F×。

(4)第四级译码:第四级译码采用F\(_{13}\)器件(74LS138)作为译码器,要求译出主控板上I/O接口$C00×~$C07×。其译码原理分析与第三级基本相同。最主要的区别是第四级片选端F13的4脚接A\(_{7}\),而且要求A7必须是“0”时,才是选中F13器件工作的条件之一,F\(_{13}\)片选另一端F13-5G\(_{2B}\)接$C0××,选中时为低电平,F13的6脚G\(_{1}\)接φ0,在正半周时输入给G\(_{1}\)高电平,上述三个条件同时满足时,F13才能被选中。F\(_{13}\)地址码选择端A、B、C接A4\(_{5}\)6。输出端Y\(_{0}\)~Y7将输出地址码$C00×~$C07×。

(5)第五级译码:第五级译码采用F\(_{14}\)器件(74LS2598位可寻址锁存器)作为译码器,要该级译出$C050~$C05F16个地址码。根据74LS259器件工作条件,片选端F14的G-应送入低电平,因此该端接第四级Y\(_{5}\)输出端(F13的10引腿)$C05×,F\(_{14}\)-15CLR端接+5V。若使$C050~$C05F产生16种地址码,要用4位地址码,其低4位A3 A\(_{2}\) A1A\(_{0}\)真值关系为0000~1111。分析地址真值关系可知A3\(_{2}\)1,共有8种地址码变化(000~111),而每种地址码变化将由于A\(_{0}\)位的不同值,产生2个不同的地址码,所以在逻辑电路中将A0作为输入数据接入F\(_{14}\)的D端,A1\(_{2}\)3作为地址码选择信号接入F\(_{14}\)的选择端A,B,C,8条输出线Q0~Q\(_{7}\)每一条线,将随着A0的不同值,而得到2个不同的地址码,即$C050~$C05F共8组。

收录机接口电路

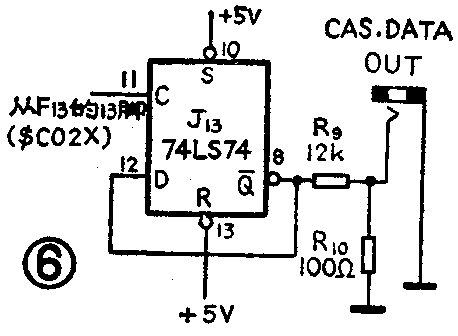

1.输出接口:收录机转录输出接口电路由触发器J\(_{13}\)和分压电路(R9,R\(_{1}\)0),及盒式机数据输出插口(CAS DATA-OUT)组成,如图6所示。触发器J13被置成计数状态,将输出端Q-J\(_{13}\)的8脚接分压器的同时反馈接入触发器数据输入端DJ13的12脚,时钟端J\(_{13}\)的11脚接收录机转录地址码$C02×,该信号由图5的F13的13引腿送来,利用其上升沿使输出端翻转。置位端S(J\(_{13}\)的10脚)和清除端R(J13的13脚)分别接+5V。(待续)(乌振声)