目前,CMOS集成门电路在电子仪器中的应用越来越多,如何简便、准确地判断这些集成门电路的好坏,是广大业余无线电爱好者关心的问题,在这里我向大家介绍一种测试门电路的一个简单装置。

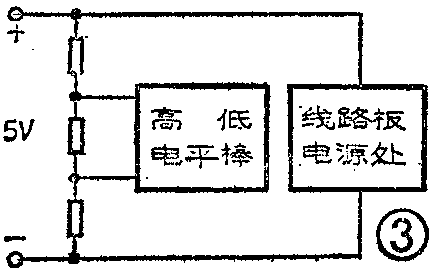

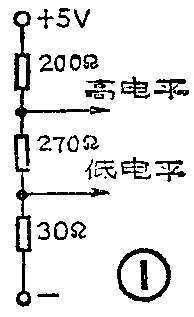

大家知道,在门电路中,当电平大于2.4V时即为高电平。当电平低于0.4V时则为低电平。我们以最常用的5V电源为例,取三只电阻,阻值各为200Ω、270Ω、30Ω,将它们依次串联起来接于5V电源的正负两端,见图1。并引出作为低电平引出线(此处对地为0.3V),以及作为高电平引出线(此处对地为3V),再将两高、低电平引线焊接于两条稍粗的铜线的上端,见图2。将这两条铜线用绝缘管套套好,(最好高、低电平管套用不同颜色加以区别)。其下端稍露作为电平输出触头,然后把这两条套有绝缘套管的铜线绑在一起,(注意高、低电平线不得相碰),这样,高、低电平信号输出棒就做好了。

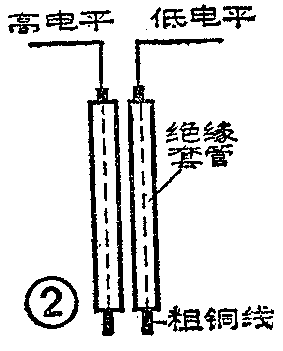

测试时,最好将电路板取下,电路板与自制的高、低电平棒同用一组电源,见图3。将所需的高或低电平加至门电路的输入端,(视需要而定)。最好使用数字万用表的直流电压档测试输出端的电压,看输出端是否符合该门电路的要求。这样就可以准确地判断此块CMOS集成门电路的好坏。(王一明)