存储器是计算机中的重要功能部件,负责存储信息数据。

衡量计算机的性能时,往往把存储量多少,存储器体积大小、工作速度快慢和价格高低当作重要的性能指标,一般总是希望容量大、体积小、速度快且造价低。

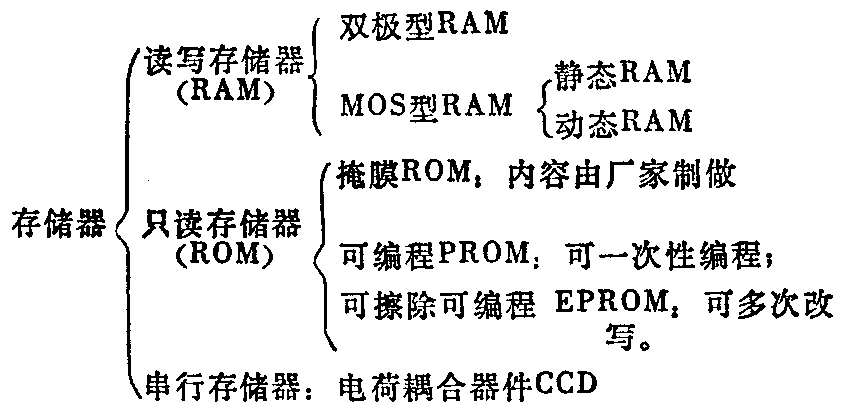

自40年代计算机诞生以来,从最早的磁芯存储器发展到现在的半导体存储器,计算机的存储器已经经历了几代变化。现在的半导体存储器可以做到在一个25mm\(^{2}\)硅片上有64k×1或64k×4存储单元,工作速度达到100ns~200ns之间,有的甚至可达到50ns、20ns。半导体存储器分类如下:

中华学习机中用到了MOS型RAM和可擦除可编程EPROM存储器。

系统内存地址的分配

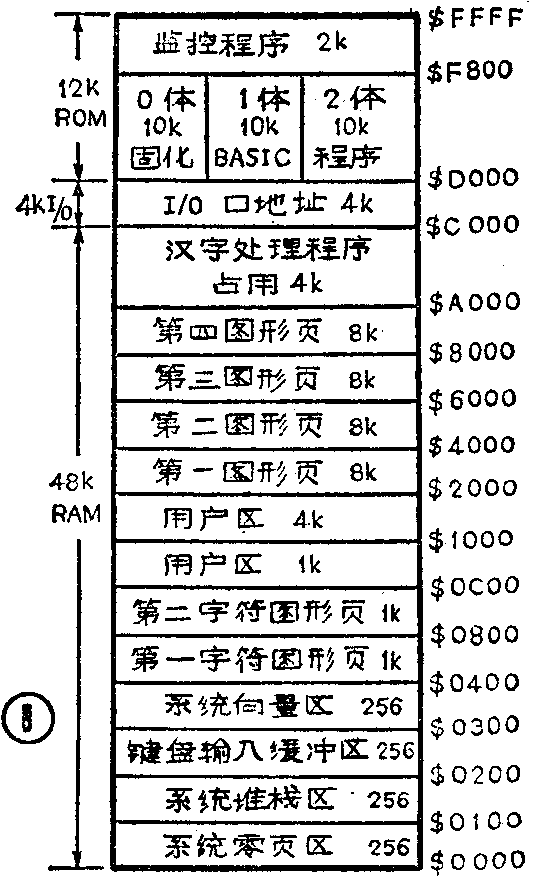

65SC02 CPU地址线有16条,可直接寻址64k(65536个单元),每个单元可存放一个二进制数据,称为一“位”,每八个单元数据构成完整的八位数据,称为一个“字节”。 64k存储空间分配见图1,随机读写存储区48k,地址$OOOO~$BFFF;I/O口地址区4k,地址$COOO~$CFFF;只读存储区ROM12k,地址$DOOO~$FFFF。地址具体分配是:

1.地址分配:48k、RAM空间按每256个字节为一个地址页划分,共有192个地址页。系统中有些地址页为专用区,如系统零页区、堆栈区、键盘数据输入缓冲区、系统向量区和汉字处理区等。另外,由于系统没有另设专用的显示刷新存储区,所以在这48k RAM中为字符、图形显示开辟了专用区,即低分辨字符图形页和高分辨图形页。系统规定在系统时钟φ\(_{0}\)正半周为CPU访问RAM时间,负半周为CRT访问RAM时间。

由于65SCO2CPU指令中没有专门访问I/O口的指令,因此系统给每个外设I/O口编上内存地址,安排在48kRAM区$COOO~$CFFF这4k空间,作为板上收录机输出/输入口、键盘数据输入口。键盘清零口、扬声器口、汉字口、打印机口、扩展槽口及系统软开关等口地址区。

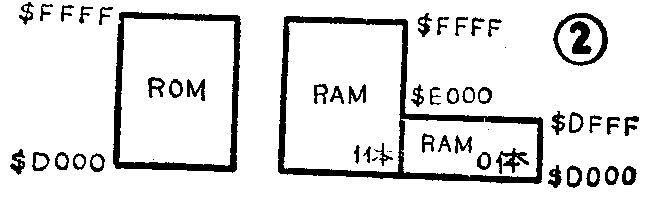

ROM区共有12k空间,地址$DOOO~$FFFF,其中监控程序占据最高地址位2k空间$F800~$FFFF见图2,余下的10k空间用作BASIC语言程序固化,地址在$DOOO~$F7FF。

2.RAM的扩充:当使用磁盘操作系统DOS3.3时,已固化的监控程序将脱开运行不起作用,固化的BASIC编译程序也可不用,可在DOS3.3支持下,由软盘调入所需的BASIC编译程序。这样就可以将$DOOO~$FFFF12k 原ROM空间让出来,用来增设16kRAM。如何将16kRAM安排在12k空间呢?解决的办法是将两个扩充区(4k0体扩充区和12k1体扩充区)叠放在原ROM区的起始地址处,即0体$DOOO~$DFFF,1体地址$DOOO~$FFFF(见图2),可以看出0作与1体扩充区有4k重叠,为使其地址重叠而内容不重,我们仍用软开关进行选体切换,以达到扩充16kRAM的目的。扩充地址分配见图3。

动态读写存储器4164

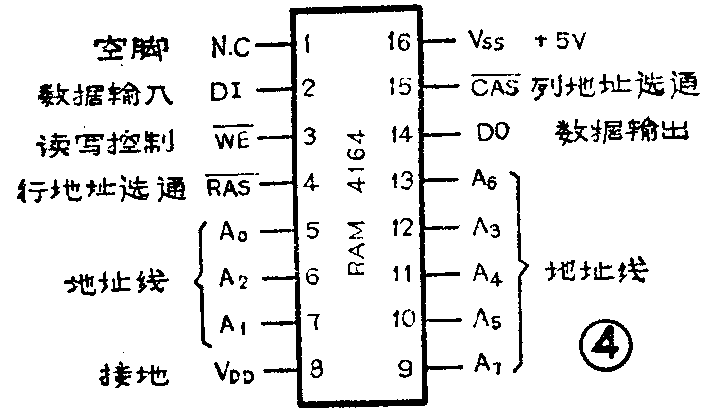

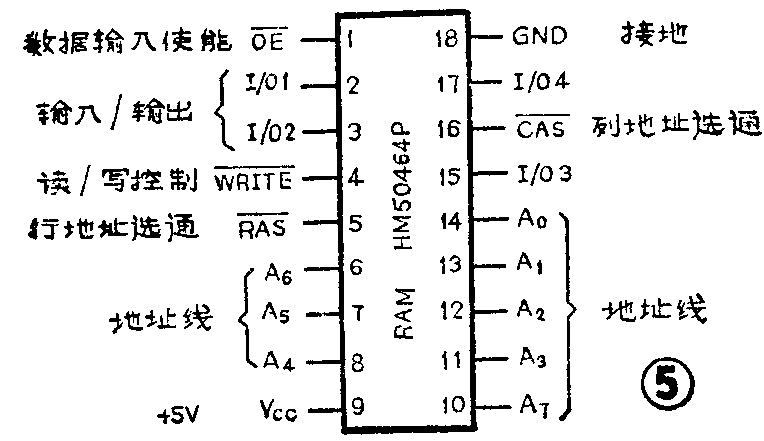

“XMF—I”机中用的动态读写存储器RAM4164是64k×1存储器,见图4,“XMF—I”中共用了八片;而在“CEC—I”机中用的是二片HM50464型64k×4存储器,见图5。

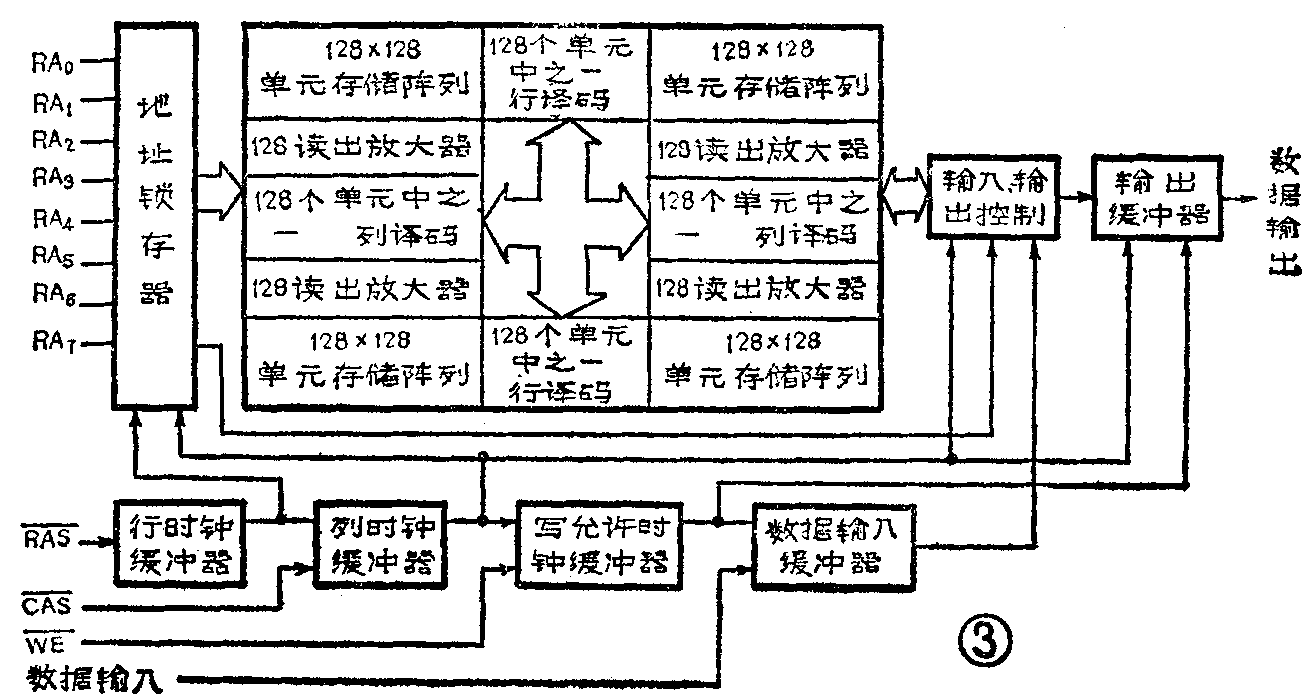

动态RAM4164的工作原理框图如图3所示,存储器有四个工作区,每个区有16384位(16k)空间,由128×128行列矩阵组成。每128个行地址设有一个行地址译码器。共有两个行地址译码器,同样256个列地址设有两个128列地址译码器。在每个工作区的数据输出输设有128个读出放大器。16位地址分为行、列两组地址,在行地址选通信号RAS-和列地址选通信号CAS-作用下,分时从RA\(_{0}\)7送入存储器中。写入数据到4164时,写控制信号WE-为低电平,写入允许时钟缓冲器发出控制信号,封住数据输出缓冲器,输入的数据经数据输入缓冲器进人存储器输入输出控制器,然后进入选定单元;读出数据时,在WE-为高电平条件下,等到时钟缓冲器发出控制信号,打开数据输出缓冲器,数据经存储器输入输出控制器送入数据输出缓冲器,最后送往系统数据总线。

动态存储器要求每2ms内必须将内容刷新一次,否则会使存储信息丢失。

动态RAM4164在系统中起着将键盘输入的字符存入键盘缓冲区、与CPU交换数据、为CRT开辟显示刷新区、存放字符和图形信息等作用。因此存储器要保证与上述各功能部件连通,4164与系统的连接主要有以下几个方面:

1.行、列地址转换电路。由门阵列器件GA\(_{4}\)的22、21、19、18、17、167的30、31引线输出RA\(_{0}\)7行、列复用地址能够有效代表A\(_{0}\)15地址,并能保证在φ\(_{0}\)正半周内送抵动态RAM4164;在φ0负半周时,CRT访问存储器所需要相应的地址参数是H\(_{0}\)H1H\(_{2}\)H3H\(_{4}\)H5V\(_{0}\)V1V\(_{2}\)V3V\(_{4}\)V5V\(_{A}\)VBPAGE 2 HIRES(有关水平和垂直计数后将专门介绍),这些参数也是经GA\(_{4}\)7转换为行、列地址的,并保证在φ\(_{0}\)负半周期间送到RAM地址端。

2.行、列地址选通信号RAS-、CAS-。这两个信号分别由时序发生电路中的器件Z\(_{42}\)(74LS195)的15和13引线输出。RAS-经35ns延迟后,直接接到RAM的RAS-;CAS-送入门阵列器件CA8进行处理,以保证在RAM 48k和扩展16k范围内都能使列选通有效,超出此范围列选无效,RAM所需的列选通信号CAS-是经GA\(_{8}\)逻辑转换后输出的。

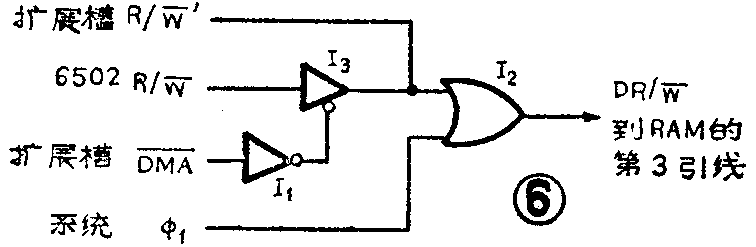

3.读写控制信号DR/W-的产生。图6为产生DR/W-的逻辑电路,当DMA-操作无效(高电平)时,CPU R/W-通道被打开,它经驱动门I\(_{3}\)形成R/W-'信号,R/W-'被同时送往扩展槽和或门I2,它在φ\(_{1}\)(φ0)负半周形成DR/W-,作为存储器读写控制信号。当D-MA有效时,I\(_{2}\)被封堵,此时由DMA-控制器DMAC沿着R/W-通道送出R/M-信号,在φ1负半周形成DR/W-'信号,使外设同存储器打交道。该逻辑电路已做在GA\(_{8}\)中。

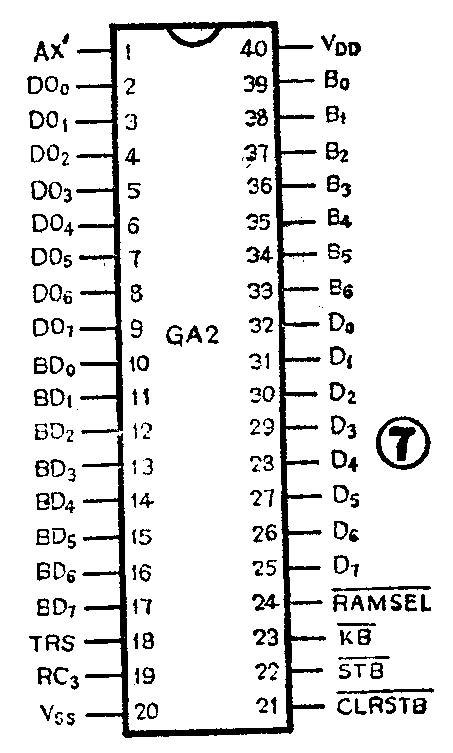

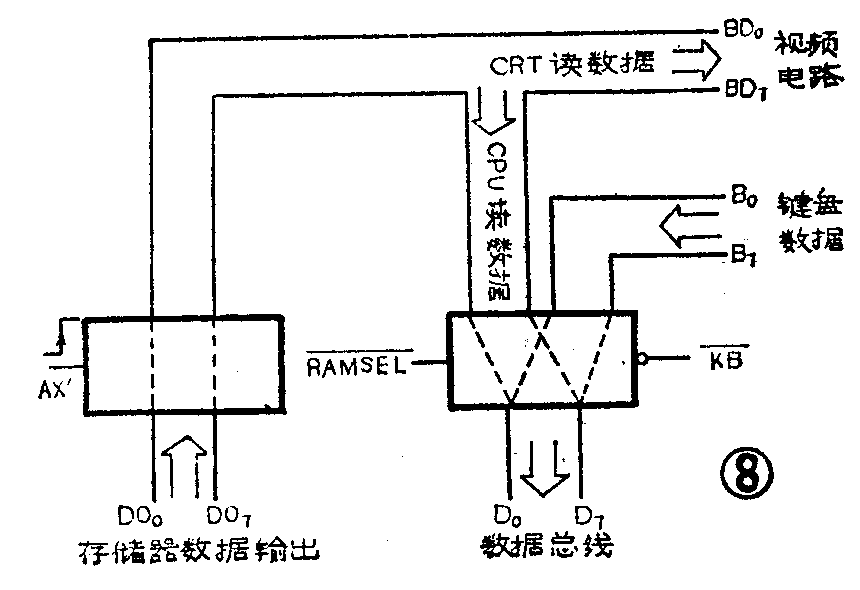

4.门阵列器件GA\(_{2}\)简介。门阵列器件是采用大规模集成技术(LSI)专门为用户设计制做的一种专用集成电路。GA2 在存储器系统中起着多路数据转换开关的作用。GA\(_{2}\)的各引出脚如图7所示。图中有四组数据线,其中键盘数据线B0\(_{6}\)共七条,最高位B7可由键盘选通信号STB-(22)在有键码读入时,在内部使B\(_{7}\)=1因此,GA2外部不必设B\(_{7}\)端。键盘数据通道由控制信号KB-(23)和RAMSEL-(24)组成的逻辑信号进行控制(见图8),当KB-=0、RAMSEL-=0时,将键盘字符码送入数据线D0~D\(_{7}\),存入RAM键盘输入缓冲区。(待续)(乌振声)