为了借鉴国际上较成功的经验,中华学习机如“XMF-1”、“CEC—1”等机型的中央处理器采用的是65SC02CPU,或与其兼容的6502CPU。6502CPU属6500系列中的产品,由美国ROCK—WELL公司生产,主要用于APPLEⅡ、ATARI及BBC等微型计算机上。6502CPU与65SC02CPU引脚功能完全兼容,其区别仅在于制作工艺不同,前者为硅栅NMOS结构,后者硅栅CMOS结构。本文主要介绍65SC02CPU,如不加说明,6502CPU与之完全一致。

65SC02CPU内部结构

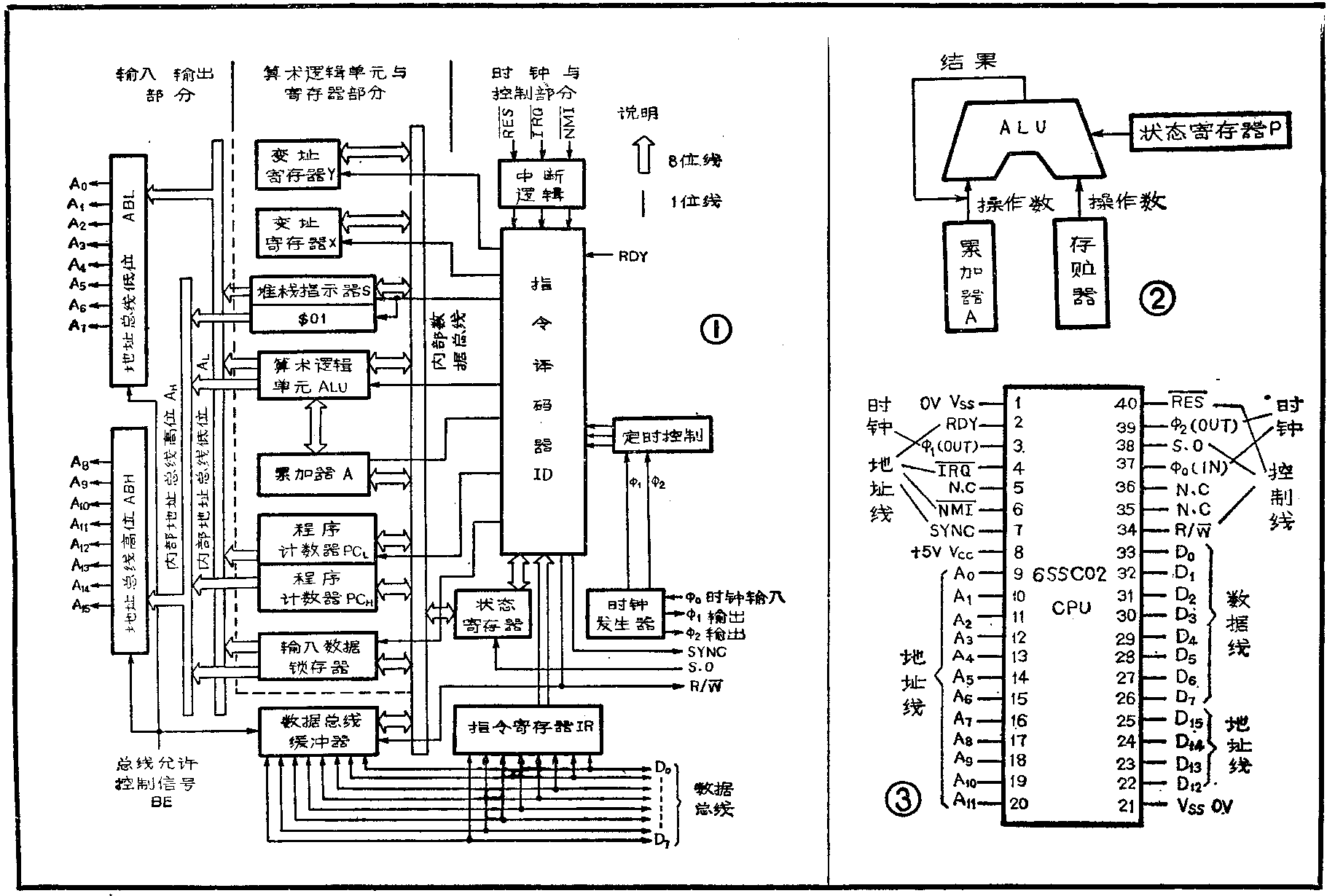

CPU是计算机系统的核心,控制着整个系统的运行,它由运算器、寄存器、控制器和总线等组成,图1是65SC02(6502)CPU内部结构框图。65 SC02 CPU 内部结构是总线结构形式,各功能部件都挂接在总线上。在允许信号BE的控制下,内部地址总线和数据总线分别通过地址总线驱动器和数据总线缓冲器,与外部地址总线和数据总线相连。CPU主要由以下三部分组成:

1.时钟与控制部分。控制部分包括指令寄存器IR和指令译码器ID。执行一条指令时,一开始总是取指(令码)操作,从存储器来的指令码数据经数据总线进入指令寄存器暂存,然后交指令译码器识别指令码的操作性质(译码过程),继而发出相应的控制信号。此外,控制部分还接受外部中断请求信号(NMI-和IRQ-)、准备好信号(RDY,也称等待信号WAIT)和复位信号(RES-)的控制,在一定条件下响应执行。时钟部分包括时钟发生器和定时控制两部分,它为系统提供基本时钟信号。为使时钟频率稳定通常用晶振振荡器来产生稳定的时钟φ\(_{0}\)(1MHz),CPU内部的时钟发生器再产生两个时钟信号φ1、φ\(_{2}\)供系统使用,其间关系φ1 φ-\(_{0}\) φ2=φ-\(_{1}\)=φ0。为了讨论上的方便,我们忽略它们的各种延迟参数,认为它们都是方波。

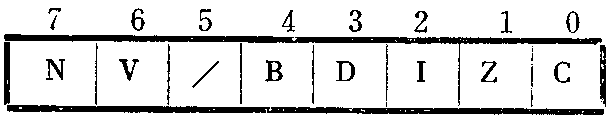

2.算术逻辑运算单元ALU和寄存器。①ALU是一个八位二进制并行算术、逻辑运算器、能把来自累加器、存储器或其它寄存器的数据内容进行运算,运算结果存入累加器A(冲掉A中原有内容)。②寄存器。寄存器的作用是暂时存放运算所需数据和运算结果,寄存器主要有下面几种:(a)通用寄存器(即A累加器),它是一个八位寄存器,通常作为存放参加运算或操作的一个数据或结果,图2是A累加器参加运算的示意图。(b)专用寄存器,包括变址寄存器Y和X、程序计数器PC和堆栈指针S。变址寄存器Y和X都是八位寄存器,专门为进行变址寻址时提供变址数值;有时也当作计数器使用,进行简单的加1或减1操作。程序计数器PC是十六位寄存器,专门为访问存储器提供地址信息,它分成高八位PC\(_{H}\)和低八位PCL,分时从内部地址线向外部地址总线发送,每送一次,地址自动加1。堆栈指针S是八位寄存器,CPU规定堆栈设在存储空间的第一页,其十六位地址的高八位地址为$01($表示十六进制),低八位地址由堆栈指针S决定,形成堆栈指针的地址为$01××,共256个存储单元($0100~$01FF)。堆栈的主要作用是记录断点地址(即进行程序断点保护),在中断返回时,按“先入后出”(先进栈的地址后出栈)的原则为程序提供断点地址。(c)状态寄存器P(也称标志寄存器Flag)。它与运算状态和运算结果密切相关,并反映在相应的标志位中,另外还可用指令设置各种状态。它是八位寄存器,用七位作状态标志位(第五位未用),其定义如下:

其中C是进位标志,C=0时表示无进位,C=1时有进位;Z是零标志位,Z=0表示结果非零,Z=1表示结果为零;I是中断屏蔽标志位,I=0允许中断,I=1禁止中断,但NMI-不受此约束;D是十进制运算标志位,D=0进行二进制运算,D=1进行十进制运算;B是BRK指令标志位,B=0时不允许软中断,B=1时允许软中断;V是溢出标志位,V=0数值不溢出,V=1时溢出;N是负数标志位,一般用数据最高位D7表示数的正负,当N=D7=0时数据为正数,反之N=D7=1为负数。

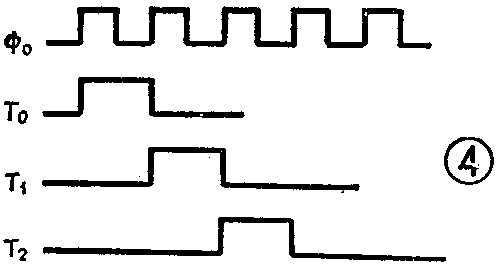

65SC02 CPU引线定义

65SC02CPU封装在40脚双列直插式管壳中,管脚功能见图3。40根引线按功能分为地址线(16条)、数据线(8条)、控制线(7条)、时钟线(3条)、电源线(3条)和未用的三条线。下面扼要介绍引线定义:(1)R/W-是读、写控制信号,是由CPU向系统功能部件发出的控制信号。R/W-端为高电平时系统执行读操作,R/W-端为低电平时执行写操作。(2)SYNC是同步信号,当CPU处于取指周期时,该端发出高电平,其它时间为低电平。(3)S.O是置溢出信号,外部方波的负跳沿使状态寄存器P的溢出标志位V置1(通常不用此线,而把它接地)。(4)RES-是复位信号,低电平有效,其作用是使CPU主要功能部件复位,起到初始化作用,即令PC寄存器清零和使其它寄存器都置“0”。复位信号的产生有两种途径:一是加电复位,即加电后电平自动降低,待电源稳定后自动升高;另一种是强制加入负电平,然后接高电平,RES-升高后先延迟6个定时周期,再从$FFFC、$FFFD中取出第一条要执行的指令码,开始进入执行程序。(5)RDY是准备好信号,也称等待信号WAIT,高电平有效。它的作用是协调高速CPU与慢速存储器或外设的读操作。当RDY变低电平时,CPU读操作周期将延续下去,此时R/W-信号和地址信号不变,直到RDY变为高电平为止。(6)NMI-是非屏蔽中断信号,CPU对该信号负跳沿进行采样,当有非屏蔽中断请求时,在执行完一条指令后,响应此中断请求。NMI-不受中断屏蔽位状态影响。(7)IRQ-是可屏蔽中断信号,CPU对该信号进行采样,同时状态寄存器P中的中断屏蔽位I=0(允许中断),CPU在执行完一条指令后转入响应中断请求,执行中断服务程序。中断服务程序执行完后,又返回主程序段继续执行下去。中断断点地址及状态存在堆栈中。若I=1,CPU不响应IRQ-请求。

CPU时序

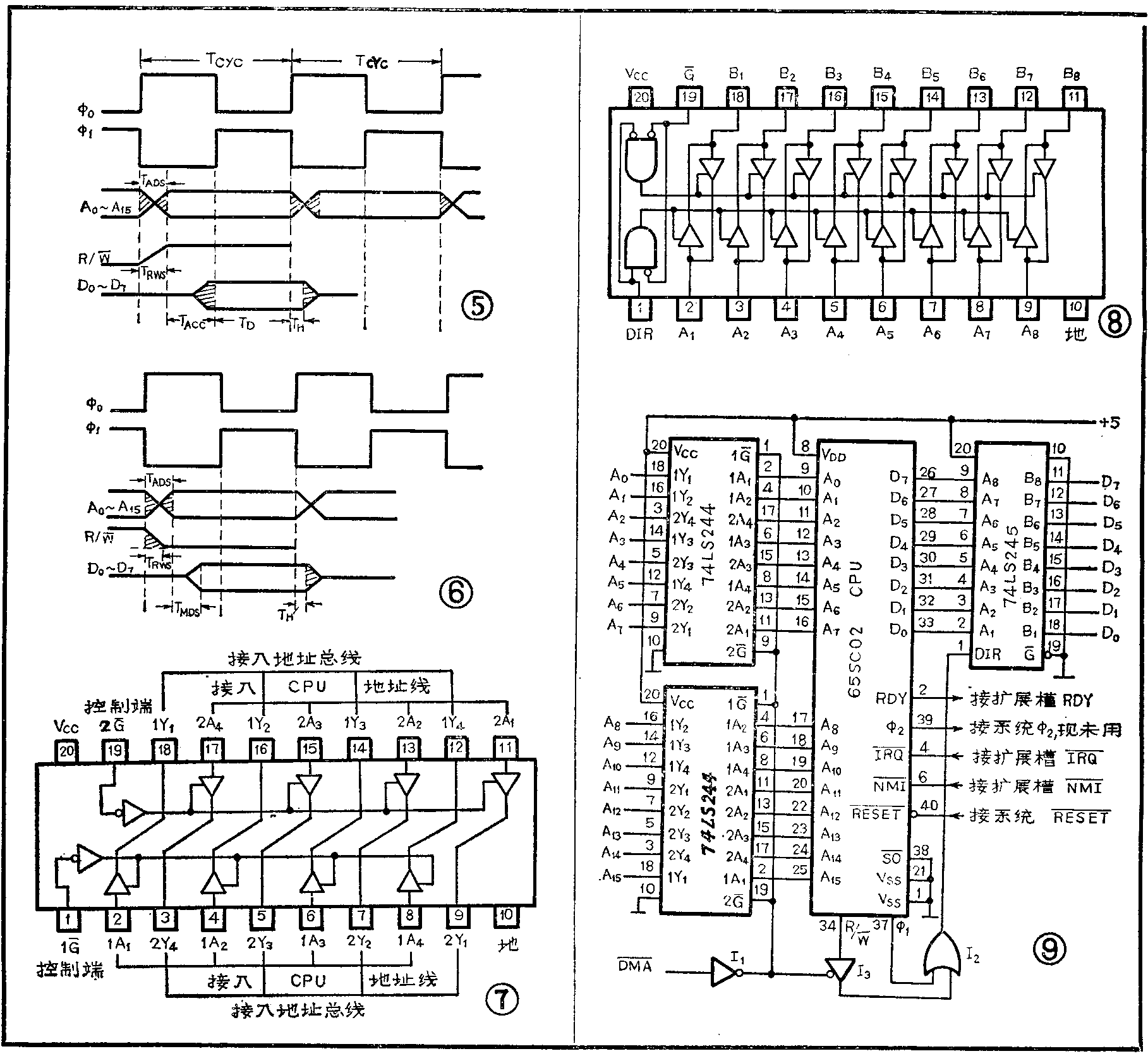

计算机之所以有条不紊地工作,是因为时钟信号给系统提供了时间基准和工作节拍。执行一条指令,可能占一个节拍,也可能占二个或更多节拍,但最长的指令节拍不会超过七个。一个节拍等于一个φ\(_{0}\)周期,工作节拍T0、T\(_{1}\)、T2……时间关系见图4。

65SC02CPU的基本读、写操作在第二讲中已从宏观信息流向关系做过介绍,现在从微观时间关系进行讨论。

1.读(输入)数据操作时序:图5表示出读操作周期的时序波形。在φ\(_{0}\)上升沿开始时,CPU发出的地址码即送入地址总线,但由于器件工作有一段延迟,送入的地址信息要经过TADS时间才能成为有效状态。读、写控制信号R/W-虽在φ0上升沿时已送入控制总线,但也要经T\(_{RWS}\)时间的延迟才能变为有效高电平。有效地址形成后,存储器接收并找到相应访问单元,在R/W-高电平读操作信息作用下,在φ0周期内将内容送入数据总线。从地址码(即地址信息)有效到数据读到总线的这段时间叫存储器访问时间T\(_{ACC}\),65SC02CPU要求TCC满足T\(_{ACC}\)≤TCYC-T\(_{ADS}\)-TDSU,T\(_{DSU}\)为读出数据稳定时间,TCYC为周期时间。

2.写(输出)数据操作时序:图6为CPU对存储器写数据操作时序图。地址码和R/W-(低电平)控制信号在φ\(_{0}\)上升沿开始时送入地址总线和控制总线,经一段延迟时间TADS和T\(_{RWS}\)后分别达到有效状态。被写的数据在φ0上升沿时已送入数据总线,当地址码稳定后,选中一个存储单元,在R/W-控制信号作用下将数据总线的内容写入被选中单元。

CPU与系统的连接

65SC02CPU的内部地址线和数据线分别通过地址驱动器和双向数据收发器与系统的地址总线和数据总线连接起来。

1.地址驱动器74LS244:它是三态驱动器,专为总线驱动设计的,其引线及内部逻辑见图7。当控制端1G-和2G-为低电平时,开启单向输出通道,接在输入端iAj(i=1、2,j=1~4)的CPU内部地址线与系统地址总线(接在输出端iYj上)连通。

2.双向数据收发器74LS245是三态输出输入总线收发器,其引线及内部逻辑见图8。图中DIR(1脚)为方向控制端,通常用R/W-读、写信号控制实现读入、写出。G-(19)脚为允许输入端,只在低电平时器件才能工作,因此用它启动或禁止器件工作。A\(_{0}\)(2)~A7(9)脚为一个方向的数据输入端,对应它的输出端为B\(_{1}\)(18)~B3(11)脚;另一个方向是把B端口作输入端,A端则作为输出端。其控制机制是:当G-为低电平、DIR也为低电平时,B端数据向A端输送;当G-为低电平,DIR为高电平时,A端数据向B端传送;当G-为高电平时,无论DIR电平是高是低,都使内部数据线与外部数据总线隔离。(待续)(乌振声)