用电子表控制数字钟

数字钟采用发光二极管显示时间,字型较大,清晰醒目,同时数字钟还具有定时,定闹,钟控等多种功能,所以被广泛使用。但是由于一般数字钟均未采用晶体振荡作为时间基准,而是利用工频电源作为时基,即直接对电源的周波数进行计数。然而电网频率变动在严重时可由标准的50Hz降为49.5Hz,即降低约百分之一。这样一来,数字钟24小时就将偏慢约14分钟。在一般情况下数字钟的日误差也较大而且往往没有规律,需要经常校表,这给使用者带来不便。

本人利用电子表芯的秒脉冲输出对数字钟进行同步控制,仅增设一块与非门和少数元器件就可使数字钟达到与电子表相同的计时精度,无需选用价格较贵的专用晶体与集成电路。

工作原理

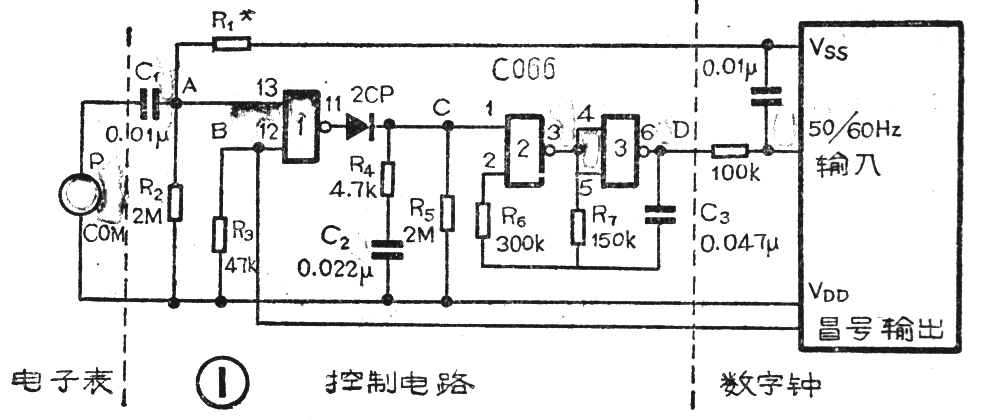

图1中第一条虚线左边是电子表示意图,P端为秒脉冲输出端,COM端为电子表显示输出的公共端。两条虚线间的电路则为新增设的控制电路。第二条虚线右边是数字钟电路的有关部分。为了使大家理解电路的控制原理,图2给出了电路中有关各点的波形示意图。

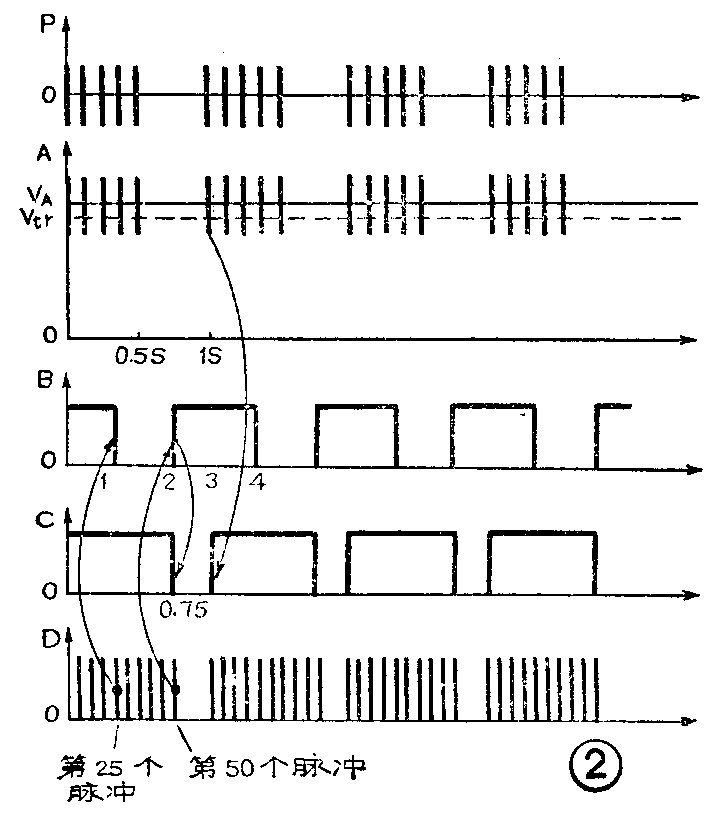

电子表P点输出波形见图2P,这是一个秒脉冲序列,每隔0.5秒输出16个频率为32Hz的方波脉冲。为了清楚起见,图中只画了5条线来代表16个脉冲,秒脉冲的重复周期为一秒。秒脉冲通过隔直电容C\(_{1}\)加在A点上,用它来控制与非门1输入端的电位变化,由于CMOS门电路输入端的转换电平Vtr约为其工作电源电压的一半(这里工作电压为14伏左右,故转换电子约为7伏左右),只有当输入电压高于V\(_{tr}\)时才为高电平输入,否则为低电平输入。因电子表输出脉冲的幅值仅为1.4伏左右,小于门电路的转换电平。为了使电子表的输出能控制与非门1的工作状态,电阻R1和R\(_{2}\)组成了一个工作点偏置电路,通过分压使得A点的静态电位略高于该门的转换电平Vtr(见图2A)。这样P点的输出脉冲就能通过电容C\(_{1}\)来控制与非门了。A点的波形就是P点波形与A点偏置电压相迭加的结果。

与非门1输入端B点的控制电压来自数字钟的冒号输出,其本身为数字钟的秒显示输出信号,冒号发亮时为高电平,冒号熄灭时为低电平,其电位高低变化周期为 1秒。因国内数字钟均设定为50Hz输入方式,所以每输入25个脉冲信号其冒号输出电平产生一次跃变。

A与B点的电位状态分别作用在与非门1的两个输入端上,而其输出端又紧接着一个由二极管和电阻R\(_{4}\)、R5及电容器C\(_{2}\)组成的一个脉冲解调电路。众所周知与非门输出电位的高低取决于两输入端的电位状态,只有当两输入端同时为高电平时,其输出才为低电平,否则输出恒为高电平。对本电路来说,若B点为低电平,则不论A点电位如何,与非门输出必为高电平,通过二极管使得C点也为高电平。若B点为高电平,则有两种情况:①如果A点有32Hz脉冲输入时,因为脉冲的负半周低于与非门的转换电平vtr(见图2A),所以A点的电位就在V\(_{tr}\)附近上下变化。当A点电位高于Vtr时,由于A与B同时为高,因此与非门输出为低电平;当A点电位低于V\(_{tr}\)时即为低电平输入,则与非门输出必为高电平。这样在A点有脉冲作用期间,与非门1的输出端就有相同频率的正脉冲输出,它通过解调电路进行峰值检波,使得C点在有32Hz正脉冲输入对恒为高电平。②如果A点没有32Hz脉冲输入时,因为A点的静态电位是高于Vtr的,即为高电平,此时A与B同时为高电平,则与非门输出便为低电平,使C点也为低电平。由上述分析可以得出A、B、C三者的关系为:只有当A点没有32Hz脉冲输入,而且B点同时为高电平时,C点才为低电平(图2中0.75S~1S期间),否则只要A点有脉冲输入或者B点为低电平时,C点必为高电平。与非门2和3组成了一个音频振荡器,R\(_{7}\)与C3决定其振荡频率在70赫左右,它工作与否完全由C点的电位高低所控制,只有当C点为高电平时,振荡器才能工作。

开始时,虽然B点为高电平,但因A点有32Hz脉冲输入,所以C点为高电平,使得由与非门2和3组成的振荡器产生70Hz的音频振荡,由D点输出方波脉冲经过数字钟内的RC抗干扰电路进入数字钟的“50/60Hz输入”端进行计数。为了清楚起见,图2D中每条线代表5个脉冲。当D点输出第25个脉冲时(时间为\(\frac{25}{70}\)秒,约0.35秒),数字钟秒冒号显示由亮变暗,B点电位由高变低(波形图中箭头1所示)。由A、B、C三者之间的关系可知,此时C点的电位不会发生变化,仍为高电平,振荡器继续工作,此后当振荡器输出第50个脉冲时(时间为50;70秒,约0.7秒),数字钟的秒冒号由暗变亮,使得B点电位由低变高(图中箭头2所录)。此时因为A点在0.5秒时间后已无32Hz脉冲输入,而B点变为高电平,所以C点立即变为低电平,迫使振荡器停止工作。此后0.3秒时间内振荡器无脉冲输出,数字钟处于等待状态。当A点1秒钟后重新有32Hz脉冲输入使得C点又变为高电平(箭头4所示),振荡器再次工作,重复上述过程。

由振荡器输出波形(图2中的D)可以看到,它每秒输出给数字钟均为50个脉冲,因此这完全可以保证数字钟准确计时,而计时精度仅取决于A点的秒脉冲精度,即电子表的计时精度。从波形图中还可看出振荡器每秒只工作一次,而每次只输出50个脉冲就被封锁住。所以数字钟的计时精度在一定程度上与振荡器的工作频率变化无关,频率的改变仅影响着振荡器在每秒内工作时间的长短。例如当振荡器的频率增高为90Hz时,振荡器工作时间缩短,其输出50个脉冲所需的时间为\(\frac{50}{90}\)秒,约0.55秒,而停顿时间增长为1-0.55=0.45秒。当振荡器工作频率降低为60Hz时。其工作时间延长,输出50个脉冲所需的时间变为50;60秒,约0.83秒,而停顿时间缩短为0.17秒。这样只要振荡器的工作频率在50~100Hz之内变化,都能确保振荡器每秒只输出50个脉冲给数字钟,从而保证它准确计数,不会引起数字钟计时偏慢或偏快。由于本电路中振荡频率选择在70Hz,而一般RC振荡器的工作频率稳定度约在±10%左右,所以可以保证它不会超出上述频率范围的。

制作与调试

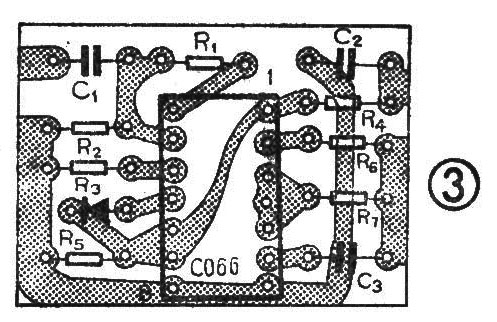

4-2输入与非门选用C066或C036。C\(_{3}\)应选用涤纶电容器,R2最好选用金属膜电阻。印刷板图见图3。

该电路唯一需要调整的是R\(_{1}\),这是因为不同器件CMOS与非门的转换电平Vtr是有差异的,其值可在30%~60%V\(_{DD}\)内变化,因此需要通过R1调整A点的直流电压。首先从数字钟内引出电源电压V\(_{DD}\)(有条件者可先用外接稳压电源)接至该电路,再用一只1.5MΩ的电阻与一个1MΩ的电位器串连代替R1,将B点与电源正极暂时相连,调节电位器的阻值自大向小慢慢减小,并用万用表观察C点的电位变化。当C点电位自高变低时,测出此时电位器的阻值大小,它与固定电阻的总值再减去200kΩ作为R\(_{1}\)的选定阻值。然后拆去B点与电源正极的连线,这样调试就完成了。

由于数字钟内部电路芯片的种类很多,引脚排列不同,必须找出数字钟的四个端点:V\(_{SS}\)、VDD、50/60Hz输入及冒号输出端(可参看本刊1986年第9、10期第45页)。首先将数字钟的50/60Hz输入端上的100kΩ电阻找到,将原来接交流电源的一端断开,改接至图1中的D点,再将冒号输出端与B点相连,最后再把电子表的秒输出P端和COM端(引出方法参看本刊1985年第1期第5页)分别与A点电容C\(_{1}\)的另一端和负极相连。通电检查可使用快调按钮来观察整个电路的工作情况:当按下快调按钮后,显示屏分位应快速变化,且每秒应有一次停顿,这样就说明整个电路工作正常。否则就应检查与非门1的工作点是否正常,必要时应重调R1的阻值大小。(李文谦)