UM5101(即NS—C\(_{1}\))语言处理器,是继UM5100之后面市的又一种超大规模CMOS集成电路,专门用于语言信号的记录和再生。与UM5100相比,它有许多改进。首先,UM5101使用动态随机存取存储器(DRAM)代替了UM5100使用的静态随机存取存储器,使处理器的成本、体积、耗电等指标都大大降低。另外,UM5101集成电路内部增设了话筒放大器、还音前置放大器、功率放大器推动级及众多的控制逻辑,使处理器的外接元件数大量减少,功能却增加许多。

由于UM5101接插的是动态随机存取存取器,所以它无法改接只读存储器(ROM)和可擦只读存储器(EPROM)。这是UM5101的一个不足。

UM5101的工作原理

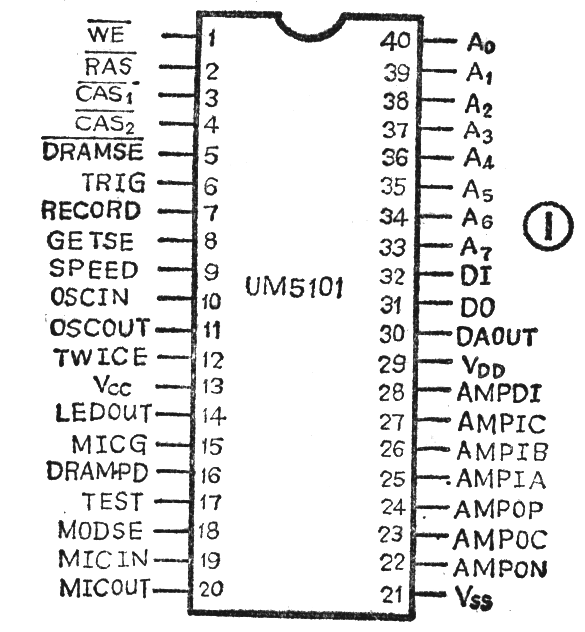

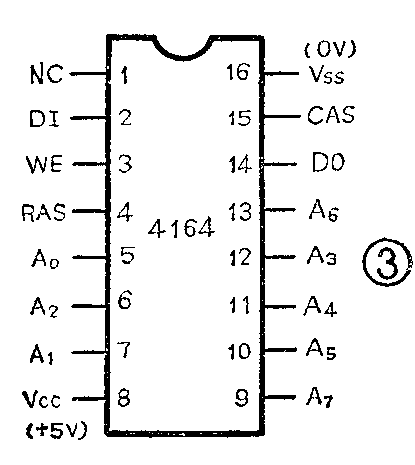

UM5101采用标准的四十脚双列直插式塑料封装结构,其外形及引脚排列如图1所示。图2绘出了UM5101的内部功能方框图。简单地说,电路内部主要包括如下几个功能:

1.话筒放大:负责将话筒送来的微弱语言信号放大,并将信号控制在后级所需要的电平范围以内。

2.模/数、数/模转换器:负责模拟信号的分解和数字信号的合成。

3.时钟电路、读/写地址计数器、刷新地址计数器及存储器控制电路:为外接存储器提供地址和所需的各种控制信号。

4.前置低放和功放推动级:负责再生语音信号的放大。

5.控制逻辑部分:协调其它功能块的工作并输出和接受各种控制信息。

UM5101各管脚的功能如下:

1脚WE-:读/写控制信号输出脚,连接到存储器,低电平有效。

2脚RAS-:行地址选通信号输出脚,连接到存储器,低电平有效。

3脚CAS1-:第一块存储器的列地址选通信号输出脚,低电平有效。

4脚CAS2-:第二块存储器的列地址选通信号输出脚,低电平有效。

5脚DRAMSE-:存储器选择,输入脚。当此脚为高电平时,UM5101的寻址能力为64K,只有第一块存储器工作。当此脚为低电平时,UM5101的寻址能力扩展为128K,两块存储器都投入工作。

6脚TRIG:触发端。UM5101处于“手动录放模式”时,每向此脚送入一个高电平脉冲,电路便放音一次。当UM5101处于“自动录放模式”时,向此脚输入一个高电平脉冲,电路便进入录音、放音循环状态(详见后述)。

7脚RECORD:录音端,输入脚。当UM5101处于“手动录放模式”时,向此脚送入一个正脉冲后,电路进入录音状态。在“自动录放模式”时,此脚没有作用。

8脚GETSE:采样速度选择输入脚。当此脚为高电平时,采样速度较低,为f\(_{osc}\)/32, fosc为时钟频率;当此脚为低电平时,采样速度提高一倍,为f\(_{osc}\)/16。

9脚SPEED:放音速度输入脚。当此脚为低电平时,放音速度与录音速度相同;当此脚为高电平时,放音速度降低至原录音速度的1/2。

10脚OSCIN:振荡输入脚。与OSCOUT脚和外接电阻构成时钟振荡器。

11脚OSCOUT:振荡输出脚。与OSCIN脚及外接电阻构成时钟振荡器。

12脚TWICE:重放两次输入脚。当此脚为高电平时,电路每次进入放音状态都将所录内容重放两次。

13脚V\(_{cc}\)+5V电源输入脚。

14脚LEDOUT:指示灯驱动输出脚。当电路进入录音状态时,此脚为低电平,点亮外接发光二极管LED,表示正在录音。

15脚MICG:话筒接地输出脚。当电路进入录音状态时,此脚为低电平,话筒一端接地,使话筒正常工作。

16脚DRAMPD:存储器供电输出脚。当电路工作时,此脚为低电平。

17脚TEST:测试输入脚。当此脚为低电平时,电路正常工作;此脚为高电平时,电路处于测试状态。这一功能主要用于集成电路出厂时的检验,平常使用时这一脚千万不要接高电平。

18脚MODSE:工作模式选择输入脚。当此脚为高电平时,电路工作在“自动录放模式”;当此脚为低电平时,电路工作在“手动录放模式”。

19脚MICIN:话筒输入脚。话筒捡拾的语音信号,经过一个隔直电容送入此脚进行放大。

20脚MICOUT:话筒放大输出脚。与MICIN的外接电阻配合,用来调节话筒放大器的增益。

21脚V\(_{ss}\):零伏接地脚。这一脚是电源接地端。

22脚AMPON:功放驱动输出脚,接输出NPN管的基极。

23脚AMPOC:功放输出脚。

24脚AMPOP:功放驱动输出脚,接输出PNP管基极。

25脚AMPIA:低放正输入脚。数/模转换后再生的语音信号经滤波网络输入此脚。

26脚AMPIB:低放负输入脚。功放级的输出信号反馈至此脚。

27脚AMPIC:功放偏置输入脚。外电路经此脚向电路内部的功放推动级提供偏置电压。

28脚AMPDI:偏置驱动输出脚。当电路进入放音状态时,此脚为高电平,给功放推动级提供偏置电流。

29脚V\(_{DD}\):+8V电源输入脚。

30脚DAOUT:数/模转换器输出脚。此脚输出未经滤波的再生语音信号。

31脚DO:存储器数据输入脚,连接到存储器。存储器输出的数字信号经此脚读入。

32脚DI:存储数据输出脚,连接到存储器。UM5101输出的数字信号经此脚送入存储器。

33~40脚即A\(_{7}\)0:行列地址输出脚。连接到存储器,提供数据地址。A\(_{7}\)0顺序排列。

UM5101有两种基本的工作模式,即前面曾提到的“自动录放模式”和“手动录放模式”。当电路被设定为自动录放模式时,此时第18脚为高电平。接通电源开关后,电路自动开始录音,录音结束后立即开始放音,放音结束后电路又重新进入录音状态。这个循环一共要进行32次。而后,电路转入守候状态。在这种状态下,每向第6脚(TRIG)送入一个正脉冲,电路将继续进行录音、放音,循环32次。

当电路被设定为手动录放模式时,接通电源开关后,电路处于守候状态。此时只有向第7脚(RECORD)送入一个正脉冲,电路才能脱离守候状态,开始录音。录音结束后自动恢复到保持状态。以后每向第6脚(TRIG)送入一个正脉冲,电路便重放刚才所录的内容一次(第12脚TWICE为高电位时放两次)。

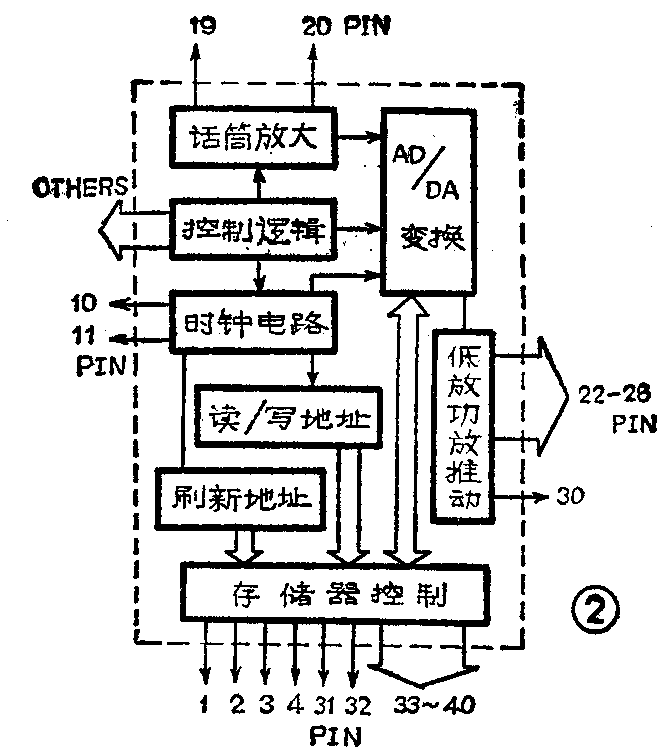

4164的工作原理

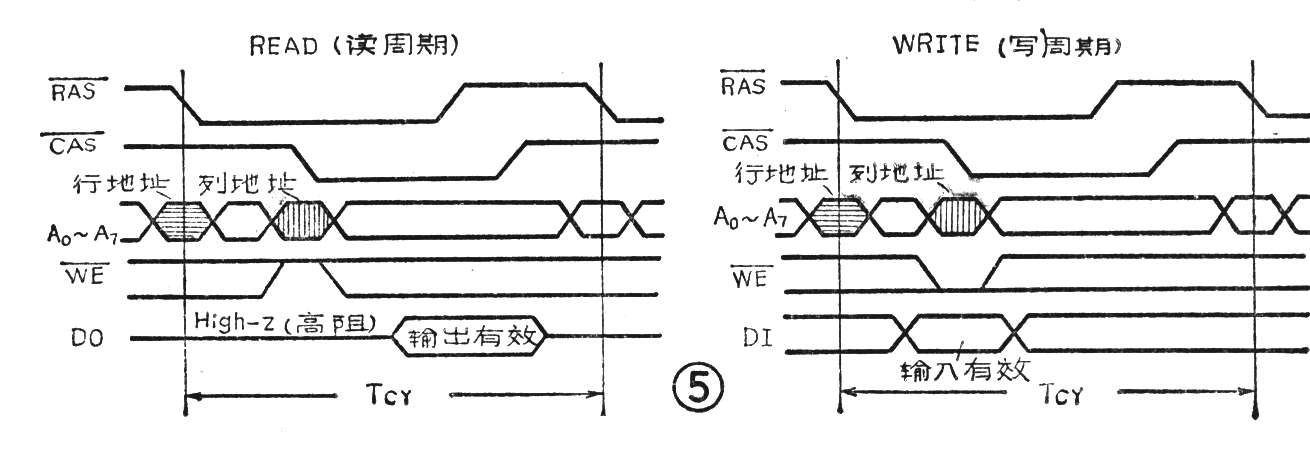

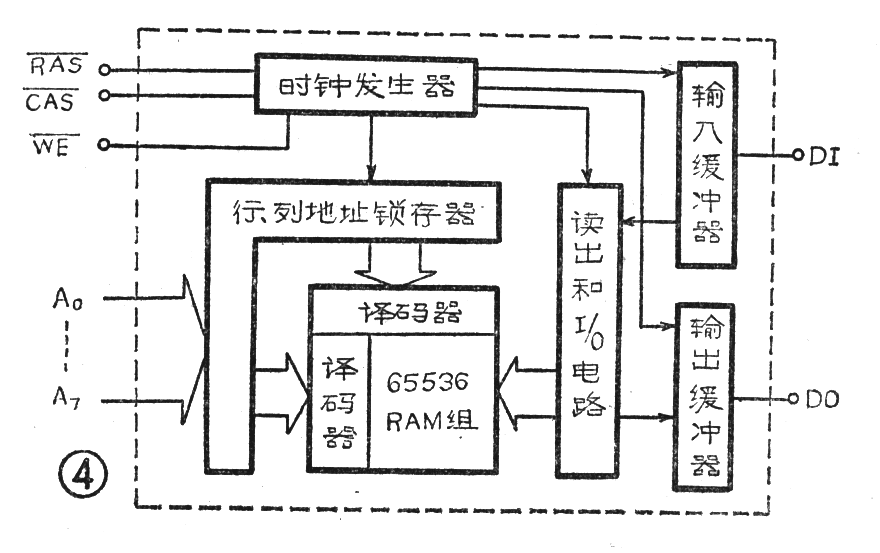

4164是与UM5101配套使用的一个存储器。它是采用NMOS工艺制造的动态随机存取存储器,存储量为64K×1位,有寻找65536个地址的能力。图3是4164的外形及引脚排列图。分析一下4164的引脚,读者可能会提出下列问题:64K存储器,按说芯片应该有16根引线作为地址线。但为什么在图3中只看到有A\(_{0}\)78根地址线?结合图4所示4164的功能图可以看出,该存储器的地址信息是采用分时传送方式提供的。也就是将16位地址信息分成行地址(A\(_{0}\)7)和列地址(A\(_{8}\)15),用行选通信号RAS—和列选通信号CAS—分别控制行地址和列地址的接收。在4164内部设有行地址锁存器和列地址锁存器。当RAS—有效(低电平)时,芯片接收A\(_{0}\)78位行地址,存入行地址锁存器;之后CAS—变为有效,芯片接收A\(_{8}\)158位列地址存入列地址存储器。行、列地址锁存器中的地址再经译码,提供所需的读写地址。

4164的数据输入引脚(DI)和输出引脚(DO)是分开的,并且加有各自的缓冲器。芯片只有一个控制信号端WE—(读/写控制),一切读写操作均由它控制完成。图5是4164读、写周期波形图,可供参考。同是4164,由于档次和生产厂家不同,读/写速度这一指标可能相差较大。一般读写周期(即图5中的T\(_{CY}\))在250ns~410ns左右,这个速度配合UM5101使用已足够。4164是动态存储器,它内部的信息必须不断地刷新(再生)才得以保存。4164采用的是整行刷新的方法,每次刷新一行。刷新周期为2ms。4164芯片使用单一的+5±10%电源。其数据输入、输出均为标准的TTL电平,静态电流也只有几个毫安,使用起来十分方便。4164芯片也有不足之处,它没有设片选信号CS—,在多片并接使用时,需要外接一些附属电路。除64K的4164以外,UM5101还可配接其它容量的动态存储器。如常见的16K DRAM4116、256K DRAM41256等。(未完待续) (赵九泷)