锁相环简称PLL,可广泛用于广播通信、频率合成、自动控制及时钟同步等技术领域,是一种极有发展前途的器件。过去的锁相环多由分立元件和模拟电路构成,国外于七十年代研制成单片CMOS数字集成电路锁相环,目前国内也能批量生产这种器件。本文首先介绍锁相环的基本概念.然后重点分析集成锁相环CC4046的工作原理,并结合实例加以说明。

锁相环简介

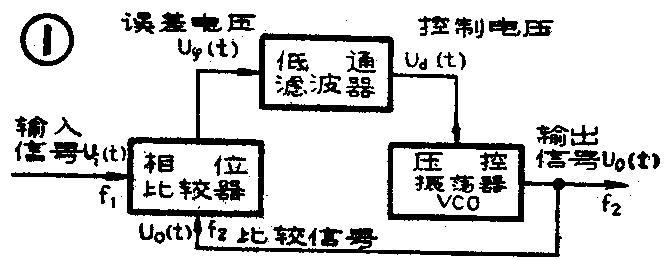

所谓锁相,就是自动实现相位同步。能够完成两个电信号相位同步的闭环系统叫锁相环。锁相环主要包括三部分:相位比较器(亦称鉴相器);低通滤波器;压控振荡器(符号为VCO)。见图1。

相位比较器一端接输入信号U\(_{i}\)(t),另一端接比较信号UO(t)(即压控振荡器的输出信号)。比较器把U\(_{i}\)(t)与UO(t)的相位进行比较,产生一个与两信号的相位差成正比的输出电压(即误差电压)U\(_{ф}\)(t)。Uф(t)再经低通滤波器滤除高频分量后,便得到平均值电压U\(_{d}\)(t)。Ud(t)是控制电压,加在压控振荡器的控制端。使VCO的振荡频率f\(_{2}\)向输入信号频率f1靠拢,二者频率差迅速减小,直至0,f\(_{2}\)=f1。这时两个信号的频率相同。两相位差保持恒定(同步),称作相位锁定。

应当指出,环路入锁以后,锁相环还具有“捕捉”信号的能力。如果信号频率f\(_{1}\)再发生变化(在锁相环的捕捉范围内),锁相环就能再次捕捉到f1,并强迫VCO锁定在f\(_{1}\)上。锁相环属于负反馈系统,其信号流程为:

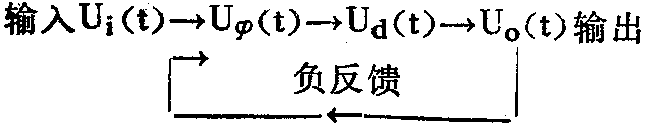

锁相环在具体应用时非常灵活。如果f\(_{2}\)1,而要求二者保持一定关系(例如比例关系或差值关系),则可在负反馈线路上插入一个运算器,如除法器÷N、乘法器×N、加法器+N、减法器-N,见图2。以满足各种不同的工作需要。

锁相环的工作原理

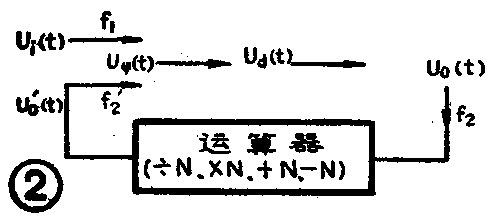

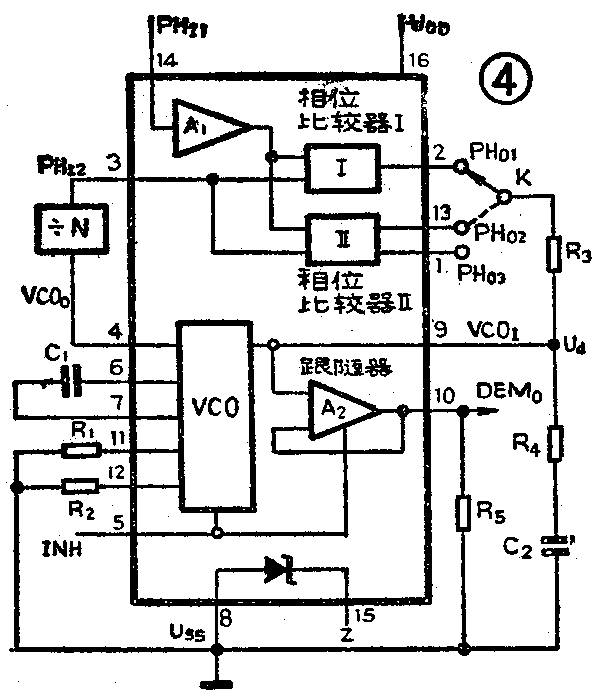

4046型是目前国内外最常见的锁相环,它属于CMOS集成电路,国外产品有CD4046、MC14046、国内型号有CC4046、5G4046、J691等。其中CC4046为新国标型号,其功能及引线同国外产品完全一致,可以互换。CC4046为双列直插式,共有16个引出端,见图3。各引出端的功能如下:

PH\(_{I1}\)—输入信号端;PHI2—比较信号输入端;PH\(_{0}\)1—相位比较器Ⅰ的输出端;PH02—相位比较器Ⅱ的输出端;PH\(_{0}\)3—相位输出端,环路入锁时为高电平,环路失锁时为低电平;VCO0—压控振荡器输出端;INH—禁止端,高电平时禁止。低电平时允许压控振荡器工作;VCO\(_{I}\)—压控振荡器的控制端;DEM—解调输出端,用于FM解调;Z—内部独立的齐纳稳压管负极;UDD、U\(_{SS}\)—电源的正端与负端。

CC4046的电源电压范围很宽,为3~18V,一般可选5V、10V、15V等。取U\(_{DD}\)=10V,动态功耗约为1.6mW,属于微功耗器件。

CC4046的逻辑图如图4所示,它主要包括:相位比较器、压控振荡器VCO、线性放大器及整形电路A\(_{1}\)。另需外接阻容元件构成低通滤波器。现对总的工作过程作一简要说明。

输入信号U\(_{i}\)从14脚输入后,经放大器A1进行放大、整形加到相位比较器Ⅰ和Ⅱ的输入端(具体使用哪个比较器,需按实际工作情况确定)。图中由于开关K拨至2脚,比较器Ⅰ可把比较信号U\(_{0}\)(从脚3输入)与输入信号Ui作相位比较,从相位比较器Ⅰ输出的误差电压U\(_{ф}\)(t)就反应出二者的相位差。Uф经R\(_{3}\)、R4及C\(_{2}\)滤波后,得到控制电压Ud加至压控振荡器VCO的输入端9脚,调整VCO的振荡频率,使f\(_{2}\)迅速逼近信号频率f1。VCO的输出又经除法器再送到相位比较器,继续与U\(_{i}\)进行相位比较。最后便使得f2=f\(_{1}\),二者的相位差为一定值,实现了锁相。在对图4的工作过程有一概括了解之后,下面分别叙述各部分的工作原理。

1、相位比较器:

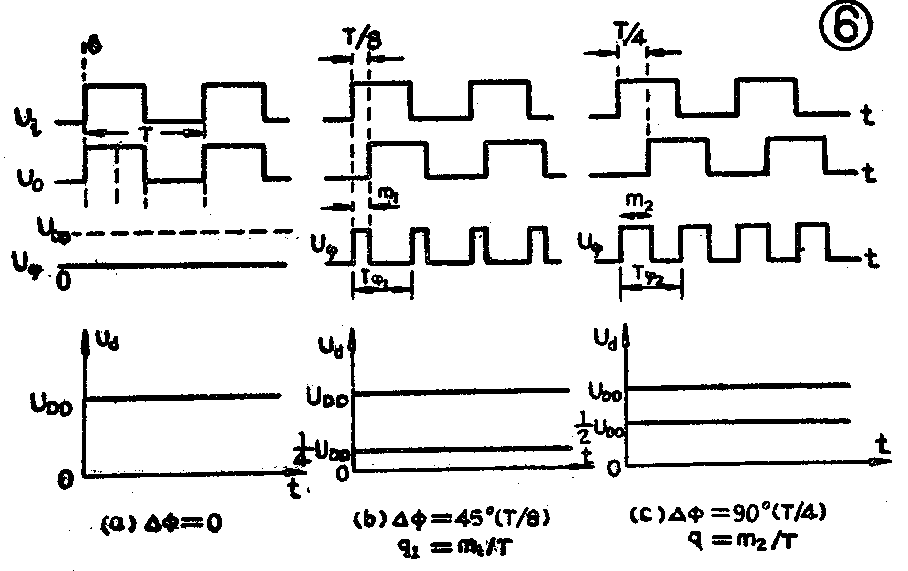

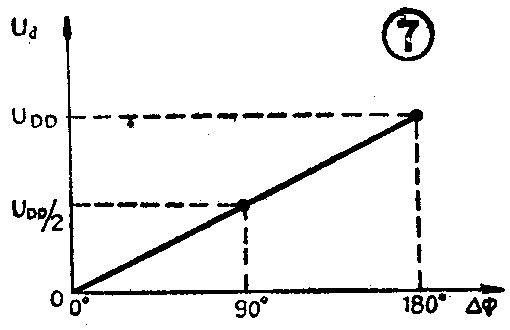

CC4046内部有两个相位比较器。比较器Ⅰ采用异或门结构,异或门的逻辑符号见图5。其特点是:两个输入端信号U\(_{i}\)、U0 的电平状态相异时(一个是高电平“1”,另一个是低电平“0”),输出瑞信号U\(_{ф}\)为高电平;反之为低电平。当Ui与U\(_{0}\)的相位差在0°~180°范围内变化时,Uф的脉冲宽度m也随之改变,即占空比q(q=m/T\(_{ф}\),Tф是U\(_{ф}\)的周期)也在改变。Uф经低通滤波器,即可得平均值电压U\(_{d}\)。在图6(a)中,Ui与U\(_{O}\)相位差=0°,平均值电压Ud=0。图6(b)中,△φ=45°(T/8),U\(_{ф}\)波形如图示,其平均值电压Ud=\(\frac{1}{4}\)U\(_{DD}\)。图6(c)中,=90°(T/4),这时Uф波形中一个周期的平均值U\(_{d}\)=1;2UDD。若=180°,则U\(_{d}\)=UDD。由此可得到U\(_{d}\)与之间的关系曲线(见图7)。

对于相位比较器Ⅰ,它要求U\(_{i}\)与UO的占空比均为50%(即方波),这样才能使锁定范围最大。

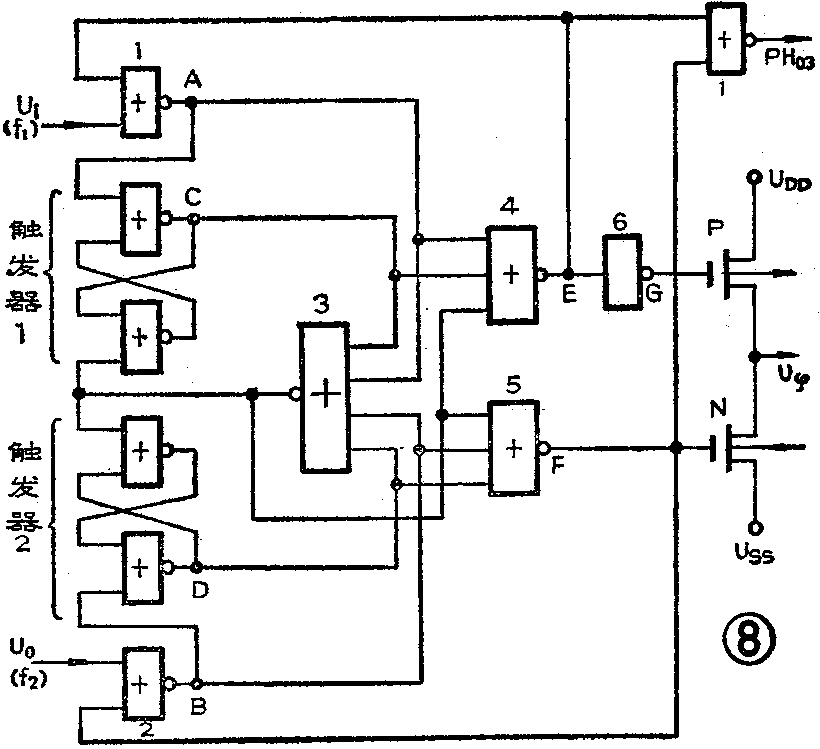

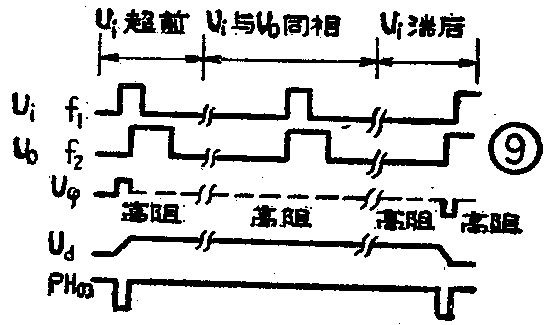

相位比较器Ⅱ是一个由信号的上升沿控制的数字存储网络,由其逻辑图8可知,它由门电路、RS触发器,三态P沟道和N沟道管输出级组成。由于它仅在U\(_{i}\)和UO的上升沿起作用,故与二者是否为方波无关,它可接受任意占空比的输入信号。根据两信号频率的关系,比较器Ⅱ的输出状态有以下几种情况:

(1)当f\(_{1}\)>f2时,输出级P沟道管子导通,U\(_{ф}\)为高电平“1”(接近于UDD)。

(2)当f\(_{1}\)<f2时,输出级N沟道管子导通,U\(_{ф}\)为低电平“0”(接近于USS)。

(3)当f\(_{1}\)=f2时,视二者相位差而定。若U\(_{i}\)超前于UO,则输出级状态同(1);若U\(_{i}\)滞后于UO,则输出状态同(2)。

(4)当f\(_{1}\)=f2且=0(相位锁定)时,P、N沟道管均截止,输出级呈高阻状态。下面以f\(_{1}\)=f2且U\(_{i}\)相位超前UO为例,结合图8、图9说明比较器Ⅱ的工作原理。

我们知道,或非门的逻辑功能是:只要有一个输入信号为高电平,其输出就为低电平;只有所有的输入信号为低电平时,其输出才为高电平。

在初始状态,U\(_{i}\)=UO=0,图8中的或非门1和2的输出端A和B均为“1”,使触发器1和触发器2的输出均为“0”,U\(_{ф}\)呈高阻态。由于Ui超前于U\(_{O}\),故Ui的上升沿先来到,使或非门1的输出由“1”变为“0”,或非门1的下降沿对触发器1不起作用,因此在或非门3的四个输入端中,只有接B点的一端为“1”故其输出为“0”。此时或非门四的三个输入端均为“0”,其输出为“1”。一方面经非门6变为“0”,使P沟道管导通。同时经或非门7(图中误标1)使相位输出端PH\(_{0}\)3为低电平。此时或非门5因B点高电平“1”其输出为低电平“0”,故N沟道管截止。所以Uф为高电平。经过一段时间后,U\(_{O}\)的上升沿来到,使或非门2的输出变为“0”,这样使或非门3的所有输入端均为“0”,其输出变为“1”,进而使P沟道管截止,Uф又呈高阻态,而PH\(_{0}\)3变为高电平。

2、压控振荡器:

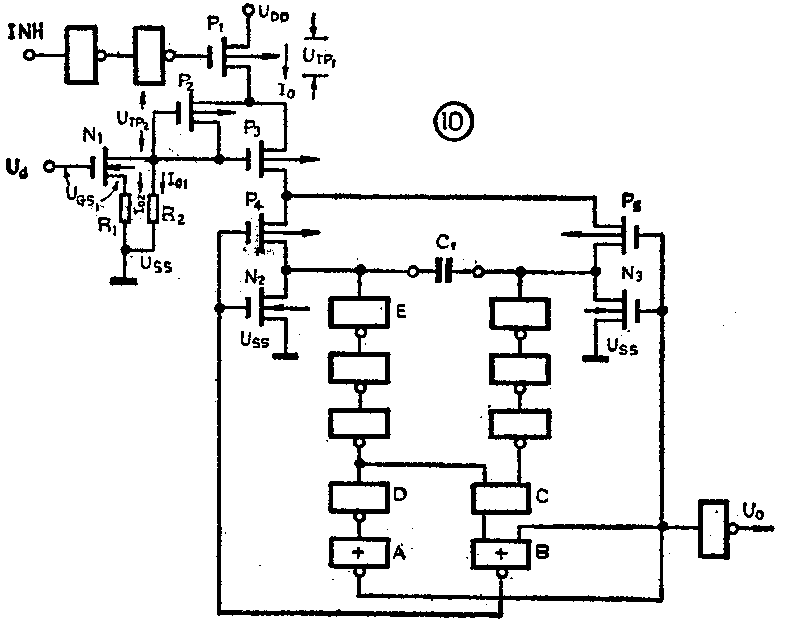

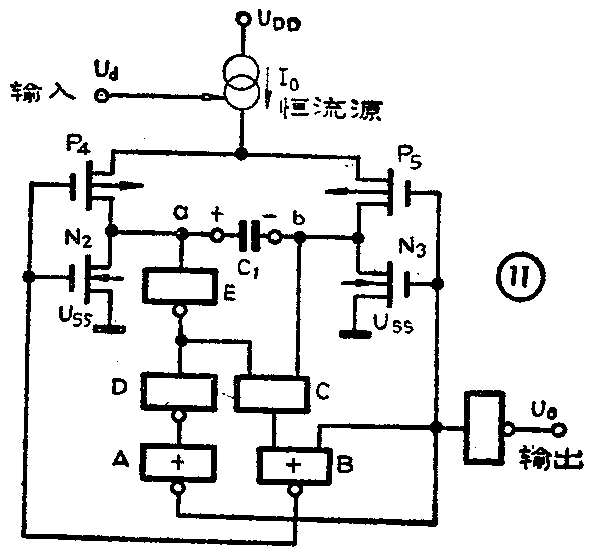

CC4046锁相环采用的是RC型压控振荡器,其逻辑图见图10,等效电路如图11所示。图10的基本工作过程是:输入电压U\(_{d}\)通过控制N1管的状态来控制流过N\(_{1}\)管电流I01的大小,进而控制电流I\(_{0}\)的大小。通过I0对C\(_{1}\)的充放电,即可实现对压控振荡器VCO振荡频率的控制。

当U\(_{d}\)<UTN1(N\(_{1}\)管的开启电压)时,N1管截止,I\(_{0}\)1=0,这时I0有最小值,VCO仅维持最低频率的振荡。若电路中不接R\(_{2}\),电路将停振,此时压控振荡器的最低频率等于零。

当U\(_{TN1}\)<Ud<U\(_{DD}\)时,N1将饱和导通。这时I\(_{0}\)1随Ud的改变而变化。若U\(_{d}\)降低,I0减小,使得C\(_{1}\)的充电时间延长,f2降低。反之,U\(_{d}\)增高时,f2也增高。

当U\(_{d}\)=UDD时,N\(_{1}\)深度饱和,I01有最大值,I\(_{0}\)也有最大值。这时,C1将以最快的速度充放电,使得振荡频率有最高值。

在图11的等效电路中,或非门A、B的输出端状态受C\(_{1}\)上的电压控制。假设初始状态时,A输出“1”,B输出“0”,则P4,N\(_{3}\)管导通,P5、N\(_{2}\)管截止,这时I0 经P\(_{4}\)、C1、N\(_{3}\)对C1充电。当C\(_{1}\)两端的电压UC1超过反相器E的开启电压(约4V)时,门E输出为“0”,经门D、门A两级反相,使门A输出为“0”。同时又使C的输出为“0”,迫使B的输出从“0”变为“1”,触发器完成一次状态翻转。这种状态又使P\(_{5}\)、N2导通,P\(_{4}\)、N3截止,C\(_{1}\)被反相充电、(相当于放电)。然后再次充电、放电,如此循环往复便形成了振荡。当Ud等于U\(_{DD}\)时,VCO有最高的振荡频率。

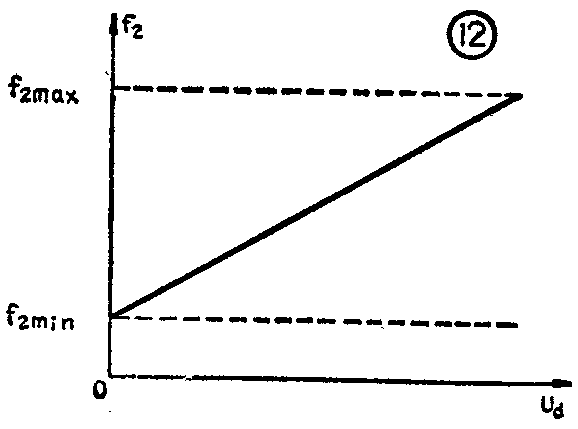

一般规定CC4046的最高工作频率为1.2MHz(U\(_{DD}\)=15V)。若UDD<15V,fmax要降低一些。U\(_{d}\)与压控振荡器输出频率f2呈良好的线性关系,见图12。图中的线性度高达0.3%~0.9%。选U\(_{DD}\)低一些,能提高线性度,但输出最高频率要降低。

在CC4046内部,还有线性放大电路及整形电路A\(_{1}\),可把PHI1端100mV左右的微弱输入信号变成方波或脉冲信号送至相位比较器。另外,还有跟随器A\(_{2}\),VCO的输出电压经A2到DEM\(_{0}\)端作FM解调用。内部的齐纳二极管可单独使用,其稳压值UZ≈5V,若与TTL电路匹配时,可作辅助电源。

CC4046需外接RC滤波器,由R\(_{3}\)、R4及C\(_{2}\)组成,滤波器的参数可根据需要来选择。其主极点频率fP=1/2π(R3+R\(_{4}\))C2。

综上所述,我们可以简单地概括如下:输入信号Ui(t)接信号输入端PH\(_{I1}\),经相位比较器Ⅰ(或Ⅱ)与输出信号UO(t)进行相位比较后,产生一个与两信号的相位差成正比的输出电压U\(_{ф}\)(t),经PH01(或PH\(_{0}\)2)输出。Uф(t)经外接RC滤波器滤除高频分量后,便得到平均值电压U\(_{d}\)。Ud经VCO\(_{1}\)端送入压控振荡器,以控制其频率的大小,使压控振荡器的频率f2向输入信号频率f\(_{1}\)靠拢,直至达到相位锁定。

锁相环的典型应用

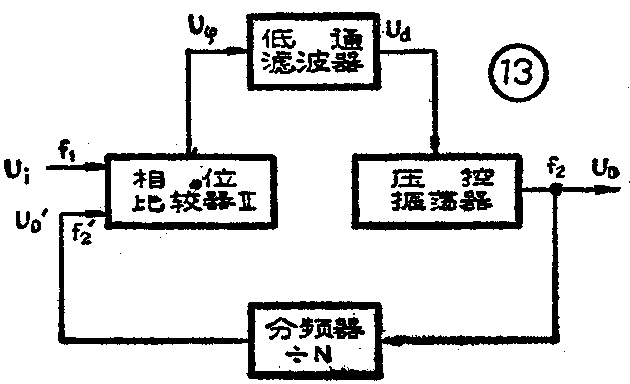

以上介绍了锁相环的原理,下面通过一个实例说明其用途。锁相环可构成倍频电路,使输出信号的频率为输入信号频率的N倍(f\(_{2}\)=Nf1),若f\(_{1}\)为基准频率,由石英晶体振荡器产生,经倍频后f2的频率稳定度则与f\(_{1}\)相当,这是目前用其它倍频电路所难以实现的。

把N进计数器插在VCO输出端与比较器输入端之间,即可对输入频率进行准确的N倍频,见图13。应当说明,因为计数器是接在锁相环的负反馈电路上,所以要想对输入信号倍频(作乘法运算),必须使用除法器(分频器÷N)才行。

图14是100倍频的实用电路。电路采用了CC4518型二——十进制计数器,故可完成100分频。图中标出了U\(_{i}\)(f1)、U\(_{O}\)′(f2′)、U\(_{ф}\)、Ud、U\(_{O}\)(f2)的去向,尽管U\(_{O}\)′与UO、f\(_{2}\)′与f2通过计数器有联系,但它们不是一回事。

刚开机时f\(_{2}\)′可能不等于f1,假定f\(_{2}\)′<f1,此时相位比较器Ⅱ的输出级P沟道管导通,U\(_{ф}\)为高电平,滤波后Ud逐渐升高,使VCO输出频率f\(_{2}\)迅速上升,f2′也增大,直至f\(_{2}\)′=f2。如果此时U\(_{i}\)滞后于UO′,则相位比较器Ⅱ的输出级N沟道管导通,P沟道管截止,U\(_{ф}\)为低电平。Uф经滤波后得到的U\(_{d}\)信号开始下降,这就迫使VCO对f2进行微调;最后达到f\(_{2}\)′=f2/N=f\(_{1}\),并且f2′与f\(_{1}\)的相位差=O°,进入锁定状态。如果此后f1又发生变化,锁相环能再次捕获f\(_{1}\),使f2′与f\(_{1}\)相位锁定。这就是锁相环所具有的特殊功能。(沙占友)