CMOS集成门电路已在各种电子电路中得到广泛应用,但在实际使用中,往往因为不同厂家生产的门电路管脚排列不完全一致,这给互换带来麻烦。下面介绍用万用表确定与非门的输入、输出端及判断该门电路好坏的方法。

CMOS集成与非门通常的封装形式为双列14脚。一般第七脚接V\(_{SS}\)(电源负极),第14脚接VDD(电源正极),其余12个脚可能是四个双输入门,也可能是三个三输入门或二个四输入门。用万用表R×1k档,以黑表笔接七脚,以红表笔依次接触1~6脚及8~13脚,会发现这些脚中有的阻值稍大,有的阻值稍小。则阻值稍大的脚为与非门输入端,阻值稍小的脚为输出端。测试中还可能看到有些脚的阻值接近∞或零。阻值∞有两种可能:一种是该脚为空脚,如双四输入与非门有两个空脚;第二种是该脚已断路。阻值接近零则说明该脚已与V\(_{SS}\)击穿短路。断路或短路均说明该门电路已损坏(其余门仍可正常使用)。

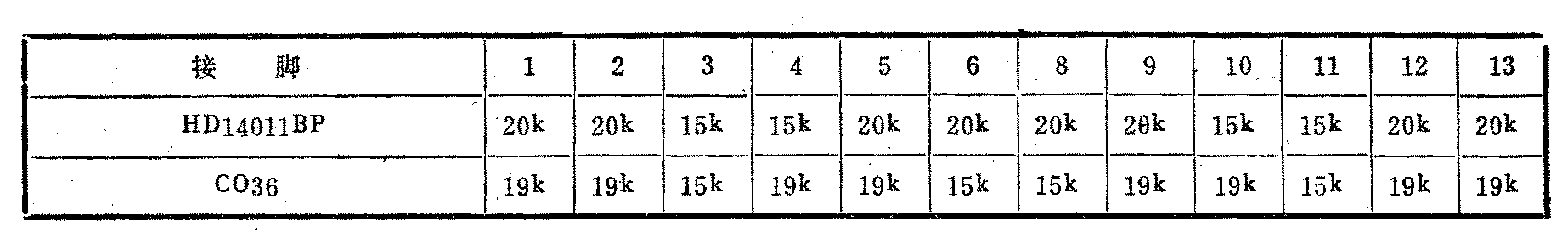

下面举例说明。用MF—30万用表测试HD14011BP及CO36,测得阻值如下方附表:

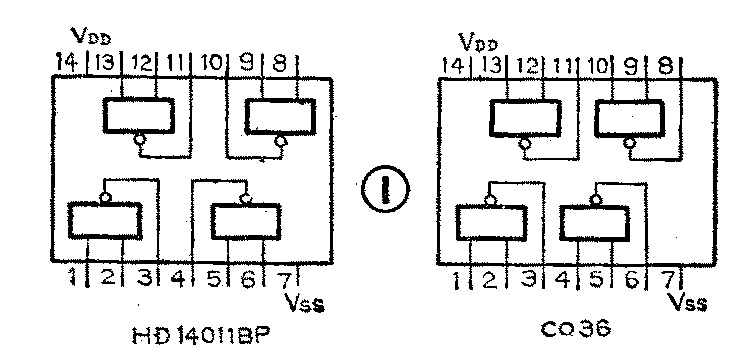

如表所述,可断定它们均为含四个双输入与非门的集成块,各接脚的位置可确定,如图1所示。

如用不同万用表来测,测试数值与表中相比有出入,但是符合输入端数值大于输出端数值这样一个规律。用同样的方法,也可对或非门、与门、反相器等集成门电路进行测试判别。(李新由)