在微计算机中,存取信息、执行指令,都按一定的地址进行。要弄清计算机的工作原理和正确地使用计算机。就要对计算机中的地址编排有个明确的了解。

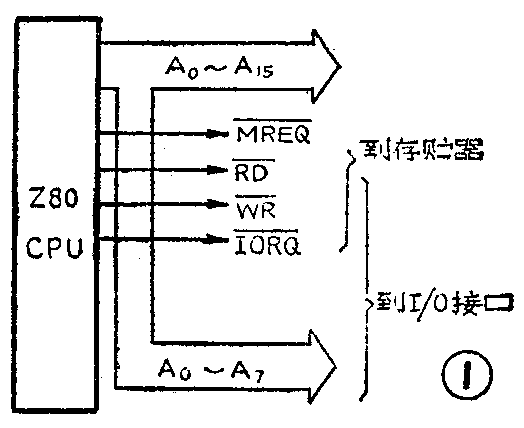

微型计算机中,中央处理器(CPU)与存贮器、输入输出口的连接有三组总线,即:传送数据的数据总线;控制读、写等操作的控制总线;选择存贮器单元的地址总线。中央处理器对每个存贮单元或输入输出口的访问,是由控制信号和地址信号配合实现的,为了达到这种配合必须有一定的硬件结构与这两种信号配合。所以微型计算机中存贮单元、输入输出口的地址编排是由硬件结构决定的。

地址的编排叫编址,编址的方式一般有两种,这就是独立编址和统一编址。

独立编址方式是把存贮单元和I/O接口的地址分开设置。中央处理器访问内存或外设分别由不同的控制信号完成。中央处理器的各种控制信号如图1所示。从图中可以看出这种编址方式访问内存贮器的指令(也叫访内指令)和访问I/O接口外部设备的控制信号是分开的。所以程序编制比较清晰,但对I/O接口的处理能力不强,只受某些指令的控制,不能通用。

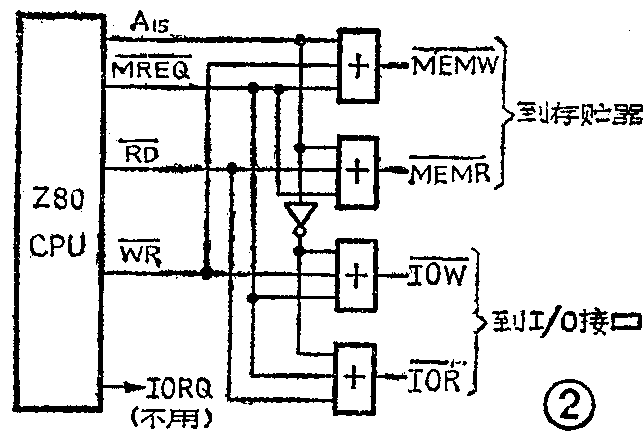

统一编址方式是把I/O接口当作存贮单元对待,统一安排地址号。按这种方式编址,访问存贮器的各种指令,也可用于访问输入输出接口所接外部设备。所以中央处理器对I/O接口的数据处理能力强。I/O接口和存贮器可以共用译码和信号控制系统。这种编址方式的硬件结构如图2所示。从图中可以看出A\(_{15}\)的作用是区分访内存贮器还是访问I/O接口。A15=0时是访内存贮器操作,A\(_{15}\)=1时是访I/O设备。由于这种编址占用了一条地址线A15,所以内存的容量是2\(^{15}\)=32768=32K。

编址方式确定以后,对存贮单元和I/O接口还要进行具体的编址,这实际上是如何正确使用地址线。

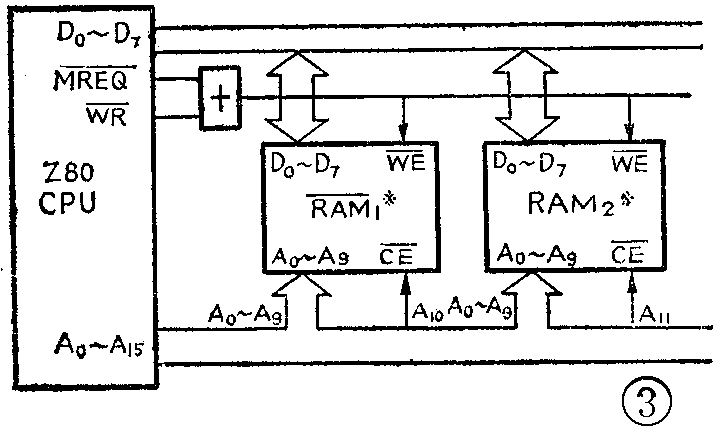

存贮器是由多片芯片组成,一般片内地址线可以和地址总线直接相连,而片选端的地址线连接比较复杂。通常有三种方法。线选法、译码选址法和复合选址法。

线选法是指定地址线中某几位直接和芯片的片选端相连,作为片选信号。

图3是两个芯片组成的2K存贮系统,图中RAM1,RAM2的容量均为1K×8位。每个芯片有2\(^{1}\)0=1024个八位存贮单元。芯片的开放信号CE-低电平有效。地址线A\(_{0}\)9直接接片内地址线作为片内寻址(片内1024个单元共有1024个地址)。其余的地址线作为片选信号。假如用A\(_{1}\)011作片选信号,A\(_{1}\)0=0选RAM1,A11=0选RAM2。其余地址线留作扩大存贮器容量时使用。

A\(_{0}\)15这十六根地址线中,以A\(_{1}\)0=0选中RAM1芯片,其它五根地址线(A11\(_{15}\))可以为任意状态这五根地址线共有2\(^{5}\)=32个状态,所以RAM1芯片中每个单元又有32个地址编号;A11=0选中RAM2芯片,同理它的每个存贮单元也有32个地址编号,这样就会发生地址的重迭。

\(_{1}\)0=0时,其它地址线可以为任意状态,若这时A11=0,而A\(_{12}\)15为任意状态,CPU将会同时选中RAM1、RAM2两个芯片,使程序出错。要保证CPU执行一条指令只选中一个芯片,即地址是唯一的,必须对其它地址线作出规定。当A\(_{1}\)0=0 A11=1选中RAM1,A\(_{1}\)0=1 A11=0选中RAM2,A\(_{12}\)15不接芯片,可以取任意状态,这里规定它们为零。这样每个单元的地址就确定了。

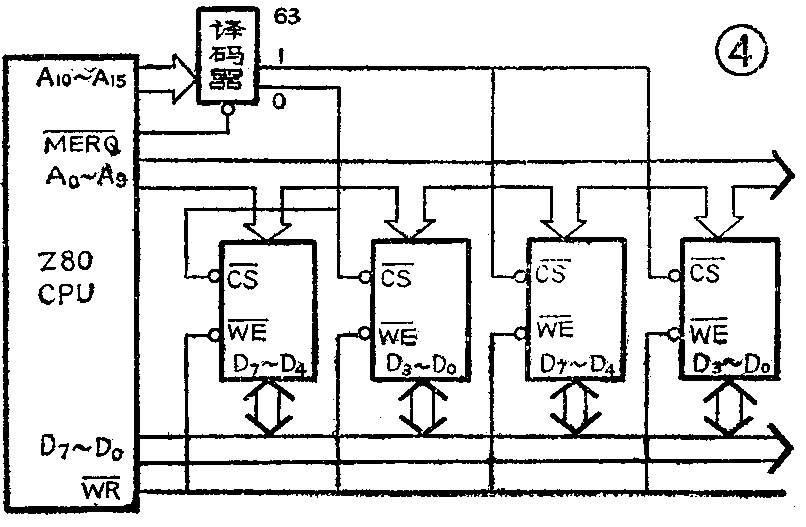

系统中存贮器容量较大时,采用线选法就不能满足要求了,就应采用译码选址,译码选址又分为全译码电路和部分译码电路。

图4是全译码选址电路,芯片用INTEL2114,是1K×4位的芯片。用4片这样的芯片构成一个RAM系统A\(_{0}\)910条地址线直接与芯片的地址连接作片内寻址,A\(_{1}\)015接译码器,译码后可产生64条选择线(2\(^{6}\)=64),控制64组芯片,这里只用了两条选择线,这种译码电路比较复杂但每组地址是单独的。

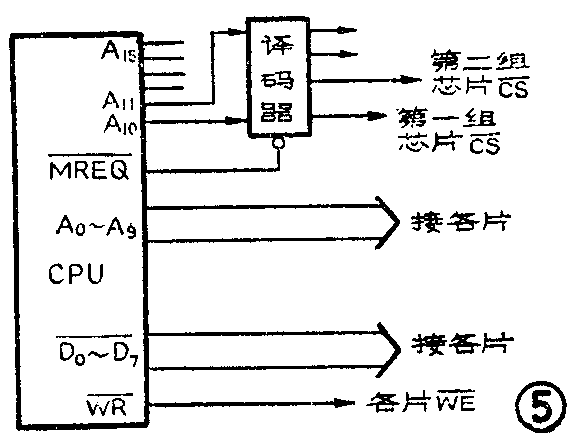

图5是部分译码选址的电路,芯片仍用2114。地址线用A\(_{0}\)9作片内选址。A\(_{1}\)011经译码后作组选择,两条地址线有2\(^{2}\)=4状态,即译码后可以控制4组芯片,在这里只用了两组。当A\(_{12}\)15为任意状态时仍可选出这两组。这样芯片中每一存贮单元有16个地址编号(对应A\(_{12}\)15的16种状态)。所以这种译码方式仍存在着地址重迭问题,使用中应注意。

由于存贮器的结构不同,译码器种类不同,各种器件负载能力也不一样。在实际组织一个系统时往往还要加入一些逻辑电路或者采用多级译码等方法。(刘福之)