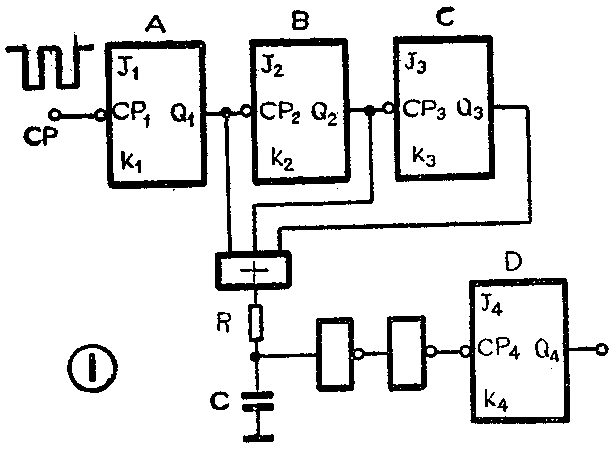

JK触发器在电子技术中的应用是相当广泛的。本文介绍的是用JK触发器和门电路以及RC网络构成的间歇定时电路,其原理电路如图1所示。下面我们来说明电路的功能及RC网路的作用。

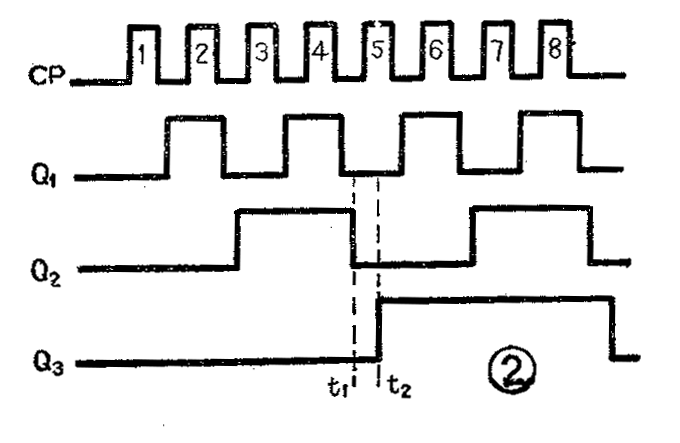

图中的A、B、C、D四个触发器的J端和K端接高电平,即J=K=1。图中,低位触发器A的Q\(_{1}\)端接高位触发器B的CP2端,B的Q\(_{2}\)端接C的CP3端,所构成的是三位二进制计数器。我们知道,计数状态的功能是:每有一个CP脉冲作用(负向跳变的下降沿)后,触发器的状态就翻转一次。这样,每有两个时钟脉冲CP输入,触发器A的状态即可翻转两次,而输出一个脉冲。同理,每输入八个时钟脉冲,可使触发器A输出四个脉冲,B输出两个脉冲,C输出一个脉冲。假设计数器的初始状态为“000”,CP为八个等时间的脉冲,经过CP脉冲的作用后,则A、B、C的输出Q\(_{1}\)、Q2、Q\(_{3}\)又为“000”。其波形如图2所示。

在图1中,触发器的输出端Q\(_{1}\)、Q2、Q\(_{3}\)均接到或门的输入端。而或门的逻辑功能是:只要输入信号中有一个是高电平“1”,其输出就是“1”;只有所有的输入信号全为低电平“0”时,输出才为“0”。所以在上述初始状态时,或门的输出为低电平“0”。经过两级非门后,作用于触发器D的负脉冲使其状态改变一次。综上所述,这个电路的功能可以叙述为:每隔8t时间(t为外加时钟脉冲周期),触发器D的状态就改变一次。若触发器D的一种状态可使它所控制的电路工作,则另一种状态可使其控制的电路停止工作,这就可实现间歇定时。

另外,由图2可以看出,各位触发器的翻转时刻是不同的。由于每位触发器的计数脉冲都是来自低位触发器的输出端,所以各触发器的翻转是从低位到高位顺序进行的。又因计数器状态的变化有可能是两个以上的触发器翻转,这时就有可能出现干扰脉冲。例如,在第四个时钟脉冲作用以后,A、B、C三个触发器均要翻转,但翻转的时刻一位比一位错后,这就可能在t\(_{1}\)~t2这段时刻(为便于分析,t\(_{1}\)~t2的间隔画的很大)出现了暂时的“000”状态。这将使或门输出一个暂短的“0”电平。若没有RC网络,这一“0”电平经两级非门后,使D触发器误翻转,这种现象在数字电路中称为“竞争冒险”。有了RC网络以后,当或门出现暂短的“0”电平时,电容C(原为高电平)通过电阻R向或门的输出端放电,由于这个“0”电平的时间极短,未等C上的电压降到非门的转换电子时,“0”电平就消失了,不会使两级非门输出负脉冲,从而消除了电路中的“竞争冒险”问题。(苏长赞)