⑤包络发生器——它可以在PSG被选择为包络控制情况时,产生具有特定波形的包络,而无需CPU逐点控制。以后还要详述这一问题。⑥数/模转换器——在这个转换器中有三个分别与三个通道相对应的数/模转换器,每个转换器可以产生十六个等级的模拟输出,用来把各寄存器中的数字量转换为模拟量。

(4)通用I/O口子。AY—3—8910PSG有二个8位I/O口子(AY—3—8912有一个),这二个通用I/O口子与PSG本身的音响部分没有直接关系。实际上它只是一个8位的双向数据锁存器,作用是提供了一个控制同音响有关的外围电路工作用的接口,这二个口子与其它设备的TTL电平完全兼容。

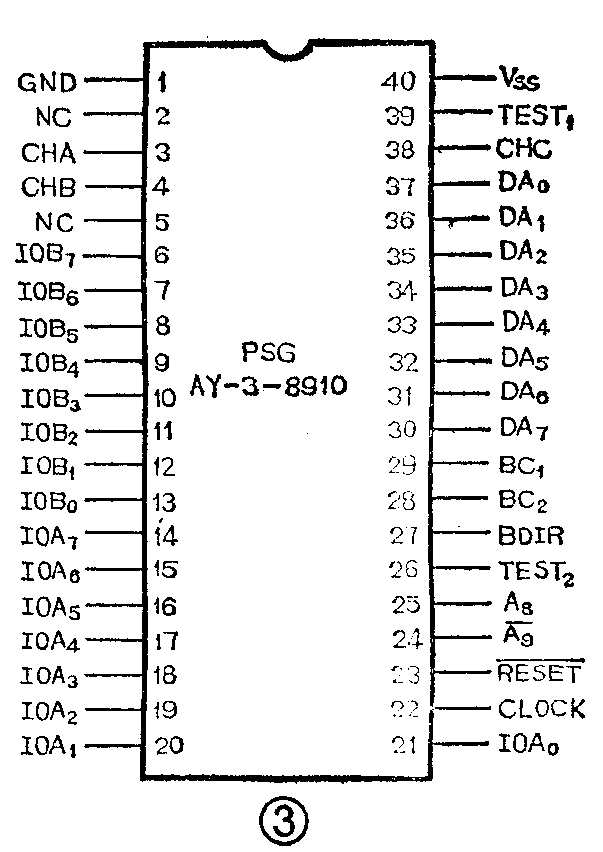

PSG的引脚分布及其功能

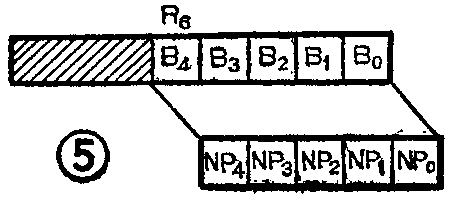

PSG的引脚分布(见图3)。引脚说明:1——地线。2——无用。3——通道A输出。4——通道B输出。5——无用。6~13——B口数据输入、输出线(8根),IOB7为数据线最高位,IOB0为数据线最低位。14~21——A口数据输入、输出线,IOA7为数据线最高位,IOAO为数据线最低位。22——时钟,频率范围为1.5~2MHz,作为乐音和噪声频率的基本时钟,与TTL电路兼容。23——复位线,低电平有效。24、25——附加地址线,24为低电平有效。它们与数据/地址线DA\(_{0}\)7(30~37脚)组合在一起可以在不附加译码器的情况下使直接寻址范围增加到1024字节,从而使得PSG中的每个寄存器可作为CPU的一个存贮单元来访问。若不用这种方法,这两个脚也可作为PSG的片选来使用。26——芯片测试引脚。27~29——PSG总线方向控制线,其中:27—BDIR,总线方向控制;28——BC\(_{2}\),总线控制2;29——BC1,总线控制1,27~29各线上加有不同数码信号时所起的作用见表1。30~37—数据/地址线。这些既是PSG中寄存器地址的选择线,又是PSG的数据线(双向,三态,即输入、输出、高阻)。38——通道C输出。39——芯片测试引脚。40——电源线(+5V)。

PSG各寄存器的功能及使用方法

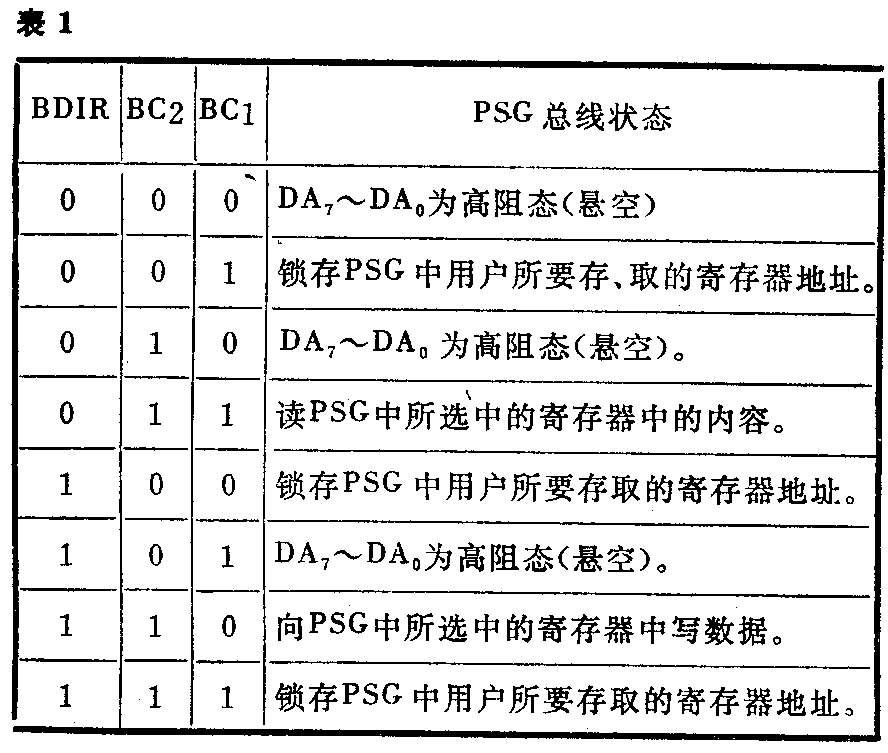

寄存器R\(_{0}\)~R5——乐音周期寄存器,其中R\(_{0}\)R1、R\(_{2}\)R3、R\(_{4}\)R5分别对应A、B、C三个乐音通道。下面仅以A通道所对应的乐音周期寄存器为例加以说明。

A通道乐音周期寄存器共12位,由寄存器R\(_{0}\)八位及R1的四位组成(见图4),其中TP\(_{11}\)为乐音周期的最高位,TP0为乐音周期的最低位。乐音周期产生过程是PSG内部计数器先对系统时钟(PSG时钟)进行16分频(PSG内部自动实现),然后再用所得结果对乐音周期寄存器中的周期数进行减法计数得到的。由于对乐音周期寄存器中的周期数进行的是减法运算,所以乐音周期寄存器所能存储的数值范围是000000000001~111111111111(十进制的1~4096)。频率的计算公式为ft=fclock/16·TP。其中ft——用户所希望的频率;fclock——系统时钟频率;TP——乐音周期寄存器中的十进制数据。例如:系统时钟频率fclock=2MHz,当想使该通道发出音高为中央C(261.6Hz)时,根据以上公式,送入该通道的周期数TP=fclock/16·ft=\(\frac{2×10}{^{6}}\)16×261.6≈478(000111011110)。将周期寄存器的范围数值1及4096代入上式,就可以算出,当fclock=2MHz时,ft的范围为30.5Hz~125kHz。寄存器R\(_{2}\)、R3以及R\(_{4}\)、R5分别对应乐音通道B和C,原理与乐音A相同。

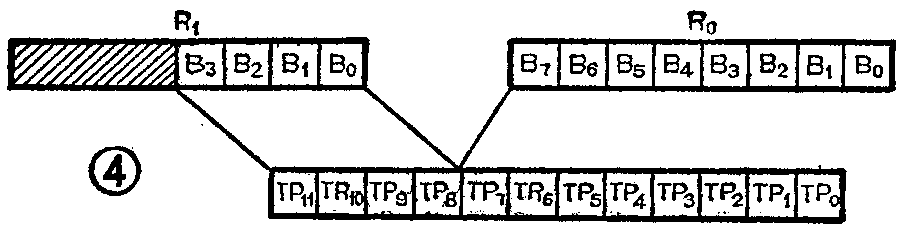

寄存器R\(_{6}\)——噪音周期寄存器。用来产生白噪音所需要的频率。作用及工作原理与乐音周期寄存器相似。其中只用该寄存器的低五位,见图5。该寄存器的数据范围是00001~11111(十进制的1~31)。频率计算方法与乐音周期相同,即fN=fclock/16·NP。其中f\(_{N}\)——用户所希望的噪音频率。fclock——系统时钟频率。NP——噪音周期寄存器中的十进制数(1~31)。若fclock=2MHz,则fN可用上式算出,范围是4kHz~125kHz。

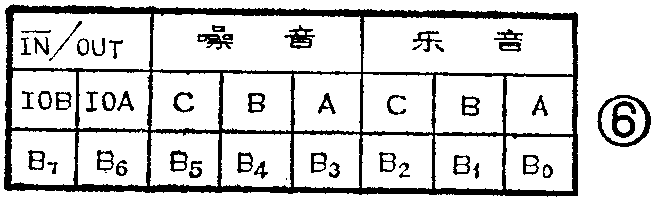

寄存器R\(_{7}\)——混合及I/O选通寄存器,用来选通三个乐音通道A、B、C和三个噪音通道A、B、C,以及二个I/O口子的读或写(见图6)。

本字节定义为:如乐音通道和噪音通道所对应的位为“0”,则打开该通道(即使该通道输出);如为“1”,则关闭该通道。IOA,IOB所对应的位为“1”,则该口子为数据输出态;为“0”,则该口子为数据输入态。例如:该寄存器送数据为11011101时,则IOA口子和IOB口子为数据输出态;同时打开噪音通道C和乐音通道B,关闭噪音通道A,B和乐音通道A,C。

注:当某一通道打开后,不能靠把它所对应的位予以置“1”的方法来关闭该通道的音响,而只能用把该通道所对应的幅度寄存器置“0”的方法来实现。

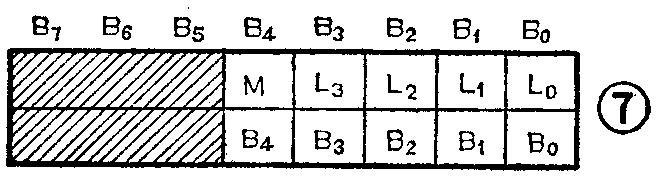

寄存器R\(_{8}\),R9,R\(_{1}\)0—通道幅度寄存器。这三个寄存器用来分别控制A,B,C三个通道的幅度。现以R10为例加以说明(见图7)。当M=0时,PSG中自动选通幅度控制器,而使包络发生器不起作用。这时音响的幅度仅由该寄存器的低四位(L\(_{3}\)~L0)来控制,其幅度的变化范围是0000~1111(十进制的0~15),即有十六个幅度级别。用户可以通过改变该寄存器中的数据来实现所希望的不同级别的包络。当M=1时,则选通包络发生器,此时音响的幅度改变与L\(_{3}\)~L0无关,而是由包络周期寄存器的数据以及包络形状/周期寄存器的数据来控制。包络发生器控制时,它输出的幅度级别只有十六个,具体的用法是由以下的包络周期寄存器和包络形状/周期寄存器决定的。

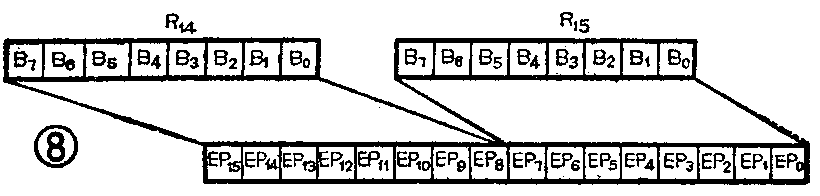

寄存器R\(_{11}\),R12——包络周期寄存器(见图8)。它用于PSG控制包络时产生包络周期。PSG包络周期产生的过程是:PSG内部计数器先对系统时钟(PSG时钟)进行256分频(PSG内部自动实现),然后再用所得结果对包络周期寄存器中的周期数进行减法计数来实现的。由于包络周期为十六位,故包络周期可表示的范围是0000000000000000~1111111111111111(十进制数的1~65535)。计算包络频率的公式为f\(_{E}\)=fclock/256·EP。其中fE——用户所希望的频率;fclock——本系统时钟的频率;EP——包络周期寄存器中所包含的数值的十进制形式。

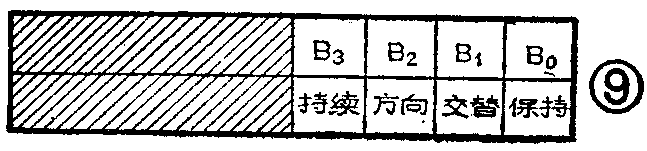

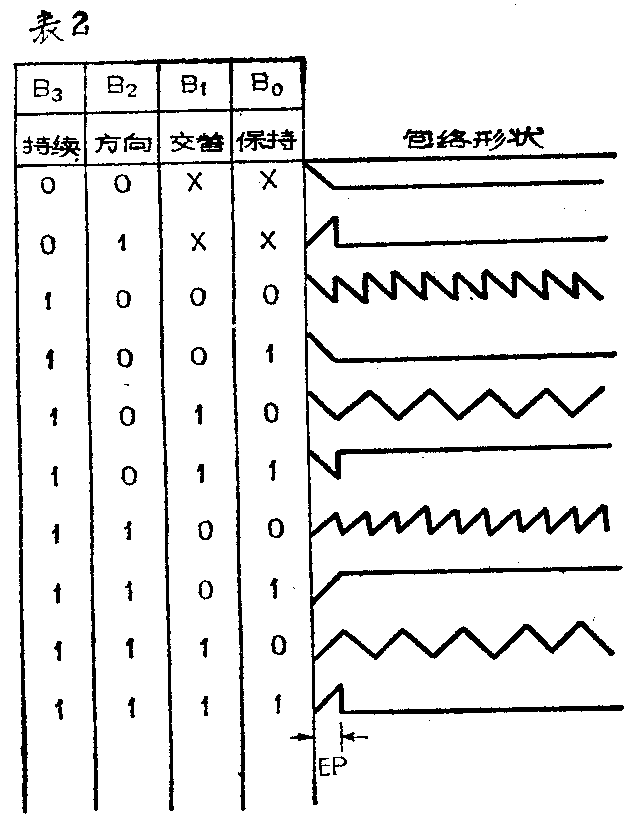

寄存器R\(_{13}\)——包络形状/周期寄存器(见图9)。该寄存器只用其低4位(B3\(_{0}\)),用户通过对这4位写入不同“0”和“1”的组合,将产生不同的包络形状,每个包络周期都划为16个等级,使得每个包络周期中,包络发生器的输出有16个不同的输出电压每输出电压状态维持1/16包络周期。

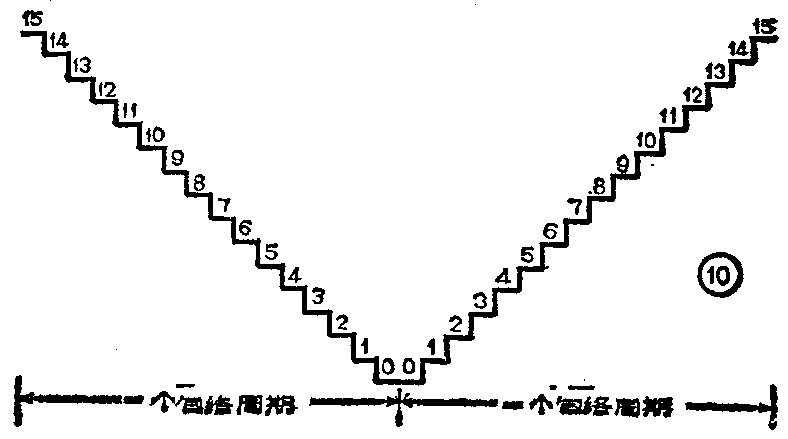

在PSG中有一个专门用于包络控制向上或向下的计数器(可逆计数器)。该计数器每次加1或减1,都使包络输出的幅度加1或减1。这个计数器为四位。每个周期计数一次,数值从0~15或从15~0,而且计数是连续的,此数终点只有0或15两种状态(见图10)。

下面介绍该寄存器的具体用法(见表2)

B\(_{0}\)——保持,若B0=1,则使某一形状的包络波形只出现一个周期,且在该周期结束时保持该周期结束时的幅值(0或15不变)(见表2中从上数第4个波形),若B\(_{0}\)=0,则上述作用消失。B1——交替。若B\(_{1}\)=1,则包络向上/向下计数器在包络周期结束时向反方向计数(见表2中从上数第5个波形)。

注:当B\(_{0}\)=B1=1时,包络计数器在保持之前计数值恢复到计数初值(见表2中最下面的波形)。B\(_{2}\)——计数方向。B2=1,则向上/向下计数器从0到15计数,否则从15到0计数(见表2中的自上数第7个波形及第3个波形)。B\(_{3}\)——继续,若B3=1,则包络形状由B\(_{0}\)来决定;若B3=0,则一个周期结束时,将计数器置0且保持(见表2中第4个及第2个波形)。注:表2中×表示与此无关。

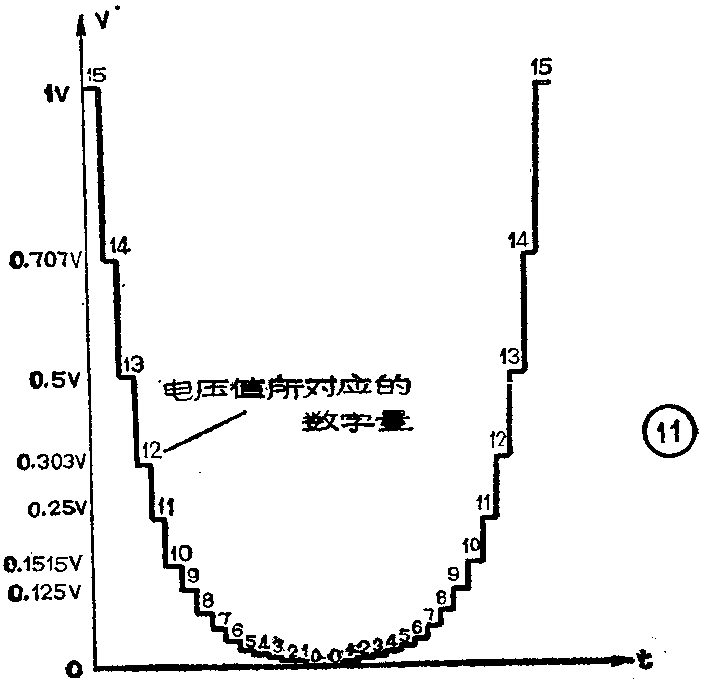

数/模转换器——数/模转换器内有三个分别对应A、B、C通道的数/模转换器。用来把幅度控制器,包络发生器中的数字信息转换成输出的模拟电压信号。对应于数字量,其相应的电压量也有0V~1V之间的16个等级的电压量输出(见图11)。

寄存器R\(_{14}\)、R15——通道输入/输出端口。这两个端口与PSG的音响部分无直接关系,只是考虑到与CPU和其它外部设备相互传递信号和数据而设置的。该口子相当于两个8位双向数据锁存器(触发器)。下面以A端口为例子说明如下:

CPU利用PSG的A端口向外部设备送数据的步骤:①选择寄存器R\(_{7}\)(锁存寄存器R7地位);②设置I/O口A为输出状态(寄存器R\(_{7}\)6写“1”);③选择寄存器R\(_{14}\)(锁存寄存器R14的地址);④把利用I/O口子向外设所送的8位数据写入寄存器R\(_{14}\)。

CPU利用PSG的I/O端口从外设读数据的步骤是:选择寄存器R\(_{7}\)(锁存寄存器R7的B6写“0”,③选择寄存器R\(_{14}\)(锁存寄存器R14的地址),④CPU从PSG的I/O口A读取数据。(康跃伟)