电子数字计算机、数字化仪器仪表以及形形色色的数控装置,都离不开电子计数器。电子计数器的核心是一种具有记忆功能的电路——触发器。本文从晶体管开关谈起,引出分立元件触发器,再进一步介绍目前广泛应用的集成电路触发器的基本原理。

具有“自锁”功能的晶体管开关

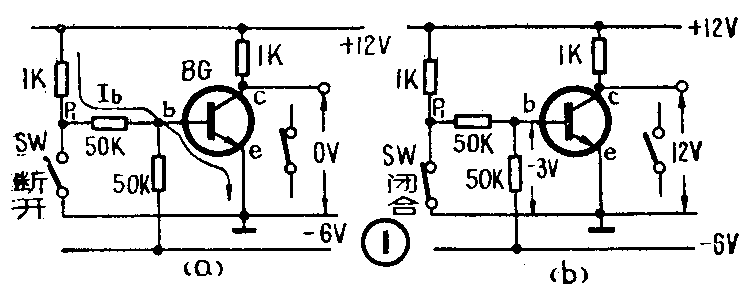

图1是大家熟悉的晶体管开关电路。当手动开关SW断开时,就会有足够大的基极电流I\(_{b}\)注入晶体管BG,使晶体管饱和,这时c、e两极之间如同一个接通的开关,所以集电极电压Vc≈OV,电路输出低电平“0”;当手动开关SW闭合时,晶体管BG的基极电位V\(_{b}\)=-3V,管子被迫截止,其c、e两极之间相当于一个断开的开关,所以集电极电压Vc=12V,电路输出高电平“1”。把上面这种关系归纳起来如表1所示。

表 1

SW的状态 P\(_{1}\)点电平 晶体管状态 集电极电压

断 开 高 饱 和 低

闭 合 低 截 止 高

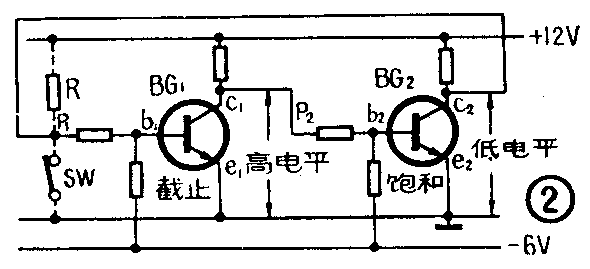

把两个图1所示的开关连接成图2的形式,让BG\(_{1}\)的集电极输出端接在BG2的基极输入端,再将BG\(_{2}\)的集电极输出端引回到BG1的基极输入端,成为一个两级正反馈放大器的闭合环路。当手动开关SW闭合时,BG\(_{1}\)截止,c1、e\(_{1}\)间相当于断开的开关,使BG2饱和,于是c\(_{2}\)、e2间又相当于接通的开关,经反馈线使P\(_{1}\)点为低电平“0”,能保证BG1的截止。这时,即使去掉手动开关SW和电阻R(图中虚线部分),电路也能持续地保持BG\(_{1}\)截止、BG2饱和的稳定状态。因此,可以把这个电路看作一种具有自锁功能的晶体管开关。

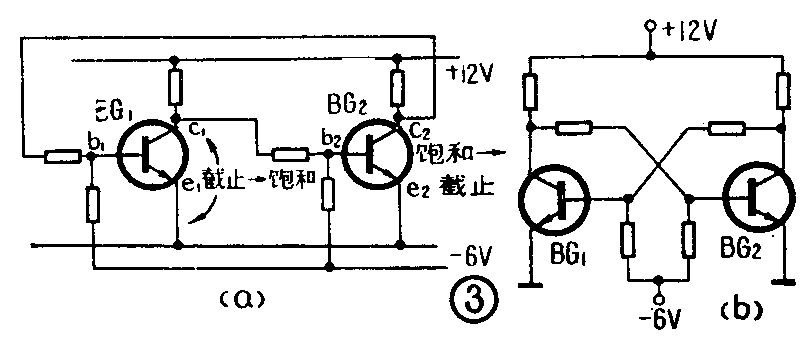

如果我们把图2中饱和管BG\(_{2}\)的基极在一瞬间强迫它变为低电平“0”,BG2就会顿时截止,集电极输出为高电平,通过正反馈使BG\(_{1}\)迅速饱和,C1变为低电平,又确保BG\(_{2}\)截止,电路就处于另一个稳定状态,(图3(a))。

由此可见,图2所示的电路具有两个稳定状态,因此常称它为双稳态触发器,简称为触发器。

一触即发——触发器的翻转

图3(a)是分立元件触发器的典型电路,图3(b)是它的习惯画法。显然,它是由两个晶体管反相器交叉耦合组成的对称电路。

假定触发器原来处于BC\(_{1}\)截止、BG2饱和的稳定状态,这时只要用一根导线把c\(_{1}\)、e1间短路一下,就会使BG\(_{2}\)立即变为截止,通过正反馈作用使BG1变为饱和。这就是说在外来信号作用下,触发器会从一种稳定状态迅速改变成另一种稳定状态,这个过程称为触发器的翻转。

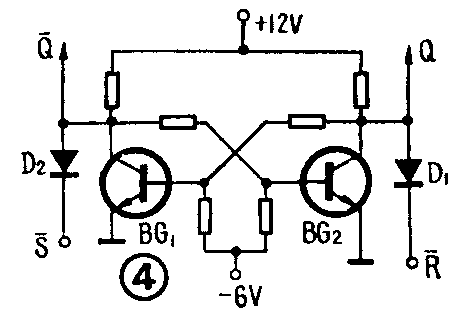

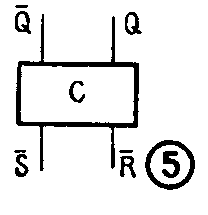

在数字系统中,我们把触发器的两个输出端分别命名为Q和Q-(表示两输出端的状态正好相反,当Q端为“1”时,Q-端为“0”;Q端为“0”时,Q-端为“1”)。S-与R-端分别通过二极管D\(_{1}\)和D2作为触发信号的输入端子(图4)。如果R-端输入低电平(或负脉冲),则BG\(_{1}\)截止、BG2饱和,Q端为低电平“0”,这个过程叫置“0”;若给S-端加上低电平(或负脉冲),则BG\(_{2}\)截止、BG1饱和,Q端为高电平“1”,这个过程叫置“1”。因此,图4所示的触发器称为R—S触发器或置“0”——置“1”触发器,有时也称为“复位—置位”触发器。它的逻辑符号如图5所示。

集成电路“与非”门构成的R-S触发器

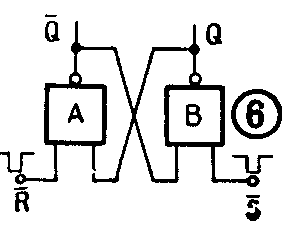

把两个集成电路“与非”门交叉耦合起来,就可以构成基本的R-S触发器,如图6所示。

假设开始时输入端R-和S-都处于高电平,输出端Q为高电平“1”,Q-为低电平“0”。当R-由高电平变为低电平时,A门的输出便由低电平变成高电平,即Q-=1。由于B门的反相作用,使B门的输出由高电平变成低电平,即Q=0。B门的输出再反馈到A门的输入端,就能确保A门输出高电平(Q-=1),这时即使R-又回到高电平,电路也能维持Q=0的稳定状态,这就是触发器的置“0”。反之,当S-端由高电平变为低电平(R-保持高电平)时,就会使Q=1,Q-=0,这就是触发器的置“1”。R-S触发器的逻辑功能可用表2所示的真值表表示。需要指出,R-=S-=0的状态是不允许的,它会破坏触发器的逻辑关系,使数字系统工作紊乱。

表 2

R- S- Q

0 1 0

1 0 1

1 1 不变

0 0 不允许

R-S触发器改造成T触发器

在计数电路中,为了进行累计计数,要求每来一个计数脉冲,触发器的状态翻转一次,最简单的具有这种功能的触发器是T触发器。

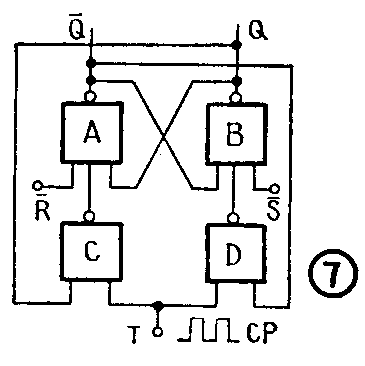

图7是由四个“与非”门组成的T触发器。A“与非”门与B“与非”门组成基本R-S触发器,C“与非”门与D“与非”门是引导门,计数脉冲(通常叫时钟脉冲)CP由T端输入。

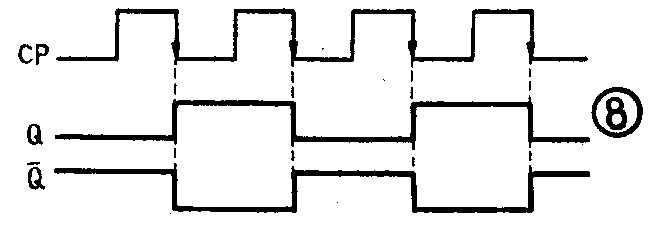

图中C、D“与非”门分别受触发器输出端Q和Q-控制。当Q=0,Q-=1时,D门的一个输入端为“1”,为迎接时钟脉冲CP做好了准备,而C门的一个输入端为“0”,即使CP脉冲到来时也不能“开门”。当T端有时钟脉冲CP输入,T端由低电平跳变到高电平(CP= 1)时,D门即输出一个负脉冲去触发B门,使Q=1,而A门的两个输入端都变成“1”,所以Q-=0。这时,Q端的“1”反馈到C门的输入端,使它处于“开门”状态,为迎接下一个时钟脉冲做好准备,D门的输入端被Q-=0封锁,处于“关门”状态。下一个时钟脉冲CP到来时,C门就输出一个负脉冲去触发A门,使触发器变成Q=0,Q-=1。这样,利用门C和门D的引导作用,触发器每输入一个时钟脉冲就会翻转一次,达到计数的目的。图中R-和S-端子也是用来给触发器置“0”和置“1”的。T触发器输入与输出的波形图如图8所示。

图7所示的触发器虽然具备了计数功能,但在实际应用时会发生空翻现象,工作不可靠。为此,人们又设计了D触发器、JK触发器等等,一、二个触发器的全部线路集中制作在一小块硅片上,封装在一个外壳中,使用起来十分方便。(张晋纯 宋东生 编译)