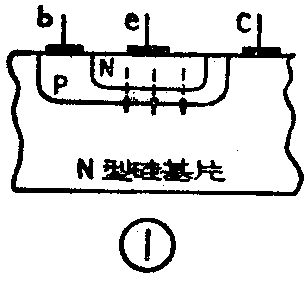

早期生产的集成运算放大器是在硅平面管工艺的基础上发展起来的。所谓平面管工艺,是利用如图1所示N型硅基片(作为集电区)通过一定的工艺措施向基片扩散P型杂质,使N型基片上形成一块具有一定面积及一定深度的P型区(作为基区),然后再向这块P型半导体上的一部分进行更高浓度的N型杂质扩散,使在P型区内再形成一个N型区(作为发射区)。控制第二次扩散层的深度,使图1所示这个具有N、P、N三层结构的基区尽可能窄一些,就能做出具有较高β值的硅NPN晶体管。由于这种晶体管的基片表面是平坦的,它的三个电极都可以从基片表面引出,故称为“平面管”,而制造这种管子所采用的工艺即称为“平面工艺”。由于硅平面管工作时,载流子(电子)自发射区通过基区向集电区注入,是纵向流动的,如图1中的箭头所示,因此硅平面管都是纵向工作的。

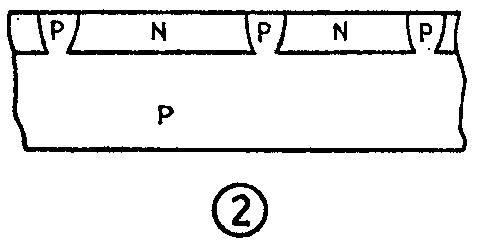

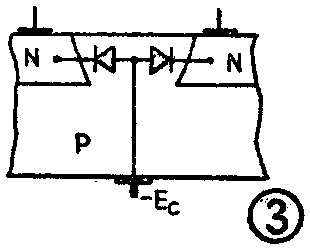

对于集成电路来讲,除了要在硅片上制造出若干晶体管及电阻外,还必须解决各晶体管以及电阻等元件之间相互隔离的问题。目前在国产集成运放中大多数厂家均采用‘PN结隔离”工艺。所谓PN结隔离,就是在制造电路时先在P型衬底材料(P型基片)上很薄的N型半导体外延层表面,通过扩散P型杂质的办法,把这层N型材料分割包围,使之形成一块块孤立的N型半导体“小岛”,如图2所示,再在各个小岛上通过平面工艺做成晶体管、电阻等元件,它们各自被与衬底相连的P型半导体材料分割包围。如果把P型衬底材料接电源最低电位-E\(_{C}\),即可保证它相对于各岛状的N区都是反偏的,因此做在岛状N区内的各元件均被反偏的PN结所隔离,如示意图图3所示。由于反偏PN结呈现很高的阻抗,这就使同一硅片上的各个元器件相互间实现了高阻抗隔离。

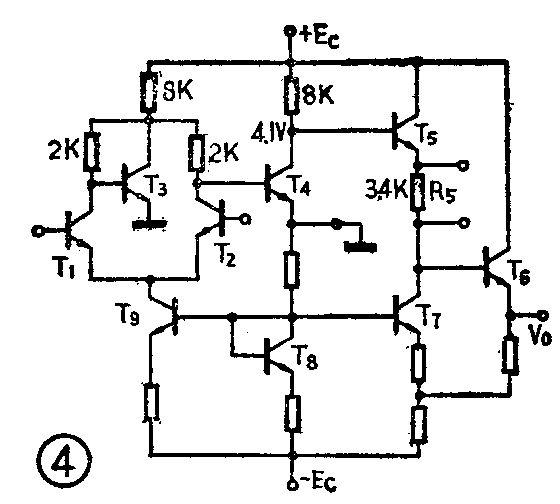

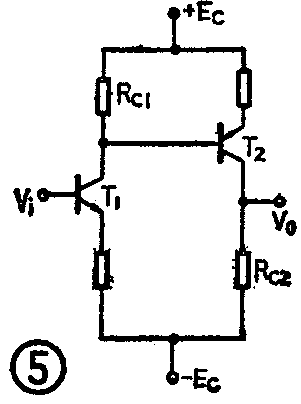

图4所示通用运算放大器F002就是采用这种工艺、均由NPN管组成的第一代集成运算放大器电路。为了提高集成运放的性能,在电路设计中如能像分立元件电路那样灵活地把PNP管与NPN管电路加以组合,即可解决单纯采用NPN管设计电路的一些缺点而大大提高集成运算放大器的某些指标,如:在NPN管多级直耦电路中,为使晶体管工作在放大区,其发射结应该正偏而集电结应该反偏,这就使每级共射电路的直流输出电位均比输入高若干伏。因此经过几级放大后,其输出端直流电位将大大高于输入端电位,如图4所示F002电路经两级共射放大后,其V\(_{c4}\)已被抬高到4.1V。虽经末级射极跟随器输出时每经过一个PN结可使其直流电位降低约0.6V,但仍无法实现V\(^{i}\)=0时Vo=0。因此在设计集成运算放大器时都必须解决所谓“电位移动”问题,即把经过几级NPN管共射放大后被抬高了的直流电位降低到能在静态(Vi=0)时使V\(_{o}\)为零的低电位值。F002电路中的电位移动是通过晶体管T5的工作点电流流过电阻R\(_{5}\)所产生的直流压降实现的。但是,信号通过R5传输到功放级T\(_{6}\)的过程中在R5上也要产生一定的损耗,因而将使增益降低。若能利用PNP管共射电路与NPN管共射电路耦合如图5所示,则可很方便地在级联放大的同时使通过第一级放大被抬高了的直流电位经第二级放大后大幅度向负端移动。这是一种非常理想的电位移动方案,因而在较成熟的集成运放电路中均采用一级PNP管电压放大,以解决电位移动问题。

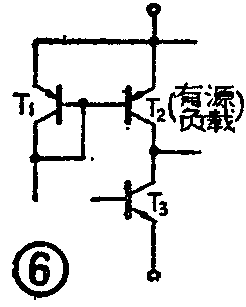

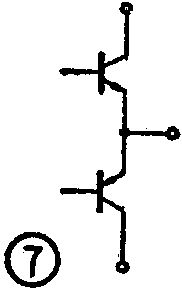

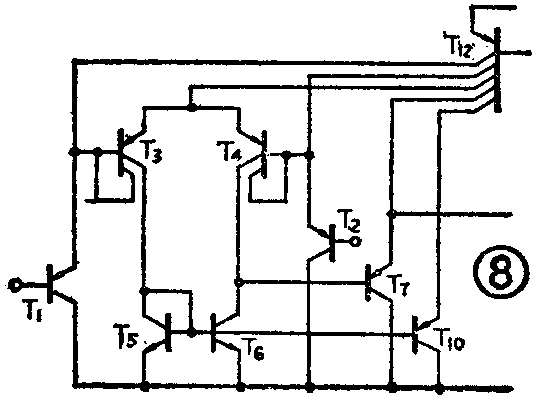

此外,在第一代通用运放中,由于共射电路的集电极负载R\(_{c}\)均采用基区扩散电阻(在制造基区的同时而制成的电阻),由于放大器工作点电流及工艺上的限制,这些电阻不能取较大的值(第一,Rc值大则电阻区长度长,将占用硅片大片面积使成本提高;第二,R\(_{c}\)的大小将受放大器工作点电流的限制),如F002第一级Rc=2K,第二级R\(_{c}\)=8K。由于Rc过小就大大限制了第一代集成运放总增益的提高。若能采用电流源(即所谓“有源负载”,其动态电阻很大)作为共射电路的R\(_{c}\),不但可解决一定的工作点电流与高阻值Rc的矛盾以提高增益,而且制造一个晶体管所占用的硅片面积要比做一个大电阻小得多,因此还可以降低器件的成本。但NPN管共射电路只能采用PNP管组成它的有源负载,如图6所示。因此在一个较复杂的集成运放中需要为数较多的PNP管构成电流源电路。最后,对NPN管直耦电路如F002,由于只能采用射随器甲类功率放大,因而静态功耗大而效率很低。为克服这个缺点也必须采用如图7所示NPN、PNP晶体管组成的甲乙类(如F006、F007)或乙类(如E003、F005)互补射随功率放大级,以减小器件的静态功耗。此外,对于某些特殊类型的电路如图8所示单电源运放8FC7(图中仅画出输入级)为实现在单电源工作时两输入端能加入为零、甚至为负(一般可达-0.5V)的共模电压,必须采用PNP管共集电极差分输入电路。因此,对于目前大量使用的双极型集成运放,在以NPN管为主的电路中还需要采用若干PNP管才能构成各主要技术指标都较为优越的电路。

然而,用生产NPN管的标准工艺是不大容易同时做出性能优良的PNP管的。为了充分发挥NPN管和PNP管互补电路的优越性,在制造集成运放时必须解决在一块硅片上制造这两种晶体管时工艺上的共容问题。

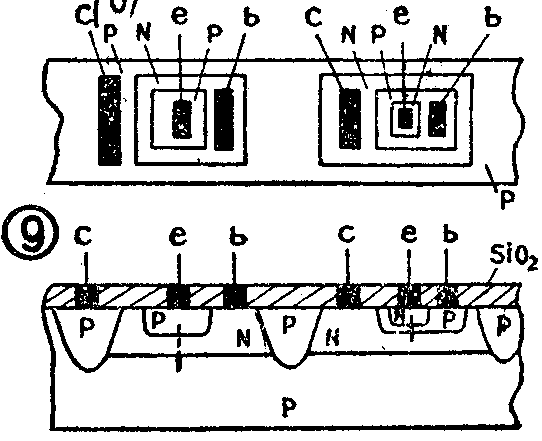

利用PN结隔离平面工艺制造NPN管时,在隔离岛上是做不出纵向结构的PNP器件的。通常采用的是所谓“衬底PNP管”和“横向PNP管”这两种PNP器件。图9左边所示为衬底PNP管,也称为纵向PNP管,右边为作为对比的NPN管结构示意图。由于采用PN结隔离,所以衬底PNP管是以P型衬底作为集电极的,岛状的N区就是它的基区,在制作NPN管的P型基区时同时制成了纵向PNP管的P型发射区。这种晶体管工作时由于载流子(空穴)是沿着晶体管断面的垂直方向运动的,如图9虚线箭头方向所示,所以称为纵向PNP管,又因为它是利用衬底材料作为晶体管的集电极,故也称为衬底PNP管。根据PN结隔离的要求,衬底PNP管在使用时其集电极必须接到电源最低电位端,所以它在电路中只能用作集电极接最低电位的共集电极电路等场合。如图8所示单电源运放8FC7输入级电路中的晶体管T\(_{1}\)、T2,输入级与中间级的隔离晶体管T\(_{7}\)以及输入级有源负载的偏置晶体管T10等均是。由于衬底PNP管的发射区P是在NPN管基区P扩散的同时形成的,因而它的基区N不可能严格控制在较窄的范围内,故其电流放大系数β低于NPN管,一般在10~50之间。而且高频性能也比NPN管差,其截止频率f\(_{T}\)约为10MHz。

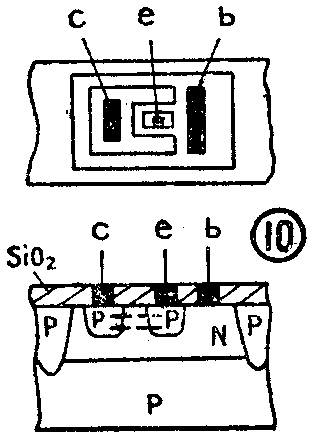

另一种结构的PNP管——横向PNP管如图10所示。横向PNP管的P型发射区和集电区是在制作NPN管的P型基区时同时形成的,它的N型基区则对应于NPN管的集电区。因为这种晶体管在工作时其载流子(空穴)是沿着断面的水平方向运动的,如图10中虚线所示,故称为横向PNP管。由于受到掩模光刻工艺水平的限制,横向PNP管集电区与发射区之间的间隔,即横向PNP管的基区不可能做得很窄,所以它的β值更低,一般在2~15之间,其典型值约为3~5。由于基区较宽,因而载流子通过基区时所需的渡越时间更长,频率特性更差,其截止频率f\(_{T}\)约在l~2.5MHz左右。因此横向PNP管仅限于用在必须采用的场合,如电位移动放大级及电流源等处。图8所示8FC7电路输入级差分放大管T3、T\(_{4}\)(因T3、T\(_{4}\)的集电极不是接至电源地端,故不能用衬底PNP管)以及作为输入级电路的电流源晶体管T12等均采用横向PNP管结构。

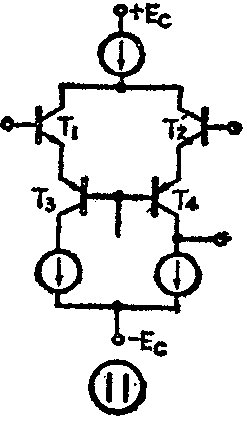

虽然横向PNP管具有β低、频响差的缺点,但由于它的发射区和集电区是同时形成的,因而集电区的掺杂浓度与发射区相同,而不像NPN管的发射区是第二次掺杂后形成的,因而杂质浓度高,所以NPN平面管发射结反向击穿电压远较集电结反向击穿电压低,一般只有6~8伏左右,而横向PNP管的发射结反向击穿电压与集电结基本相同,可达25~120伏。因而在电路设计中可以将NPN管与横向PNP管接成如图11所示共集—共基组态输入级差分电路(如通用Ⅲ型运放F006、F007,低功耗运放F010等)或其它复合组态输入级形式,即可充分发挥它的发射结反向击穿电压高的特点,大大提高了运算放大器的差模输入电压范围。通常这种复合输入级的差模输入电压范围指标可达±30伏以上,这也是为什么在输入级电路中常常引入横向PNP管的原因之一。

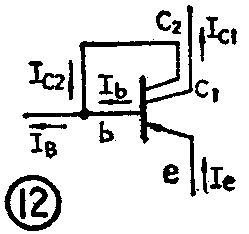

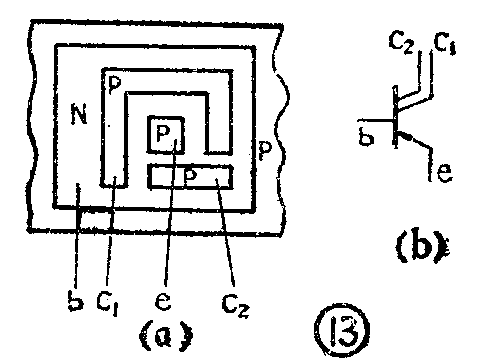

在PN结隔离集成运放中除去上述两种结构的PNP管外,还常采用如图12所示的称为“可控β横向PNP管”的结构,它是将双集电极横向PNP管的第二集电极C\(_{2}\)与基极b短接而成的。图13a是顶视图,表明了它的多极结构,13b是它的通用符号。采用这种PNP管是为了减小由于β随温度变化所引起的集电极电流漂移以及为了解决批量生产中横向PNP管β的离散性问题,这是因为将双集电极PNP管按图12的接法能够形成从C2到基极b的电流负反馈。这样,不管是由于温度变化还是由于不同批量生产所造成的横向PNP管的β=I\(_{C1}\)/Ib在较大范围内变动时,由于电流负反馈作用就使图12所示等效晶体管的β′=I\(_{C1}\)/IB值基本上不受这些因素影响而维持一个较为恒定的值。电流负反馈的深度与第二集电极电流I\(_{C2}\)的大小,亦即与第二集电极的面积有关。在设计晶体管时可以用控制两个集电极的面积比来控制它的β值,因此这种晶体管称为可控β横向PNP管。此外,由于引入一定的负反馈,因而它的β截止频率要比一般横向PNP管高一些。图8所示单电源运放8FC7输入级电路中的晶体管T3、T\(_{4}\)就采用了这种器件,此外在国产通用型运放BG303、BG305、低漂移运放F032等许多电路中也已经广泛采用了这种晶体管。

多集电极横向PNP管除去可以接成可控βPNP管用作增益级或电流源外,还可以利用它的多个集电极构成若干个电流源使用,而每个电流源所提供的电流大小与它相应的集电极面积成比例。如图8中的T\(_{12}\)就有5个集电极,相当于5个恒流源电路。(伯龄)