开环输入电阻是运算放大器的主要技术指标之一。在大多数情况下,我们总是希望集成运放的开环输入电阻大,而且经常把集成运放器件看成是理想器件,即认为它的开环输入电阻是无穷大的。

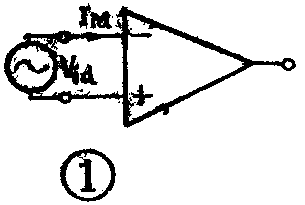

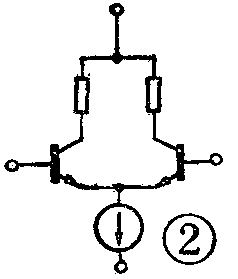

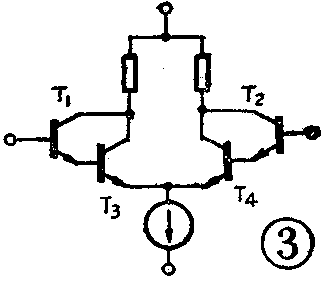

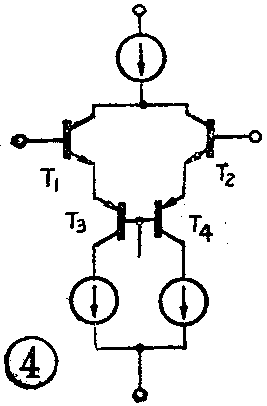

集成运放的“开环输入电阻”一般被定义为:开环运算放大器在室温下,加在它两个输入端之间的差模输入电压变化量ΔV\(_{id}\)与由它所引起的差模输入电流变化量ΔIid之比(见图1),并用符号R\(_{ID}\)表示。运算放大器输入电阻的大小取决于输入级电路的形式、输入晶体管的β值以及工作点电流的大小。由于绝大多数运算放大器输入级均由差分电路组成,因此输入级差分电路的输入电阻就是运算放大器的输入电阻。对于如图2所示的简单差分电路,我们已知其输入电阻RID=2r\(_{be}\),rbe为晶体管的输入电阻。r\(_{be}\)的阻值是较小的,因此RID也小。例如,通常CF702的R\(_{ID}\)只有20K左右。这个数字远较无穷大为低,这是这种器件的一个很大的缺点。为了提高器件的输入电阻,也常采用复合管差分输入电路。图3所示为高增益运放BG305的输入级,这种电路的输入电阻典型值为0.5MΩ至2MΩ。通用Ⅲ型运放的输入级电路如图4所示,其输入回路也由四个PN结组成,但因组态与BG305不同,(采用共集—共基组态)其输入电阻指标RID一般都大于于500KΩ。对于采用超β管作输入级差分对管的第三代集成运放如FO30、4E325、XFC78、XFC10、FC72、FO31等,虽然其输入级电路的基本结构与CF702相似,仍为普通差分放大电路,但由于工作点电流很低(约20μA比CF702低一个数量级),以及β值很高(1000~10000,比CF702高1~2个数量级),就使这种器件R\(_{ID}\)仍可高达1MΩ以上。如XFG-78的RID为5MΩ,FO30的RID>0.5MΩ。

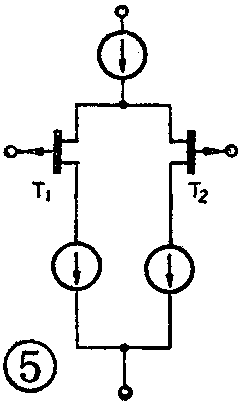

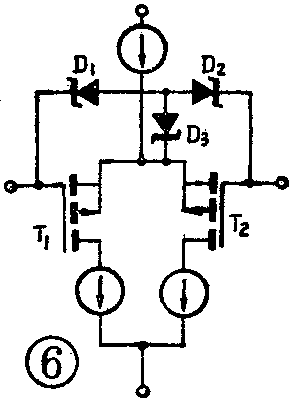

由以上几种电路输入阻抗的分析可以看出,在双极型集成运放电路中由于受输入级晶体管β及工作点电流的限制,要想进一步提高其R\(_{ID}\)指标是很困难的。为了满足某些应用电路对高阻抗器件的要求,生产厂家已研制出以J型场效应管作输入级的高阻抗运放5G28、XFC6、BG313等,其输入级电路如图5所示。图中T1、T\(_{2}\)为P沟道J型场效应管,由于J型场效应管的输入PN结工作在反偏状态,因而具有极高的输入电阻RGS(其R\(_{GS}\)的大小由工作在反偏状态的PN结漏电流确定,故输入电阻高,而双极型晶体管的输入PN结即发射结工作在正偏状态,故其输入电阻rbe很小),这种器件的R\(_{ID}\)可高达10\(^{3}\)MΩ以上。而以MOS场效应管作输入级的高阻抗单电源运放如F3140B、F3130、FO72等器件,其输入级电路如图6所示。图中T1、T\(_{2}\)为P沟道MOS场效应管,由于MOS管具有比J型场效应管高得多的输入电阻RGS,因而应该能够具有更高的R\(_{ID}\)指标,但由于这种器件的输入级均加有栅极保护二极管D1、D\(_{2}\)、D3,使两输入端之间并联了背靠背串接的两个稳压管,因此它的输入电阻也要受二极管反向漏电流的影响。这几种器件的输入电阻指标可达1.5TΩ(1.5×106MΩ)。此外,另一类全部由MOS场效应管组成的CMOS集成运放如5G14573、CH14573,其输入电阻也可达10\(^{4}\)MΩ以上。

还应该指出:在集成运放两输入端之间不仅表现出一定的输入电阻,由于存在着半导体器件的PN结电容及电路分布电容,在运放两输入端之间还有一定的输入电容C\(_{ID}\)。因此集成运放的输入阻抗ZID应该是输入电阻与输入电容的并联值。随着信号频率的增加,器件的输入阻抗将随之减小,但对于常规的双极型集成运放电路,由于它们的R\(_{ID}\)指标不高且工作频带也比较窄,因此输入电容的影响相对较小,一般不对器件的输入电容进行测试及考核。但对于以场效应管作输入级的高阻抗运放,由于它们的输入电阻很高,相对比起来输入电容的影响就比较突出,放在一些高阻抗运放电路中除去RID指标外,还同时给出输入电容指标,如F3140B的CID≤4pF,F3130的CID≤4.3pF。

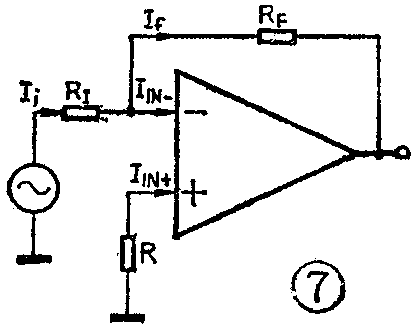

既然不同类型的集成运放在R\(_{ID}\)指标上相差这么多,那么我们在使用中应如何选择器件呢?当然,一般说起来是RID越大越好,这是因为R\(_{ID}\)高的器件其IIB也必然较小,这时才能近似认为运算放大器的输入端不吸收电流,即如图7所示有I\(_{IN+}\)≈0、IIN-≈0,这样才能近似把I\(_{N}\)-端看成虚地以及认为其输入电流Ii等于反馈电流I\(_{f}\),才能导出Vo=-I\(_{f}\)·RF=-I\(_{i}\)·RF=-\(\frac{R}{_{F}}\)RIV\(_{i}\)。即RID高、I\(_{IB}\)小的器件,其实际运算结果将比较接近理论值。因此当运放作为运算器应用并对计算结果要求较高时,应选用RID较高的器件。尤其在积分电路或是以积分器为核心的采样、保持等应用电路中,对R\(_{ID}\)及IIB就要求更为严格,近时应选用高阻抗运放如F3140B等。对于定时电路或要求较高的振荡电路也以选用R\(_{ID}\)较大者为佳。但对于大量用于比例放大的应用场合,因为对放大器闭环增益要求不很严格,因而选用一般的通用型器件即可。

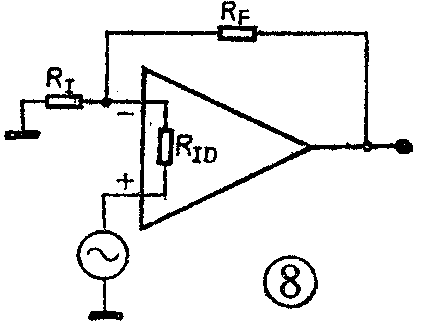

由于运算放大器的闭环增益公式及非线性应用电路中有关翻转时间的计算公式等,都是在假定集成运放的R\(_{ID}\)=∞、IIB=0的前提下推导出来的,因此在设计电路时应该注意所用器件的R\(_{ID}\)要与所设计的电路参数相适应。如图8所示电路中采用的器件为通用Ⅲ型CF741,其RID≥2MΩ。设计电路参数时应保证有R\(_{I}\)《2MΩ,一般小10倍或10倍以上即可。如取RI=200KΩ、R\(_{F}\)=1.8MΩ,这时的Avf≈1/F=1/\(\frac{R}{_{I}}\)RI+R\(_{F}\)=10。由图8可见,当器件的RID≠∞时,实际的反馈系数F=R\(_{I}\)‖RID/R\(_{I}\)‖RID+R\(_{F}\)≠RI/R\(_{I}\)+RF,因此若R\(_{I}\)与RID相近或甚至大于R\(_{ID}\),则实际电路的闭环增益Avf将与R\(_{I}\)+RF/R\(_{I}\)有较大的偏离,只有当BI《R\(_{ID}\)时才能近似认为F=RI/R\(_{I}\)+RF以及A\(_{vf}\)=RI+R\(_{F}\)/RI。

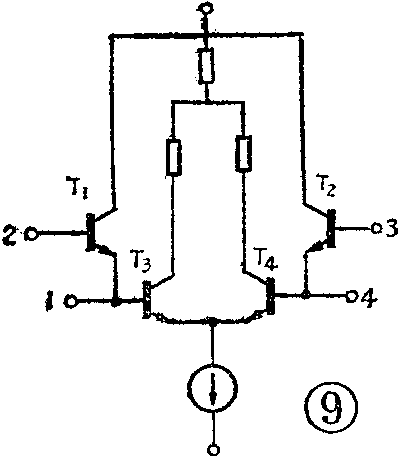

有些运算放大器如8FC2I、7XC2、8FC3、XFC2、FC52等其输入级电路采用复合管输入级或达林顿输入电路,并具有四个输入端,如图9所示即为8FC2I的达林顿输入级电路(指在基本差分放大电路前面再加一级射极跟随器的放大电路)。若从1、4端输入时,晶体管T\(_{1}\)、T2不起作用,仅T\(_{3}\)、T4组成普通差分电路作输入级。这时器件的失调及噪声较小,但R\(_{ID}\)也小,只有20KΩ左右,且IIB也较大;若以2、3为输入,则T\(_{1}\)、T2、T\(_{3}\)和T4构成达林顿输入级,这时由于在差分电路前面附加了一级射随器,因而其输入电阻较高,R\(_{ID}\)可达500KΩ以上,且输入偏置电流也减小了β1倍。但因输入回路串接的PN结较多,故失调及噪声也较大。使用这类器件时可根据对输入电阻的要求灵活选用不同的输入形式。

“开环输出电阻”也是集成运放的一个指标,它通常被定义为:开环运算放大器在室温下其输出电压变化与输出电流变化之比,用符号R\(_{OS}\)表示。它实际上就是开环状态下集成运放输出级的输出电阻,我们总是希望放大器的输出电阻越小越好,以使它具有较好的带负载能力。由于集成运放的输出级几乎都采用射极跟随器电路,因而均具有较低的开环输出电阻。一般器件的ROS约为200Ω。当利用集成运放接成各种线性应用电路时因为都采用较深的电压负反馈,因而电路的闭环输出电阻在电压负反馈的作用下变得非常之小,以致在大多数应用场合均可认为其闭环输出电阻为零。在非线性应用电路中虽然因引入电压正反馈使电路的输出电阻增大,但这时运放的输出只要求能给出高电平或低电平而对输出电压的量值一般不严格要求,因而其输出电阻的大小也不会影响非线性电路的工作,故对其影响一般也不作深入讨论。(张国华)