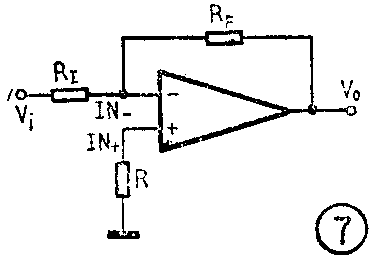

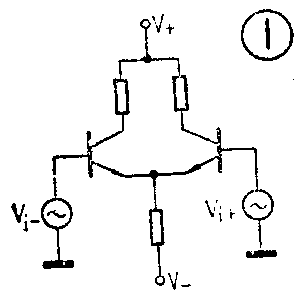

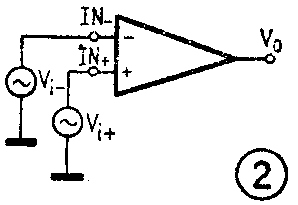

所谓“差模输入电压”一般是指在差分放大电路的两个输入端上所加的两个对地的输入信号之差,即图1所示V\(_{i+}\)-Vi-,有时也称为“差分输入电压”。这类放大器的输出电压V\(_{0}\)仅与其差模输入信号,即Vi+-V\(_{i}\)-成比例,而与这两个信号本身的大小无关。因此,对于输入级均由差分电路组成,因而也具有两个输入端的运算放大器如图2所示,差模输入电压Vi+-V\(_{i}\)-就是它的有效输入信号,其输出电压V0仅与差模信号成比例,比例系数即为集成运放的开环电压增益A\(_{VD}\),即V0=(V\(_{i}\)+-Vi-\(_{VD}\)。而“差模输入电压范围”则被定义为运算放大器两个输入端之间所能承受的最大电压,超过这个允许值,集成运放输入级的某一侧晶体管将出现发射结反向击穿,从而使运放的输入特性显著恶化,甚至可能使它发生永久性损坏。因此VIDR这个指标是用来描述当集成运放两输入端出现过大的差模信号时,不致使输入级晶体管发射结反向击穿的输入信号范围极限指标。

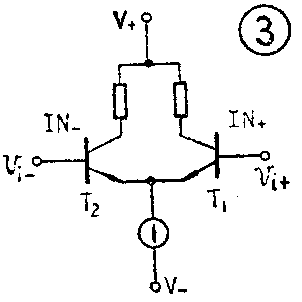

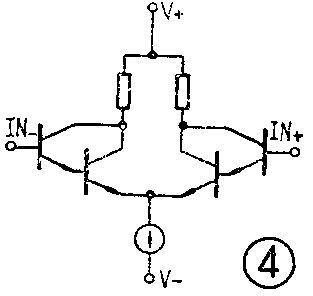

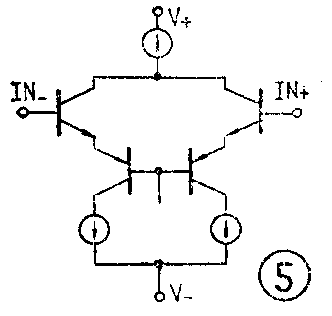

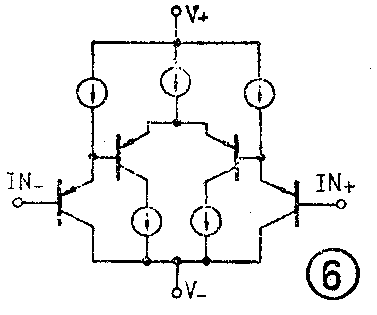

为什么不同型号的集成运放其差模输入电压范围指标V\(_{IDR}\)相差很大呢?这是因为器件VIDR的大小与输入级电路形式有关,对于通用I型运算放大器CF702(即F001、F002),由于输入级采用基本差分电路如图3所示,因此加在两个输入端之间较大的差模输入信号势必使其中一个晶体管的发射结正偏而使另一个反偏。如图3,当V\(_{i}\)+=1V、Vi-=-1V时(这时的差模输入电压V\(_{ID}\)=Vi+-V\(_{i}\)-=2V),晶体管Ti正偏,V\(_{BE1}\)≈0.7V,因而差分晶体管的发射极电位被箝位为VE1=V\(_{E2}\)=0.3V,而晶体管T2则被反偏截止,V\(_{BE2}\)≈-1.3V。若Vi+=2V、V\(_{i-}\)=-2V(这时VID=4V),则此时的V\(_{BE1}\)仍近似等于0.7V,仅比刚才稍有增加,且有VE1=V\(_{E2}\)=1.3V,而VBE2上的反偏电压却增加到约为-3.3V。由此可见,较大的差模输入电压V\(_{ID}\)的绝大部分都加到被反偏的晶体管发射结上。由于采用平面集成工艺做成的硅NPN晶体管其发射结的反向击穿电压BVEBO只有7~9V,超过这个值发射结将被反向击穿。故CF702以及凡是采用基本差分电路作输入级的集成运放如CF709(即F003、F005)、5G23、YZ41、5G26、BG312、8FC5等,其V\(_{IDR}\)指标一般规定为±7V。对于高增益运放BG305,由于输入级采用复合管差分电路如图4所示,因此输入差模信号将使其中同一侧的两个晶体管发射结正偏,而另两个晶体管的发射结反偏。由于反偏电压将由两个晶体管的发射结共同承担,显然这种电路能够承受比CF702更大的差模输入电压,因此BG305以及采用复合管差分电路作输入级的集成运放如SG006、8FC2I、FC3、XFC2、FC52等,其VIDR指标可增大到±14V,即比CF702大一倍。而对于采用包括横向PNP管在内的复合组态输入级的运算放大器,如通用Ⅲ型运放CF741(即F007,其输入级电路见图5)、单电源运放8FC7(其输入级电路见图6),其两输入端之间虽然也是四个两两相对串接的发射结,与上述BG305输入回路的形式相似,但由于其中的横向PNP管具有较高的发射结反向击穿电压,其BV\(_{EBO}\)可达25V以上,因此CF741、8FC7、以及输入级电路形式与之相似的双通用运放CF747(即BG320)、低功耗运放CF253(即F011)、F010等,其输入差模电压范围VIDR可达±30V以上。

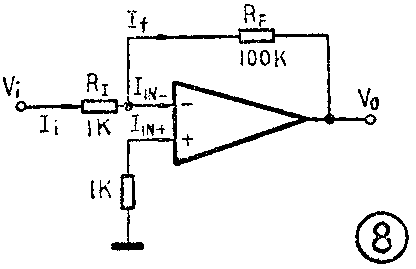

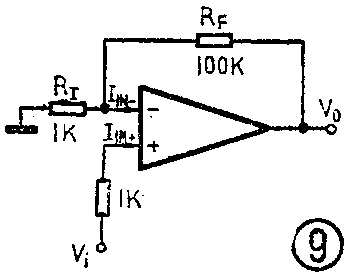

运算放大器电路在什么情况下会出现较大的差模输入电压,这不仅与输入信号的大小有关,而且与电路的工作状态有关。如在图7所示常见的反相输入线性放大电路中,只要放大器工作在线性范围,即集成运放内部晶体管均工作在放大区而未进入饱和、截止状态,则不管输入信号大到几伏甚至十几伏,运放的差模输入电压V\(_{ID}\)=VIN+-V\(_{IN}\)-仍近似为零。这是因为运算放大器在线性工作状态具有极高的开环增益AVD,因而能使V\(_{IN}\)+-VIN-=V\(_{0}\)/AVD趋于零。或者说,只要放大器仍工作在线性段,图7中IN-端就具有“虚地”的性质,这时输入信号电压V\(_{i}\)全降在电阻RI上,即有V\(_{i}\)≈VRI,而不会加到运放的输入端。如今图7电路中的R\(_{I}\)=RF而组成反相器电路,其闭环增益A\(_{Vf}\)=-RF/R\(_{I}\)=-1,当Vi=10V时,反相器输出为V\(_{0}\)=-10V(当采用常规的±15V电源工作时,运放输出电压的线性工作范围在正常负载情况下可达±12V以上),这时的Vi及V\(_{0}\)虽然都不小,但加在运放输入端的差模输入电压仍近似为零。因此,对于线性应用电路,在放大器不出现输出饱和的正常情况下,就不会出现较大的差模输入电压,因而选择器件时可以不必考虑VIDR指标。但是,一旦放大器的输出达到饱和,图7电路中运放的反相端就不再具有虚地的性质,这时就会出现较大的差模输入电压。如图8所示电路,由于R\(_{F}\)=100KΩ而RI=1KΩ,故闭环增益A\(_{Vf}\)=-RFR\(_{I}\)=-100,假定该运放的饱和输出电压值为±12V,因而在|Vi|≤12V/100=0.12V时,放大器工作在线性状态,集成运放的差模输入电压近似为零。但当|V\(_{i}\)|>0.12V后,如Vi=10V,这时因放大器早已饱和,输出电压V\(_{0}\)达到饱和值-12V后不再变化。当仍然认为反相端注入电流IIN-≈0而忽略它时,反相输入端电位V\(_{IN}\)-即可由RI、R\(_{F}\)的分压关系求出。这时因Ii=I\(_{f}\)=Vi-V\(_{0}\)/RI+R\(_{F}\)=10-(-12V)/1KΩ+100KΩ=22V/101KΩ≈0.0218mA,所以有VIN-=V\(_{i}\)-IiR\(_{I}\)=10V-0.218mA·1KΩ=10V-0.218V=9.782V,而同相端因IIN≈0,故V\(_{IN+}\)≈0。这时在图8运算放大器输入端将出现VIN+-V\(_{IN}\)-=0V-9.782V=-9.782V的差模输入电压,可见,对于这个电路若采用VIDR为±7V的器件就不合适了。同样,对于图9所示同相输入放大电路,当V\(_{i}\)较小,运放仍工作在线性范围时,因其输入电流IIN+与I\(_{IN}\)-均近似为零,故有VIN+≈V\(_{i}\)及VIN+≈V\(_{IN}\)-。这时虽然VIN+与V\(_{IN}\)-均不为零,但其差模输入电压VIN+-V\(_{IN-}\)≈0(即在运算放大器输入端存在其大小等于Vi的共模输入电压),当V\(_{i}\)增大使V0达到饱和值±12V后,反相输入端电位就被R\(_{I}\)、RF分压确定为V\(_{IN}\)-=12V·RI/R\(_{I}\)+RF=12V·1KΩ/1KΩ+100KΩ≈0.119V;此后V\(_{i}\)再增大,V0及V\(_{IN}\)-将因放大器已饱和而不再变化,这时在运算放大器输入端就出现了输入差模电压。当Vi继续增大到10V时,有V\(_{IN}\)+≈Vi=10V,故此时差模输入电压V\(_{ID}\)=VIN+-V\(_{IN-}\)=10V-0.119V=9.881V。因此,在设计线性应用电路时,对于闭环增益较高而且输入信号有可能偏大的场合,应该仔细核算可能出现在输入端的差模输入电压最大值并选用合适的器件。(张国华)