在调试、检修脉冲数字电路装置或做有关实验时,一般都需要检查、判断电路中有关端点的电平高低、脉冲有无以及其它一些动态特性等。本文介绍一种仅用一块CMOS集成电路和几个辅助元件组成的多用逻辑电路探针(以下简称多用探针),它能代替万用表和示波器来帮助我们迅速而简便地进行上述测试工作。

这个多用探针能将所测到的高、低电平分别以“1”、“0”的数字形式直接显示出来,它能适应CMOS、PMOS、HTL等各种集成电路组装的逻辑装置,并且能测量单次脉冲和连续脉冲群。它还具有输入阻抗高、显示清晰、体积小、耗电省等优点。

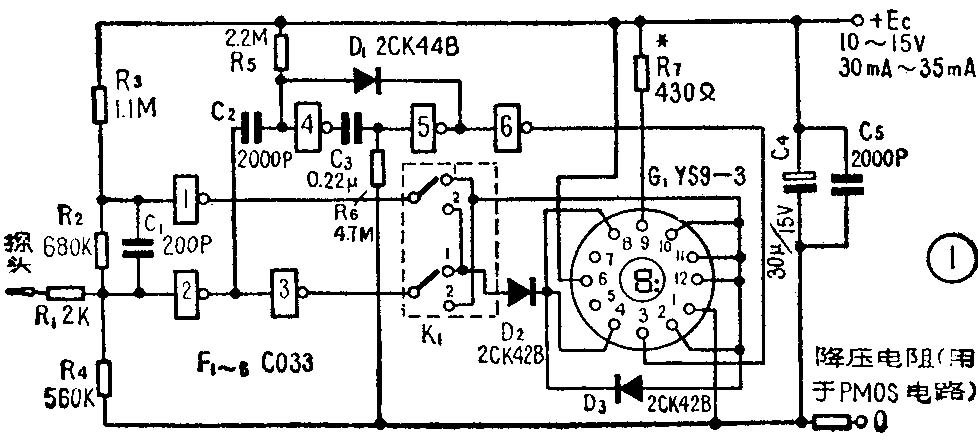

电路原理

多用探针的电路见图1,主要分成两大部分,其中由非门F\(_{1}\)、F2、F\(_{3}\)和数码管G1等组成高、低电平测试显示电路;由非门F\(_{4}\)、F5、F\(_{6}\)和G1等组成单次脉冲和脉冲群等测试显示电路。下面分别介绍这两部分电路的工作原理。

多用探针接通电源后,当探头悬空或被测点为断路时,电源电压E\(_{C}\)通过电阻R2、R\(_{3}\)、R4分压后分别加到F\(_{1}\)和F2的输入端。选取恰当的电阻值,使分压后F\(_{1}\)的输入电平高于它的转移电平Vf1(又称阈值或翻转电平,指门电路翻转时的输入电平);而F\(_{2}\)的输入电平低于它的转移电平Vf2。这样,F\(_{1}\)的输出即为低电平;F2的输出为高电平,F\(_{3}\)将此高电平反相后输出低电平。由于这时与G1有关数字段阳极相连的F\(_{1}\)及F3的输出端均为低电平,G\(_{1}\)阳极对灯丝发出的电子基本上无吸引力,因此G1不显示。

当探头测到高电平时,F\(_{1}\)由于本来输入即为高电平,因此输出维持不变,与其有关的G1数段(“□”形)仍不发亮。但F\(_{2}\)的输入却由低变高,使其翻转,输出变低,F3的输出就变为高电平,通过二极管D\(_{2}\),使G1有关数段(4、8脚)带高电位,从而G\(_{1}\)显出“11”,表明被测点是高电平。相反,当被测点为低电平时,F2、F\(_{3}\)维持探头悬空时的状态不变。F1的输入却由高变低,输出变高,这个高电平直接加到了G\(_{1}\)的2、10、11、12脚,并通过D3加到4、8脚,使G\(_{1}\)相应显示出“□”来,表明测到低电平。如被测点电平不正常,处于高、低电平间,那么G1将无显示。这是因为这种不正常电平既不能使F\(_{2}\)开启,也不能使F1关闭,从而电路也就维持原态不变。

使多用探针动作——即显“1”或显“0”的探头所需输入高或低电平的数值大小,取决于电源电压E\(_{C}\)、F1和F\(_{2}\)的转移电平以及R2、R\(_{3}\)、R4阻值的大小。一般当E\(_{c}\)、Vf1、V\(_{f2}\)已定时,R2、R\(_{3}\)、R4的阻值应满足下列关系:

E\(_{C}\)(R2+R\(_{4}\)R2+R\(_{3}\)+R4)>V\(_{f1}\)

E\(_{C}\)(R4R\(_{2}\)+R3+R\(_{4}\))<Vf2

为了使多用探针的输入阻抗保持在300~400千欧以上,R\(_{2}\)~R4通常应在470千欧到2000千欧间选用。初选好R\(_{2}\)~R4后,就可在调试中适当调整这些电阻的阻值来达到所要求的显“0”或显“1”的探头输入电平值。

图1电路中,F\(_{2}\)的输出端还通过电容C2与F\(_{4}\)~F6等组成的单次脉冲和暂态脉冲群测试显示相连接。这个测试电路其实是一个单稳态电路,它能将单次窄脉冲扩展成持续时间很长的宽脉冲。宽脉冲加到G\(_{1}\)后即显示“一”字形,表示测到了脉冲或脉冲群。单稳电路的工作原理如下:当探头上无输入脉冲时, F2输出端亦无脉冲,此时F\(_{4}\)输入端因R5接E\(_{C}\)为高电平,F4输出为低、F\(_{5}\)输出为高、F6输出为低、G\(_{1}\)无显示,电路处于稳态。当探头测到脉冲时,F2输出的负向脉冲通过C\(_{2}\)使F4的输入由高变低,输出即变高。通过C\(_{3}\)耦合,使F5的输出由高变低,F\(_{6}\)输出为高,G1管中的“一”字段发光,表明测到脉冲。在此同时,F\(_{5}\)输出的低电平通过D1的箝位作用使F\(_{4}\)输入端维持在低电平。这样,暂稳态就开始了。F4输出的高电平通过R\(_{6}\)向C3充电,随着充电的进行,F\(_{5}\)的输入电平按指数规律下降,当降到F5的转移电平时,F\(_{5}\)翻转,输出恢复到高电平,暂稳态结束,G1显示熄灭。电路的暂稳时间t,也即F\(_{6}\)输出的单个脉冲的宽度,一般可按下式估算:t=(0.5~0.8)R6C\(_{3}\),式中t的单位为秒,R6单位为兆欧,C\(_{3}\)单位为微法。图1电路的t设计为0.7秒左右,也即G1对单次窄脉冲的显示时间为0.7秒左右。由于CMOS门电路的转移电平每块都有些差异,因此在调试时可根据所需要的暂稳时间适当调整R\(_{6}\)和C3。

装制与调试

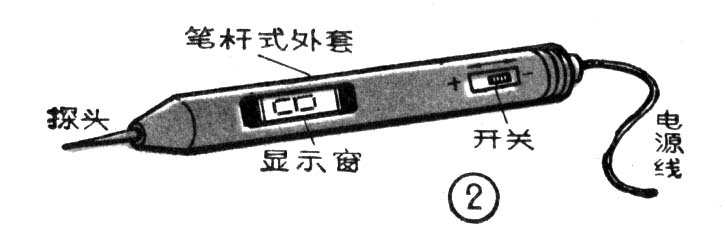

由于所用元件较少,全部零件可装入一个直径20~25毫米、长100~150毫米的笔杆式外壳中,外形如图2。电路中电阻可选用RJ型1/4W金属膜的,电容可用QI3型玻璃釉的,二极管采用2CK“芝麻”型。图1是为测试CMOS电路而设计的,因此电源电压为10~15伏,G\(_{1}\)用YS9-3型数码管已有足够的显示亮度。如能用额定阳栅工作电压更低的数码管(如YS9—1H型等)则显示将更清晰明亮。PMOS电路的工作电压常为20~24伏,因此使用时要在EC电源线上串进一个降压电阻后方能接到被测装置的供电电源中去,串降压电阻后C\(_{4}\)两端的电压应保持在12~15伏。在测试TTL电路组装的设备时,由于TTL电路的工作电压仅为5伏,因此G1的显示较暗。若在电路中加一个双位双刀拨动开关(图中虚线框内K\(_{1}\))就成了正逻辑和负逻辑电路的通用探针,K1置于“1”时(图2笔套上“+”位置)用于测CMOS、HTL、TTL和正逻辑PMOS电路,K\(_{1}\)置于“2”时(图2笔套上“-”位置)用于测负逻辑PMOS电路。

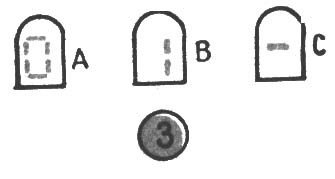

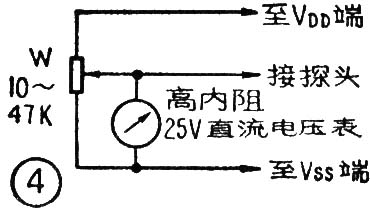

电路全部组装完毕、检查无误后,就可进行调试。接上电源,测量G\(_{1}\)灯丝电压应为1.1伏,如不对,应改变R7的阻值。然后在探头悬空的情况下看G\(_{1}\)是否有显示。加显“□”(如图3A),可适当减小R3(或增大R\(_{4}\));如显“:”(如图3B),可适当减小R4(或增大R\(_{3}\)),直至无任何显示为止。下一步就是将探头接到图4所示的测试电路中去,调节W,从电压表上分别读出显“1”和显“0”时的输入电平值,看是否和预期的一致。图1电路显“0”输入低电平值为1伏以下,显“1”输入高电平为7~8伏以上。F1、F\(_{2}\)的转移电平为(0.6~0.65)EC左右。如显“1”电平不符,可调换合适的F\(_{l}\)~F3。如显“0”电平不对,则可调整R\(_{2}\)的阻值来纠正。调好显“1”和显“0”电平后要再将探头悬空,看G1是否有显示。如有显示,就应再相应微调R\(_{3}\)、R4来消除。

经过以上调试后,多用探针就能使用了。测试高、低电平时的情况以上已介绍了。测试单个脉冲时,G\(_{1}\)应显示出如图3C所示的字样,并维持0.7秒左右的时间。当探头测到频率较低的脉冲或脉冲群时,G1除了显示出图3C那样的字样外,还会交替出现1和0的字样,根据1、0字样各自的持续显示时间的长短,就可大致看出所测脉冲的占空比。(王德源)