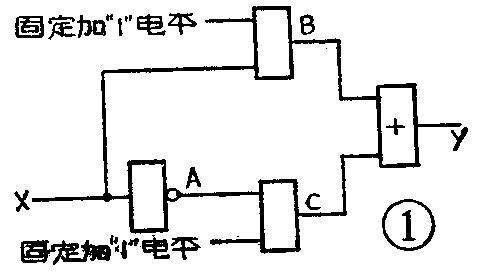

在电路图1中,X为输入端,Y为输出端,根据我们已学过的逻辑电路知识不难看出,当X为逻辑0(低电平信号)时,则A=1(高电平信号),C=1,B=0,Y=1;当X为逻辑1时,则A=0,C=0,B=1,Y=l。这就是说,无论输入端X是逻辑0还是逻辑1,输出端Y总为逻辑1。

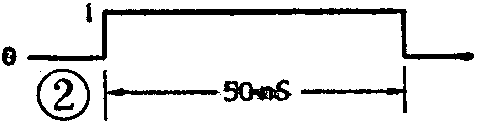

讨论上述逻辑关系的时候,我们没有考虑门电路的延迟时间(即信号通过逻辑门电路所需要的时间),实际上任何一个门电路都有一定的延迟时间。假如图1电路中的与门、或门、非门的延迟时间都是5毫微秒(ns),那么当把图2所示的脉冲信号(该信号有两个电平:1和0)加到图1电路的输入端X时,电路的输出端Y是否还总是1电平?

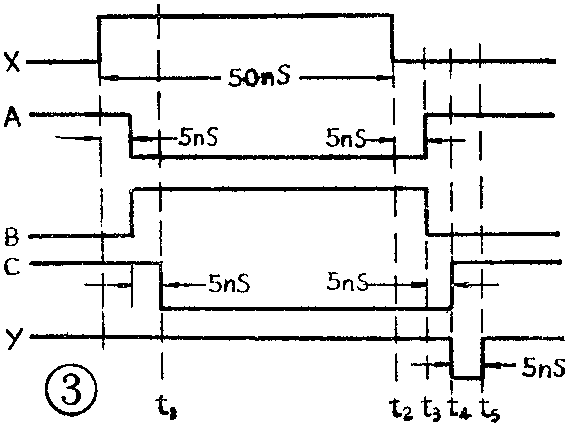

为了弄清这个问题,我们将图1电路中各点(X、A、B、C、Y)的波形图画出来,见图3。图1中B点和X点的波形是同相的,只是在时间上B点比X点延迟5毫微秒;A点则和X点的波形相反且延迟5毫微秒;C点与A点的波形相同,也延迟5毫微秒;最后,输出端Y点的波形则应为B点和C点波形相加,并且再延迟5毫微秒。

下面我们分析在时间t\(_{1}\)、t2……时,Y点波形的变化情况。在t\(_{1}\)以前,由C=1维持Y=1;在t1的时候,虽然C由1→0,但由于B在5毫微秒以前已由0→1,所以能由B=1继续维持Y=1;在t2时,虽然X由1→0,但是B点要在5毫微秒以后才由1→0,所以在t\(_{2}\)~t3期间,仍由B=1维持Y=1,在t\(_{3}\)~t4期间,B=0,C=0,按逻辑关系说Y=0才对,但由于Y本身的延迟,B=0以后5毫微秒,才能使Y=0,所以此时Y仍为1;到达时间t\(_{4}\)后,由于B由1→0已经过5毫微秒,所以原来由B维持Y=1的条件消失,而这时C刚由0→1,因此C还不能立即使Y=1,因此就出现了Y=0的情况;t5以后,便由C=1维持Y=1了。由此可见,由于门电路延迟时间的影响,输出端Y出现了一个短暂的不应该有的0电平,也就是出现了一个负脉冲,而不总是为1电平。

这个小例子告诉我们,有些逻辑电路在考虑逻辑门电路的延迟时间后, 有可能产生短暂的逻辑上的错误。若把图1电路的输出端Y接在某些电路或仪器上,可能不会有什么影响。如接在直流电压表上,这个逻辑上的错误并不会影响表的读数。但是,如果输出端是接到某触发器上,则可能引起误触发,造成整个电路逻辑上的错误。有些数字电路的逻辑功能并没有问题,但工作总是不正常,往往就是由于这种原因造成的。(木易)