主要特性曲线

同晶体管一样,集成电路也有它的特性曲线,熟悉这些特性曲线可以灵活运用集成电路。TTL与非门集成电路的主要特性曲线有:

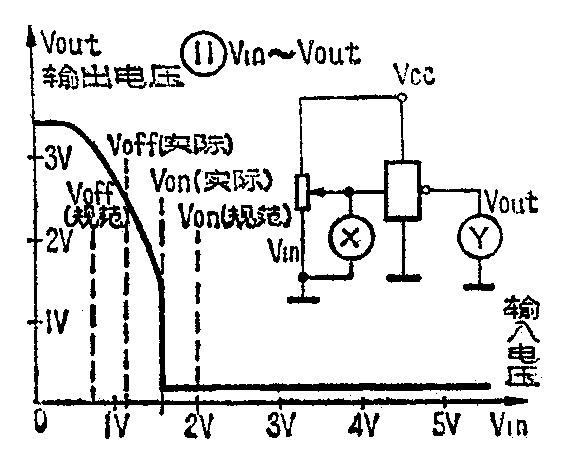

1.图11是转换特性曲线(V\(_{in}\)~Vout),也叫电压传输特性曲线。从这曲线上可以看到输出电压是如何随输入电压的变化而变化的。

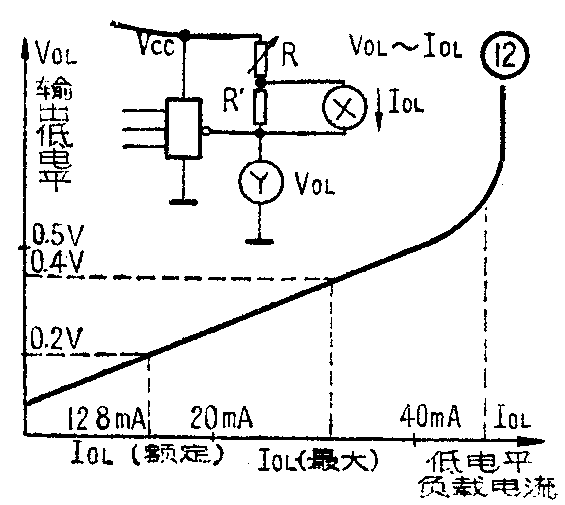

2.图12是低电平负载特性曲线(I\(_{OL}\)~VOL),表明负载电流对门电路输出低电平的影响,当负载电流I\(_{OL}\)上升到一定程度后,曲线急剧上升,低电平就将超出规定,破坏了逻辑关系。

从图中看出,随着I\(_{OL}\)的增大,VOL基本上直线上升,这直线的斜率即为与非门电路在此种状态下的输出阻抗,一般为10~20欧。

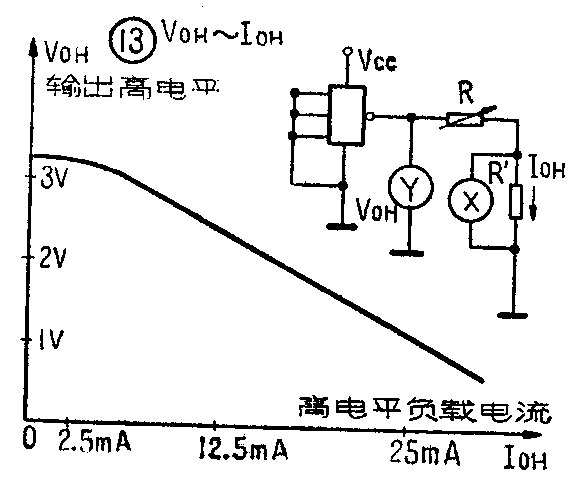

3.图13是高电平负载特性曲线(I\(_{OH}\)~VOH)。在I\(_{OH}\)=0时,VOH有一较高的值(室温下3.9~4伏),稍稍流出电流即下降到3.6伏左右,随后有一小段较为平坦,如果I\(_{OH}\)继续增大,VOH开始直线下降,其斜率(不计正负号)即为此时的输出阻抗,一般在100欧左右。这曲线表明:TTL与非门输出为高电平时,可以给出的驱动电流比低电平时的吸入电流小得多,一般以不超过1~2毫安为宜。

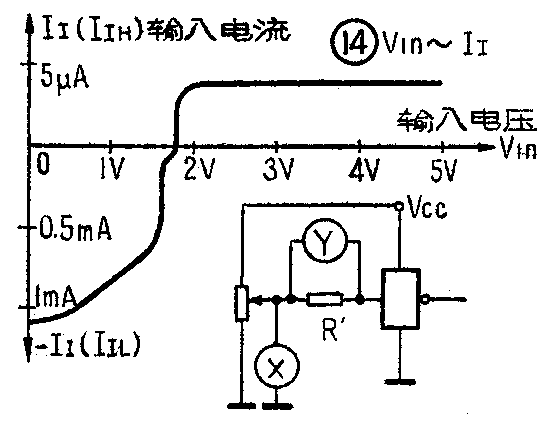

4.图14是输入电压—电流特性曲线(V\(_{in}\)~II)。输入电压为0伏时(此时其余非被测输入端接高电平),测得的I\(_{I}\)是从电路往外流的电流,其值即为IIL。随着V\(_{in}\)的提高,IIL直线减小,这段直线的斜率的倒数就是输入端为低电平时的输入阻抗,其值基本上等于线路图(图1)中的R\(_{1}\)。当继续提高Vin到1.5伏附近,I\(_{I}\)迅速变成0,这是曲线的转换区。继续提高Vin(此时其余非被测输入端接地)则电流微微向正的方向增加,这时I\(_{I}\)变成IIH,I\(_{IH}\)数值很小,在微安量级,当Vin大于2伏时,几乎成一平行于X轴(V\(_{in}\))的直线。它的斜率的倒数很大,对应着这时的输入阻抗很大(几百千欧),是为输入端为高电平时的输入阻抗。

单与非门的最简单应用

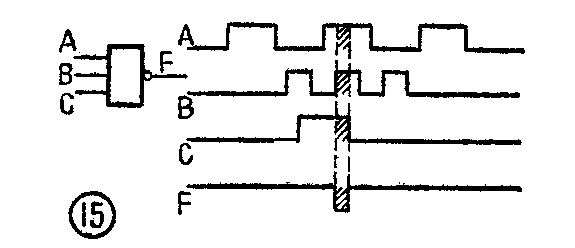

1.译码。在自动控制系统中,常要求必须同时满足几个条件后,一个动作才能执行、一个继电器才能吸合或一个报警装置才能工作等等。假设必须同时满足三个条件才能执行,那么这样的一种关系可以用一个三输入端的“与非门”来完成。图15是它的波形图。

图中A、B、C是三个输入信号(三个条件),这三个信号只有在同时是高电平(如波形图15中阴影部分所示)时,输出端F才是低电平,这个输出信号经过处理后可用来推动继电器等执行机构。这种功能称为“译码”。

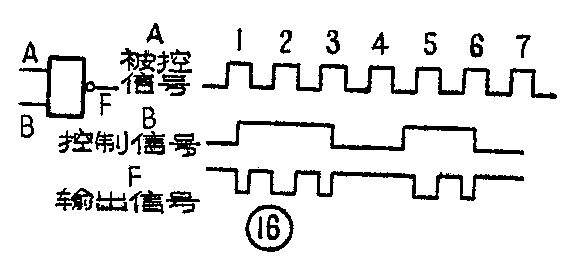

2.门控。设有一信号,希望受另一信号的控制,若控制信号为高电平时,允许被控信号通过,反之则不允许通过。这样的一种功能,可用二输入端的单与非门来实现,如图16所示。

从图16可看到,在控制信号为高电平区间,脉冲1、2、3、5、6都可通过,不过脉冲2、5是完整通过的,而脉冲1、3、6只通过一部分,脉冲4则完全不能通过。如果我们希望通过的脉冲都是完整的,则还需要采取一些其它措施,这类问题将另外讨论。

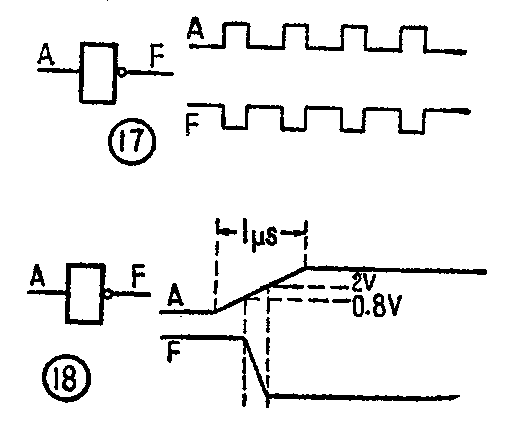

3.倒相。若只使用一个输入端,则输出信号就等于输入信号的倒相(图17)。与非门在这种特殊的情况下就成了“非”门。倒相应用也是常见的,如上述“译码”和“门控”两种应用中,输出信号都成了负信号,若需正信号时,则再加一级倒相即可。信号经两级倒相仍为原信号(这里假设工作频率较低,不考虑延迟)。

4.整形。若输入信号是边沿很差的信号,经与非门之后,边沿变好。例如图18中输入信号上升时间t\(_{r}\)=1微秒,由于在输入从0.8伏至2.0伏之间,输出即完成从高电平到低电平的转换,因此输出边沿≈tr·

与非门的级联

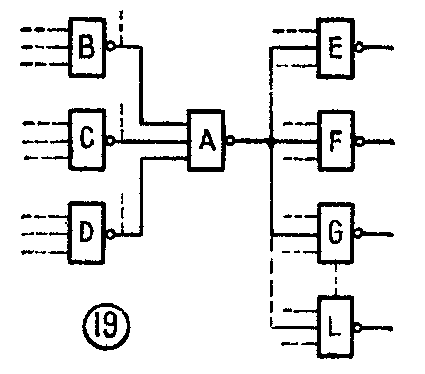

从以上所讲的可以看到,单个与非门的应用面是有限的。但是由多个单门构成级联,加上适当的反馈,可以组成纷繁复杂的逻辑关系,完成各种逻辑功能。下面先讲一讲级联的一般问题。

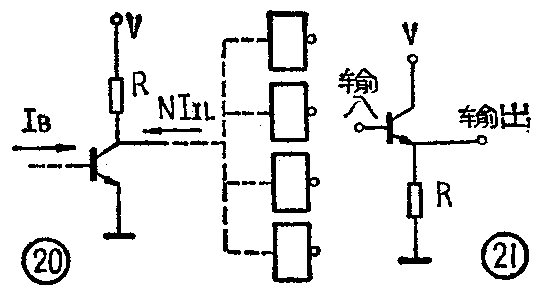

TTL与非门的输出高电平为3~4伏,低电平小于0.4伏,而它对输入高、低电平的要求也是如此。因此,一个单门的输出可以直接接到另一门的输入端。典型的单门级联如图19。与非门A的三个输入端分别与门B、C、D的输出相连接,当这三个输出中任一为低电平时,假设B为低电平,则从A中就有一股电流I\(_{IL}\)流入B。若三个输出都为低电平,在理想情况下(VOL都相等),每个门各从A中取得三分之一的I\(_{IL}\)。在上述两种情况下A输出均为高电平,由于带有N个负载,每个负载有高态输入电流IIH,所以从A的输出端流出的电流为NI\(_{IH}\)。从特性曲线可看出,NIIH越大,门A的V\(_{OH}\)降落越多,所以指标要求IIH越小越好。

当门B、C、D输出都为高电平时,门A输出为低电平。门E、F……L中各有一股电流I\(_{IL}\)流入门A。在最坏情况下,即E、F……L的其他输入端都为高电平时,IIL为最大,门A所受的总电流为NI\(_{IL}\)。因此对于一个确定的门电路,负载数N应严格保持小于规定值。如果要求带负载较多,可选用“与非功率门”,它的负载数可达到30个。

输入输出接口

第一级门电路的输入信号可能是机械的、光的或其它形式的信号,这些信号都需要先转换成电信号,并通过输入接口,使信号电平与TTL电路的输入电平相匹配。逻辑电路最后一级的输出也要通过输出接口,以推动需大电流或高电压才能动作的执行机构。

输入接口的低电平必须小于0.4伏,而且必须是低输出阻抗的。较好的形式是NPN晶体管的集电极输出,如图20所示。

一般不常使用射极输出器作输入接口。用射极输出器似可降低输出阻抗,其实还应该考虑以下的问题:因为此线路(如图21所示)在高电平时输出阻抗为R/(1+β),但在低电平时,晶体管截止,输出阻抗仍为R。而对TTL与非门电路而言,要求的却是在低电平时前级的输出阻抗要小。部标规定I\(_{IL}\)最大为1.6mA,如VOL为0.4V,则R≤0.41.6≈250Ω,即能可靠的带动一个门电路。若R取250Ω,则在高电平时R上的压降为3.5V,流过R的电流为:I\(_{R}\)≈3.5V-0.7V;250Ω≈11mA,显然不经济(但并非不可使用)。有时也用射极输出器作输入接口,因为它的输入阻抗很高,对被转换的信号,如高内阻的光信号等,影响很小。

输入接口的高电平应在3.5伏至5伏之间,不允许用高于5伏的电压,因为这样可能导致门电路输入端的击穿。如果电压较高,可用分压法降低,但应注意不能因分压而提高低电平时的输出阻抗。

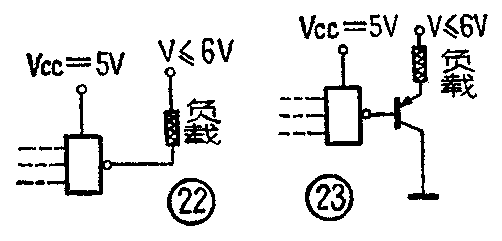

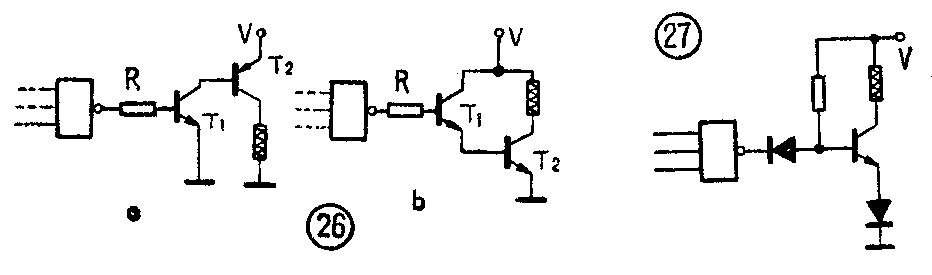

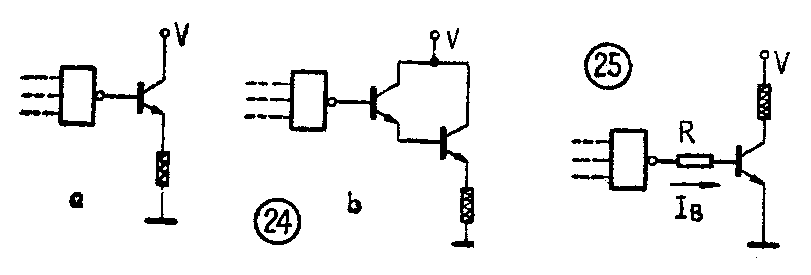

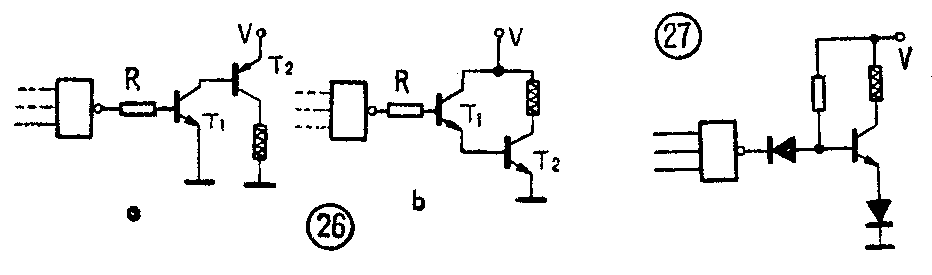

TTL集成电路的输出接口可以用两种方法驱动。(1)当TTL电路输出为低电平时,允许流入NI\(_{IL}\)的电流,可以直接驱动微型继电器等(如图22),但继电器电流不能超过IOL(部标为12.8mA)。在电流较大的情况下,可以加射极输出器,如图23所示,这时驱动电流可增加β倍。若还不够,可用两管连接成复合管式。此外,无论是图22还是图23,均应注意继电器的电源电压不能过高,以免与非门中的T\(_{4}\)管(见图1)被击穿,一般不超过6伏。(2)在高电平驱动时,由于输出阻抗较大,稍有驱动电流,高电平即降落,所以一般都需加射极输出器,如图24,但此时负载上电压减小。在需要较高电压的场合,则必须用晶体管作反相器如图25,这时,在门的输出端加限流电阻R,使驱动电流达到所需要求。如果需要更大电流,可以用图26和图27所示方法。

总之,接口的形式可以是多样的。注意TTL集成电路在不同情况下的输入输出阻抗,再应用晶体管电路的知识,便可以灵活运用。(上海半导体器件十六厂 徐治邦)