TTL集成电路的全名是“晶体管—晶体管逻辑集成电路”。这是因为电路的所有电子器件全部由晶体三极管构成,并集成在一块半导体硅片上。在稳定情况下输入和输出只有两种方式,即高电平或低电平;输入与输出的关系不是数量上的倍数关系,而是一种逻辑关系。它可以构成各种数字运算电路以进行逻辑运算,因此,它不但是电子计算机的重要元件,且广泛应用于各种程序控制、数控装置或数字式仪器仪表中。

TTL集成电路除作逻辑数字运算外,还可组成例如多谐振荡器、单稳态触发器、双稳态触发器等脉冲电路,所用的元件数远少于用分立元件搭成的同类电路。本文准备先从单与非门讲起,就TTL集成电路的基本原理及应用作些介绍。

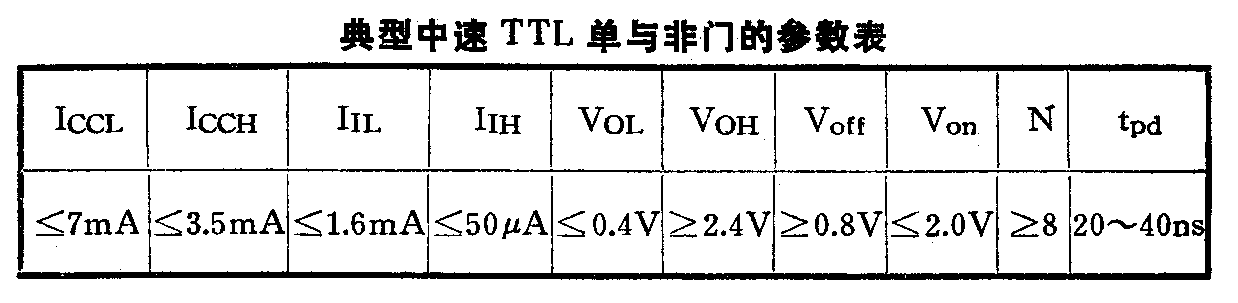

典型TTL单与非门的工作原理

图1是一个典型TTL单与非门的线路图,它是由五个晶体管和五个电阻构成。T\(_{1}\)是一个多发射极晶体管,其中任一发射极与T1的基极、集电极一起都可构成一个晶体管,任何二个发射极之间,由设计及工艺保证它们基本上保持独立。T\(_{1}\)管的发射极是电路的输入端,图1中只画了三个,实际上目前有的产品可以多到八个。

在任一输入端加一电压Vin=0伏,则从电源V\(_{cc}\)(一般是5伏)通过R1、T\(_{1}\)的be结至输入端有电流流通,即T1管的基极有电流“注入”,T\(_{1}\)饱和很深。T1的bc结也处于正向偏置状态,所以V\(_{B}\)(图1上B点电位)比Vin只高0.1伏左右,T2无法导通。因而V\(_{C}\)≈5伏,VD≈0伏,T\(_{5}\)亦不可能导通。但因VC≈5伏,所以T\(_{3}\)管是导通的。T4的基极电压较高,V\(_{E}\)≈5伏-0.7伏=4.3伏,因T5不通导,T\(_{4}\)发射极没有通路,所以T4不通导。但若在输出端接一个电压表,或加一高电平负载,则T\(_{4}\)微微通导,在T4的be结上有一个压降(约为0.5~0.7伏),所以可量得输出电压为3.7伏左右。在全部输入端都为0伏时,上面的分析与结果不变。

如果使Vin=0.4伏,则V\(_{B}\)≈0.5伏。这时T2仍不导通,T\(_{3}\)、T4、T\(_{5}\)的状态亦保持不变。再进一步提高Vin到0.9伏,VB≈1伏,T\(_{2}\)已经导通,VD≈0.3伏,此电压还不足以使T\(_{5}\)通导。T2导通时,V\(_{C}\)开始降落,通常设计使R2/R\(_{3}\)≈2,这样VC降落的速度为V\(_{D}\)上升速度的2倍。当输入电压为1.3伏时,T2、T\(_{5}\)都导通,但T2尚未饱和,V\(_{C}\)约为3.6伏。这时,从Vcc通过R\(_{2}\)、T3的be结、T\(_{4}\)的be结、T5的ce到地构成通路,T\(_{3}\)、T4、T\(_{5}\)全部导通,形成一个很大的“瞬态”电流。随着输入电压的进一步提高,T2迅速饱和,V\(_{C}\)降到1伏左右,此时T3虽仍通导,但电流较小,而T\(_{4}\)已不能通导。输出管T5已处于深饱和状态,输出电压V\(_{out}\)≈0.1伏。这时候的输入电压约为1.8伏,若进一步提高输入电压,例如提高到3.7伏,输出状态保持不变。

这里,归纳一下TTL与非门的特性:当任一输入为低电平时,输出为高电平;只有当所有输入都为高电平时,输出才为低电平。这两个输出状态是稳定的,输入电压稍有波动,不会引起输出电压的变化。我们将小于0.4伏的电平称为低电平(也称“0”电平),而将大于2.4伏的电平称为高电平(也称“1”电平)。输入电压0.8伏和2.0伏称为“门槛电平”,这个区间对应于电路的过渡区。

当所有输入都为高电平时,电路输出才为低电平,“全高”变“低”,这是“与非”关系,这个电路即被称为与非门电路,它的逻辑表达式为F=A·B·C……-。

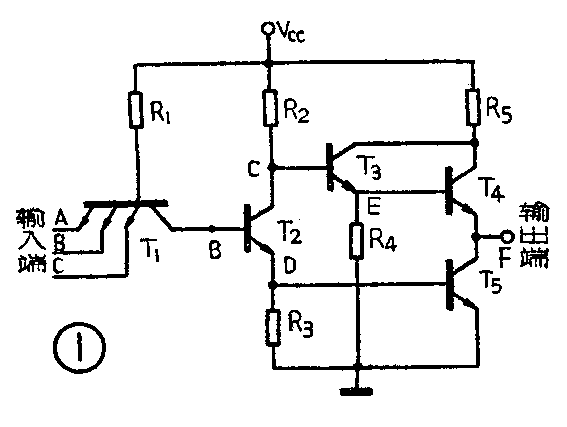

单与非门的逻辑图

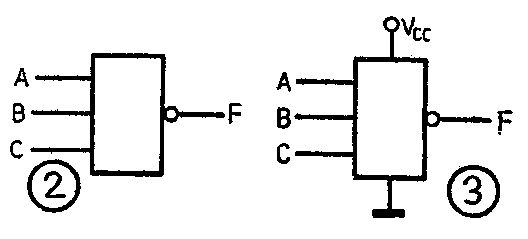

从逻辑功能来看,图1的线路可以用逻辑符号(图2)来表示。这里,A、B、C表示三个输入端,方框表示它们是“与”关系,小圆圈表示“非”关系,从小圆圈上引出的线表示输出端。整个图表示:这是一块有三个输入端的单与非门。用逻辑图来代替线路图,可使表达形式简捷、逻辑关系突出,对于整机设计、装配、调试都是很方便的。当然,每一个单门必须有电源和地线,但在逻辑图上规定不标出,只是在某些特定情况下,如参数测试中,才将逻辑图画成图3的形式。

典型TTL单与非门的主要参数

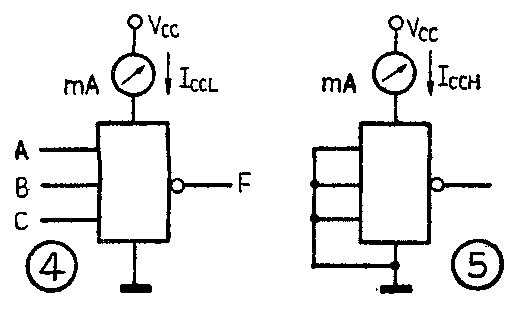

1.通导电流I\(_{CCL}\):指与非门电路输入端全部开路,输出空载处于低电平时,由电源供给的总电流,测试方法如图4所示。

2.截止电流I\(_{CCH}\):指与非门电路输入端短路接地时,输出空载处于高电平时,由电源供给的总电流,测试方法如图5所示。

I\(_{CCL}\)和ICCH实际反映一个单门消耗电流的大小,即功率消耗的大小。

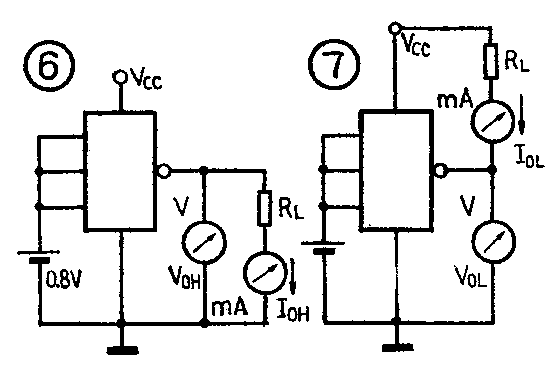

3.输出高电平V\(_{OH}\):输入任一端接低电平时,输出的电压值。该参数必须在额定输出负载电流下进行测试,如图6。

4.输出低电平V\(_{OL}\):输入端全部接高电平时,输出的电压值。实际测量时规定要带一定的负载电流,如图7所示。

5.关门电平V\(_{off}\):输入电压从0伏上升到一定程度,输出开始下降,规定输出下降到一定程度(此时仍能保证电路处于高态输出)时的输入电压为“关门电平Voff”,输入电压小于V\(_{off}\)时,“门”保证是“关”着的。

6.开门电平V\(_{on}\):当输入电压上升到某一数值Von时,输出保证为低电平,V\(_{on}\)就称为这个电路的“开门电平”。

实际测量时,V\(_{off}\)和Von不是单独测量,而是和V\(_{OH}\)、VOL一起测量的。在固定输入电压为0.8伏(即V\(_{off}\))测输出电压为VOH说明关门电平合格。在固定输入电压为2.0伏(即V\(_{on}\))测输出电压为VOL则说明开门电平合格。

7.同V\(_{OL}\)一起测的还有低电平负载能力N,也称扇出系数,就是在规定的低电平输出时,一个门电路输出端能够带动同类型电路的个数。在测量时则是规定带N个负载,反过来看低电平是否合格。

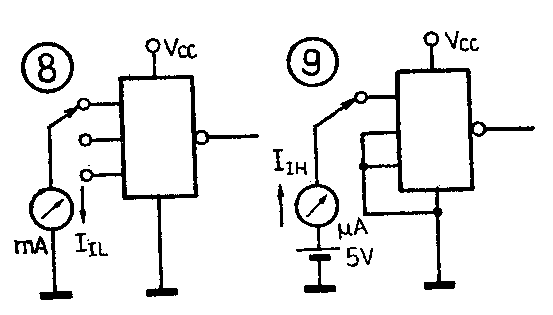

8.输入短路电流I\(_{IL}\):当与非门某一输入端接地时,从VCC经R\(_{1}\)、T1的be结至地的电流。图8。

9.输入交叉漏电流I\(_{IH}\):与非门任一输入端接高电平(例如5伏)而其余输入端接地时,流入输入端的电流,测试方法如图9。

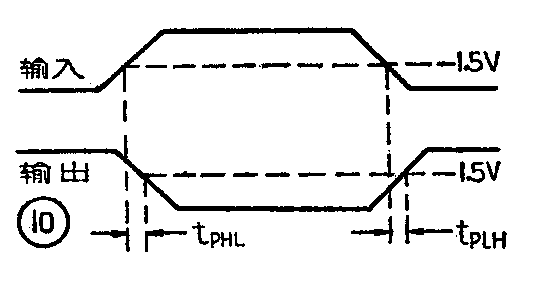

10.传输延迟t\(_{PLH}\),tPHL,t\(_{pd}\):在与非门的输入端加一信号,则它的输出是一个倒相的信号,但在时间上略有延迟,如图10所示。输出波形下降边的1.5伏处和输入波形上升边的1.5伏处的时间差称为tPHL,意思是:“从高态(H)到低态(L)的传输延迟”。类似地,t\(_{PLH}\)为“从低态到高态的传输延迟”。这两个数值一般是不一样的,所以“平均传输延迟”tpd=\(\frac{1}{2}\)(t\(_{PLH}\)+tPHL)。(上海半导体器件十六厂 徐治邦)