联合设计31厘米电视机,是一种普及型产品,也是今后我国重点发展的家用晶体管黑白电视机。为帮助大家了解它的基本原理,我们将陆续发表一些有关电路分析的文章。现在先介绍高频头电路。

高频头电路的主要作用是对天线上感应的各种微弱的全电视信号加以选择,并将选择出来的全电视信号加以放大,然后,与本机振荡信号一块注入混频器进行变频,产生特定的中频信号。因为高频头电路在电视机中构成一个独立整件,所以,又叫做高频头。

高频头的种类很多。按器件划分,有电子管高频头和晶体管高频头两类。由于电子管的输入、输出阻抗都很高,所以,电子管高频头的电压增益可以做得很高,承受强信号的能力和抗交扰调制的能力都比较好,而且性能稳定,一致性好。但是,电子管高频头的体积大,供电系统较复杂,耗电也多。晶体管高频头的优点是体积小、耗电少。但晶体管的输入、输出阻抗很低,动态范围小,所以承受大信号的能力和抗交扰调制的能力都差。另外,晶体管的参数一致性和稳定性也不如电子管。但只要合理选择电路,认真进行设计,完全能够得到良好的效果。按调谐方式来分,高频头又可分为机械调谐式和电子调谐式两种。机械调谐高频头又有三种主要形式:(1)转鼓(滚筒)式——特点是各频道的线圈位于同一转鼓上,彼此是独立的,因此,各频道的幅频特性互不影响,只是结构较为复杂。根据我国目前生产条件,联合设计采用了这种结构形式。(2)转换开关式——它类似于波段开关,各频道线圈互相串联,所以,幅频特性相互牵引。但结构较转鼓式简单。(3)转盘式——它吸取了转鼓式与开关式的优点,各频道线圈位于同一转盘上,但接触点是固定的,即用转动的圆片代替了转鼓,使结构简单、体积缩小,因此得到了广泛的应用。电子调谐式高频头,由于没有机械触点,所以可靠性高,也便于实现集成化,越来越得到广泛的应用。按微调方式来分,又可分为独立微调式和公用微调式。独立微调式,各频道均没有本振微调线圈,通过同一传动机构进行微调。可预先将各频道的本振频率调好,变更频道时无需再调整;而公用微调式是各频道公用一个本振线圈,变更频道时,本振频率也要改变,就必须重新调整本振频率。因此,联合设计采用了独立微调式。

目前国内外用得较多的高频头电路是由高放、混频、本振等组成的超外差式电路。超外差电路灵敏度高,抗干扰性能好,工作稳定。此外,还有高放、自激混频式电路和直接混频式电路,因稳定性差、信杂比低劣,在产品电视机中很少采用。但业余爱好者可根据自己的条件,试一试。

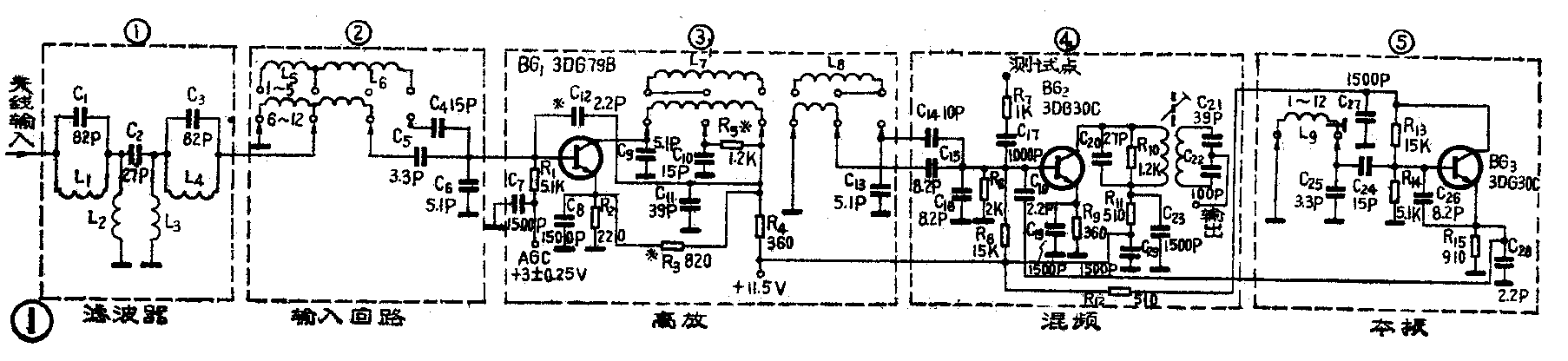

联合设计31厘米电视机的高频头电路如图1所示。它由滤波器、输入回路、高频放大、混频和本振五部分组成。现分别分析如下:

1.滤波电路:

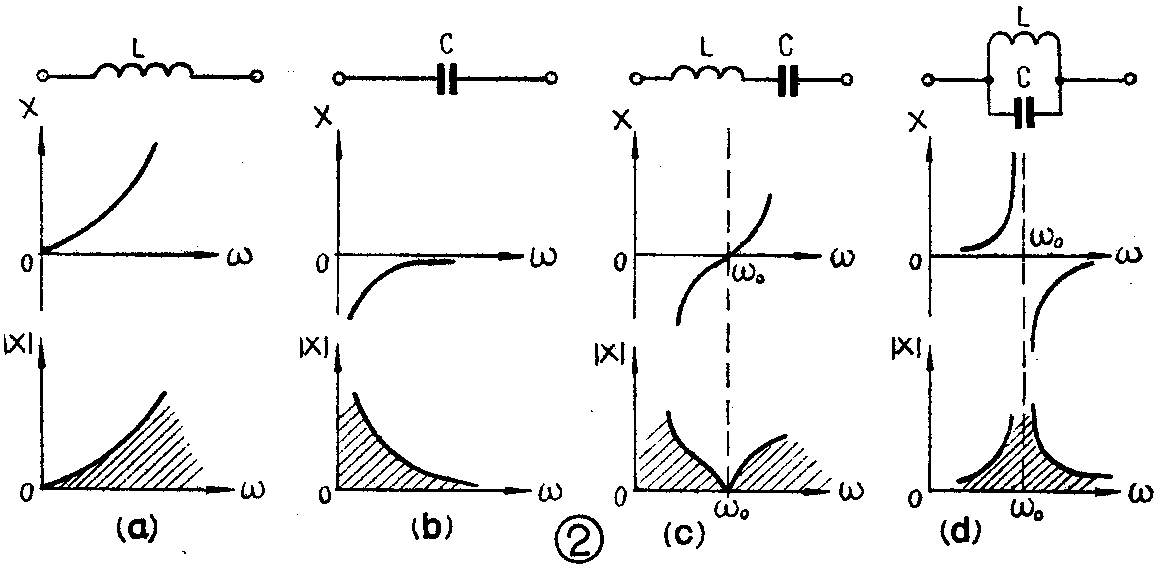

在天线馈线和输入回路之间,接入一组滤波器,目的是为了抑制中频以下的干扰信号和高频道的镜象干扰信号。常用的滤波器由电感、电容组成。图2是电抗元件的阻抗特性。由于感抗(jωL)是随频率的增加而增加的,所以,当把电感串联于电路时,有低通特性见图2(a)。由于电容器的容抗(1/jωc)是随频率的增加而减小的,所以,串联于回路时,有高通特性,见图2(b)。对于L、C串联谐振回路来说,其谐振阻抗为零(理论值),所以,串联于回路中有带通特性,见图2(c)。对于L、C并联谐振回路,其谐振阻抗为无穷大(理论值),所以串联于回路中有带阻特性,见图2(d)。由于电抗元件有这些频率特性,所以将电感和电容进行适当的组合,就可以获得各种类型的滤波器。

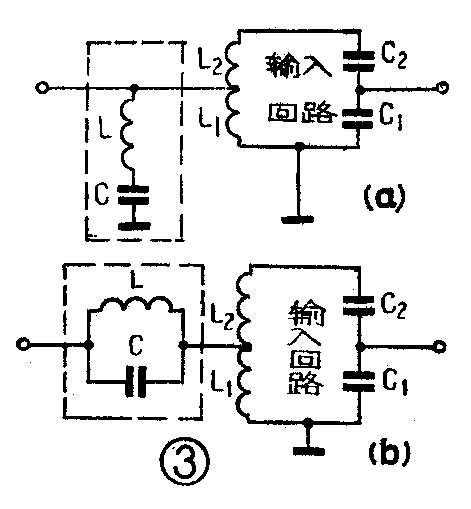

(1)简单型滤波器,如图3所示。图3(a)为L、C串联谐振电路,将它并联于输入回路中,由于其串联谐振频率为中频频率(若伴音中频为30.5MHz,图象中频为37MHz,则应谐振在34.25MHz上),所以,此滤波器对34.25MHz阻抗很小,相当于短路,使中频干扰信号不能进入输入回路。图3(b)将L、C并联谐振电路串联在输入回路,因为并联谐振频率为中频频率,所以,对中频干扰阻抗很大,因此中频干扰信号不能进入输入回路。上述两种滤波器,优点是结构简单,但是阻带较窄,只能滤掉单一的中频干扰,对于30.25~38.25MHz范围内的其他中频干扰信号,就不能抑制了。

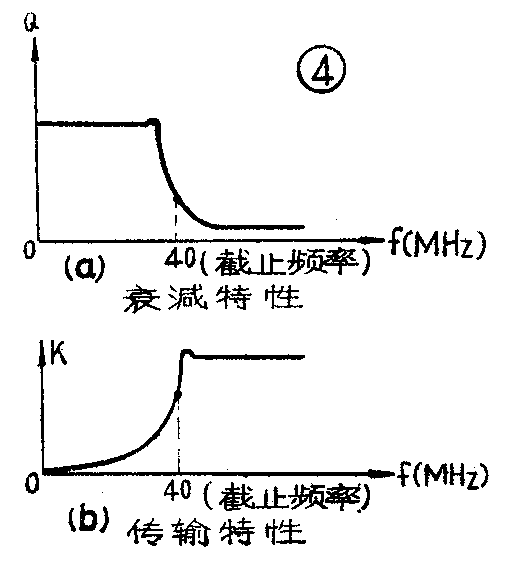

(2)复合高通滤波器,如图1第①虚线框内所示。它由两节简单带阻滤波器和一节高通滤波器组成。L\(_{1}\)C1、L\(_{4}\)C3分别组成带阻滤波器,作用是阻止中频干扰进入输入回路;L\(_{2}\)、C2、L\(_{3}\)是简单π型高通滤波器,L2、L\(_{3}\)可使40MHz以下的干扰信号旁路到地,C2为信号进入输入回路提供通路。这种滤波器的衰减特性和信号传输特性如图4(a)、(b)所示。其优点是有一定的阻带带宽,在阻带中,衰减量可做得较高;而对通带内的行波系数影响较小。联合设计高频头的滤波器就采用了这种电路。

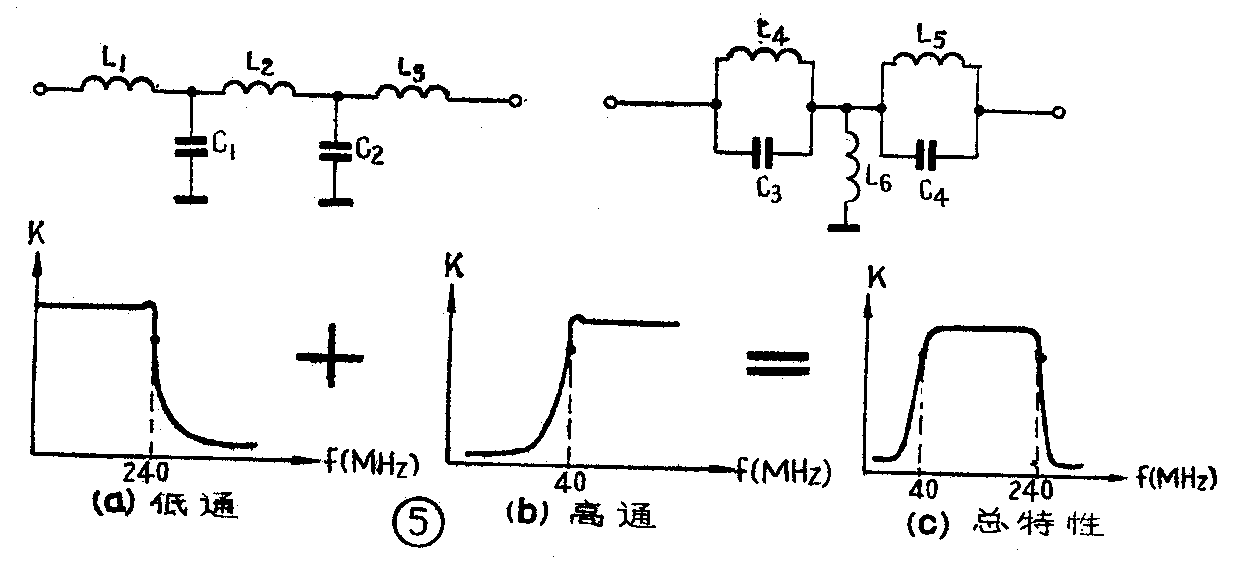

(3)高、低通复合滤波器,如图5所示。图(a)是低通滤波器,其作用是将240MHz以上的干扰信号滤掉;图(b)是高速滤波器,其作用是将40MHz以下的中频干扰滤掉。图(a)与图(b)相连接,就组成一个频率为40~240MHz的带通滤波器。这种滤波器不仅可以抑制掉中频干扰,而且还可以抑制掉高频道的镜象干扰。

在设计滤波器时,必须考虑通带内的阻抗匹配问题,因为天线馈线的特性阻抗为75欧,所以,滤波器的输入阻抗也应为75欧;又因为输入回路的输入阻抗为75欧,所以,滤波器的输出阻抗也应为75欧,这样滤波器的传输效率才最大。其次,通带的幅频特性要好,以减小相移失真。要求阻带要有足够的衰减量,一般为40dB。有关滤波器的知识就介绍这些,详细内容请参阅有关滤波器设计方面的书籍。

2.输入回路:

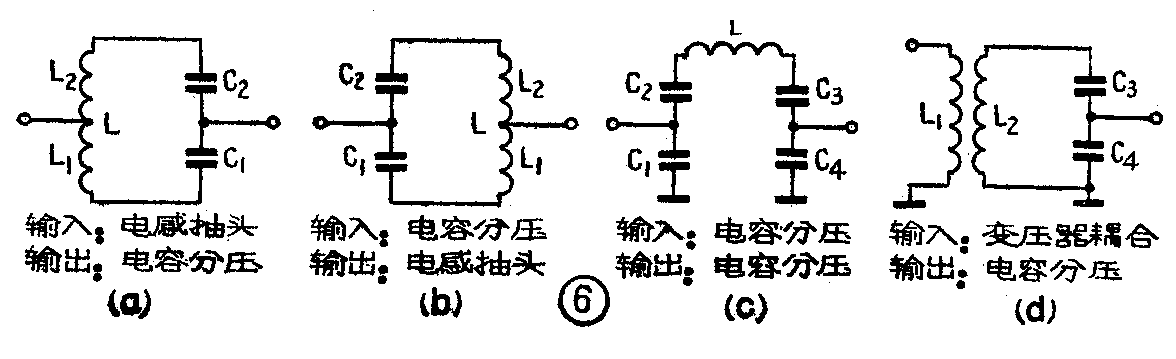

输入回路主要起阻抗匹配和进一步选择并传输信号的作用。输入回路主要有以下几种形式,如图6所示。图6(a)为输入端电感抽头,输出端电容分压的形式。它的优点是可以通过改变线圈的抽头(即匝数比),达到良好的阻抗匹配。但是,通频带随频率的变化而变化,一般高频道的频带很宽,选择性较差。因此,当电路要求阻抗匹配比要求选择性更为重要时,采用这种电路比较适合。联合设计高频头就是采用这种输入回路。图6(b)为输入端电容分压,输出端电感抽头的形式,通过改变线圈抽头的位置,可使输入回路在高、低频道时,均与晶体管达到良好的阻抗匹配,这样可保持一定的带宽,并减小加中和时带来的增益差。另外,C\(_{1}\)可以选得很大,使本振辐射干扰旁路到地,起到减小本振辐射的作用。缺点是晶体管的输入电容随AGC电压变化时,频率偏移较大,使幅频特性曲线变坏。由于输入端为电容分压,所以行波系数较差。图6(c)是输入、输出端都是电容分压的情形,这种电路的优点是机械接点少,调整简单,C1也可以选得很大,可减小本振辐射干扰。缺点是行波系数的一致性差,改变频道时,带宽也随着改变。图6(d)输入端为变压器耦合形式,输出端为电容分压,其原理和图(a)相似,但是由于阻抗匹配不如图(a)好,所以用得较少。

在设计输入回路时,要重点考虑阻抗匹配和减小插入损耗的问题。所谓阻抗匹配,就是要求输入回路的输入阻抗和天线阻抗(馈线特性阻抗)匹配,另一端(输出阻抗)和晶体管的输入阻抗匹配,这样传输效率才能高。图1第②虚线框中的L\(_{5}\)为接入电感,L5与L\(_{6}\)之和为回路谐振电感。为了与天线馈线实现更好的阻抗匹配,1~12频道采用不同数值的线圈,并通过改变线圈的匝数比,使天线和回路达到阻抗匹配。为了与晶体管输入端实现更好的阻抗匹配,高、低频段采用不同的分压电容,C4、C\(_{6}\)为1~5频道的分压电容;C5、C\(_{6}\)为6~12频道的分压电容。如果输入回路与天线阻抗不匹配,有一部分能量要被输入回路反射回去,被接收机二次接收。由于二次波的相位和一次波的相位不同,结果在屏幕上产生重影(鬼影)。通常用反射系数来衡量反射的大小,反射系数ρ=RA-R\(_{in}\)RA+R\(_{in}\)(式中RA为天线阻抗,R\(_{in}\)为输入回路的输入阻抗),当RA=R\(_{in}\)(匹配),ρ=0,能量全部进入输入回路;当RA≠R\(_{in}\)(不匹配),ρ≠0,就有一部分能量反射回天线。一般用行波系数S=1-|ρ|;1+|ρ|来说明匹配的好坏,当ρ=0时,S=1,能量传输最大;当|ρ|=1时,S=0,能量全部反射回去。设计时,要求S≥0.25。S=0.25时,对75欧的天线来说,相当于输入回路的输入阻抗为300欧,或者18.75欧,这时,传给输入回路的功率只有匹配时的二分之一,可见,匹配越好,能量传输就越大。

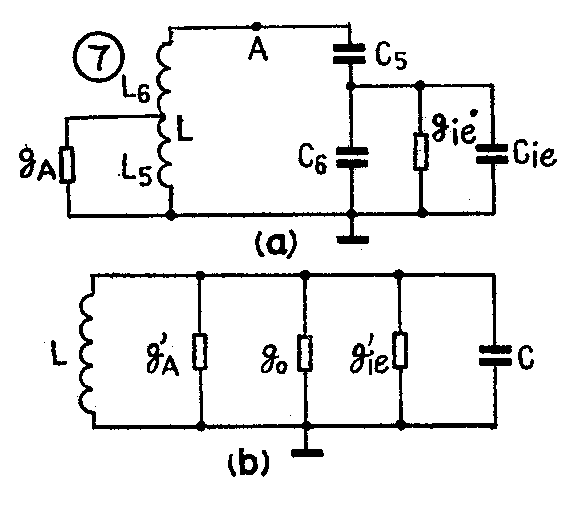

我们将图1的输入电路画成图7(a),所示的等效电路,来进一步分析实现阻抗匹配的条件。其中,g\(_{A}\)为天线电导(天线阻抗的倒数);gie为晶体管输入电导(输入电阻的倒数);C\(_{ie}\)为晶体管的输入电容。将gA折算到A、地间,则

g\(_{A}\)'=(N1N)\(^{2}\)g\(_{A}\)=n12g\(_{A}\)

式中n\(_{1}\)=N1N=L\(_{5}\);L5+L\(_{6}\)为接入匝数比。将gie也折算到A、地间,则g\(_{ie}\)'=C6(C\(_{5}\)+Cie+C\(_{6}\))\(^{2}\)gie=n\(_{2}\)2gie,式中n\(_{2}\)为电容分压比。这样图7(a)可进一步等效成图7(b),其中C=C6(C\(_{5}\)+Cie)/(C\(_{5}\)+C6+C\(_{ie}\)),实现阻抗匹配的条件是:gA'=g\(_{o}\)+gie'(g\(_{o}\)为回路固有并联阻尼电导)。由于go《g\(_{A}\)',go《g\(_{ie}\)',所以,gA'≈g'\(_{ie}\),即n1\(^{2}\)g\(_{A}\)=n22g\(_{ie}\)。用阻抗来表示,即有n1\(^{2}\)/R\(_{A}\)=n22/R\(_{ie}\)。从上式可以看出,通过改变电感线圈的匝数比n1和电容分压比n\(_{2}\),可以使信号源折算到输入回路的阻抗等于晶体管折算到输入回路的阻抗,从而达到阻抗匹配的目的。也就是说,通过改变L5/(L\(_{5}\)+L6)和C\(_{4}\)/C6或C\(_{5}\)/C6,就可使输入 回路在1~12频道内与天线馈线和晶体管达到阻抗匹配。但是由于晶体管的输入阻抗是随着偏置电压和工作频率变化而变化的,所以,输入回路不可能和晶体管做到完全匹配。为了减小晶体管输入电容变化对输入回路的影响,分压电容C\(_{6}\) 可以选大一些,或者在回路里适当并联上一个小电容。

所谓插入损耗,主要是指插入输入回路后,所造成的能量损失。如果只考虑回路本身的损失(不考虑不匹配造成的损失),则传输效率η=(1-Q\(_{L}\)/Q0)\(^{2}\)≈1-2Q\(_{L}\)/Q0,式中Q\(_{0}\)=ω0Lr为回路的空载品质因数,QL=ωCR为有载品质因数。而插入损耗A=10lgη。可见,要使功率传输效率η大,要求Q\(_{0}\)越大越好,QL越小越好。要使Q\(_{0}\)大,必须减小线圈本身的损耗电阻r;要使QL小,必须减小回路的总阻尼电阻R。由于晶体管的输入电阻R\(_{ie}\)是固定的,所以 ,要减小R, 一般采用增加接入线圈匝数的方法来减小N/N1。另外,要选用损耗电阻小的导线绕制线圈,以便增大Q\(_{0}\)值。但是,QL降低后,通频带要变宽,使选择性变差。对于输入回路来说,主要是提高能量传输效率,减小插入损耗,不使信噪比变坏,所以,一般要求插入损耗A≤0.5dB。

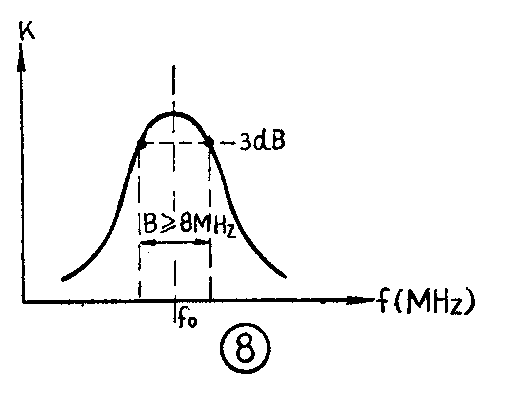

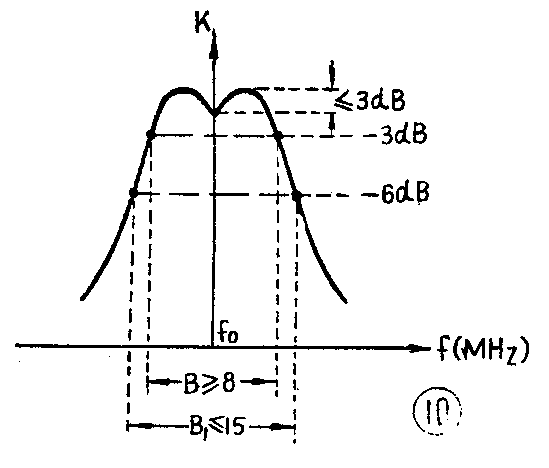

从上面分析可知,输入回路的通频带与插入损耗有关,通频带太窄,会增加插入损耗,通频带太宽,选择性变差,一般要求带宽B≥8MHz,图8为输入回路的幅频特性。

3.高放电路:

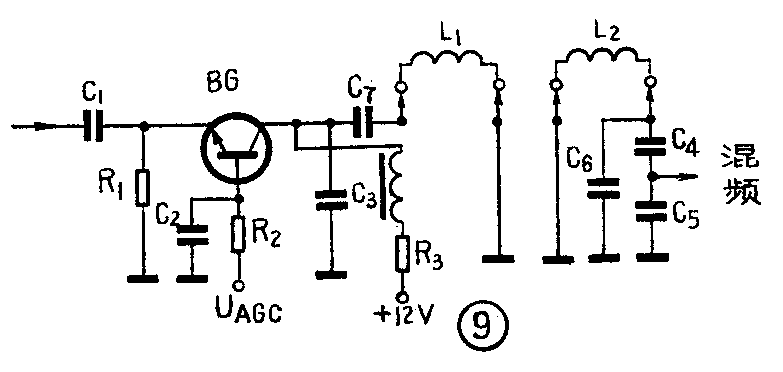

高放电路的主要作用是选择并放大全电视信号。高放电路主要有以下两种形式:图1第③虚线框为共发射极电路,这种电路的优点是:交流放大系数β\(_{fe}\)较大,增益较高(尤其在低频段);输入阻抗较高,便于和输入回路匹配。缺点是:内反馈电容Cob较大(为负反馈),使增益有所下降,同时也影响工作的稳定性,但是比较容易中和;另外,增益随着频率升高而下降,高、低频道的增益差较大;输入阻抗随频率和电流的变化而变化,容易影响幅频特性。图9为共基极电路,其优点是内反馈电容C\(_{oe}\)很小,所以,不加中和电容也能稳定工作。由于交流放大系数βfb较小,其增益取决于输出、输入阻抗之比,所以,在1~12频道内增益比较均匀,增益差较小。虽然C\(_{oe}\)较小,但为正反馈,如果设计不当也会引起自激。由于输入阻抗小,所以与输入回路匹配较困难,加上增益低,这种电路一般用得较少。

为了降低噪声、提高增益、提高承受大信号的能力和抗交扰调制的能力并增大AGC的作用范围,目前国外已采用双栅场效应管作高放管。

从级间回路来看,又分为单回路和双回路两种形式。单回路的特性曲线呈单峰,其优点是线路简单,相移失真小。但这种电路通频带窄、选择性差。双回路有电感耦合(紧耦合),和电容耦合两种,特性曲线呈双峰。这种电路的通频带可以做得很宽,选择性也好。但是因为幅频特性有凹陷存在,所以相移失真较大,插入损耗也较大。电感耦合靠改变初、次级线圈的互感和自感量来调整幅频特性,能获得较好的矩形系数,但调试较困难。电容耦合只要改变微调电容的数值,即可调整幅频特性,因此,调试较简单。

在设计高放电路时,主要考虑以下几个问题:

<1>噪声系数。大家知道,多级放大器的噪声系数NF\(_{∑}\)=NF1+\(\frac{NF}{_{2}}\)-1Kp1+NF\(_{3}\)-1);Kp1·K\(_{p2}\)+……+NFn-1K\(_{p1}\)·Kp2……K\(_{pn}\)-1,由于各级放大倍数都较大,所以NF∑≈NF\(_{1}\)+NF2-1;K\(_{p1}\)。可见,整机的噪声系数主要取决于高频头,高频头又主要取决于高放电路。因此,设计高放电路时,要选用噪声系数小的管子,一般要求NF≤4dB。

<2>增益要求。为了把微弱的全电视信号加以放大,提高整机的灵敏度,高放电路必须满足一定的增益要求。根据整机增益分配的要求,高放功率增益要大于18dB。从噪声系数的公式来看,第一级增益越大,整机噪声系数也越小。高放电路的增益不仅要满足要求,而且对强信号要求能够自动控制。因此,高放管必须具有AGC特性。一般采用正向AGC,因为正向AGC动态范围大(对管子而言)、承受大信号的能力和抗交扰调制的能力都较好。所谓交扰调制是由于高放管be结的非线性造成的,当强干扰信号来到时,会对有用信号进行调制,从而干扰了图象。所以要选用be结非线性较小的管子。

高放管的工作状态,一般选择在高放管AGC起控点的电流值上,此时高放管的增益最大。对于3DG80B和2G210来说,起控点电流为3毫安。由于国产正向AGC管高频道起控电流小于低频道起控电流(相差零点几毫安),所以,为使高、低频道都能处于起控状态,一般调试在低频道起控点上。

<3>选择性。在设计和选择高放电路时,要求满足一定的通频带宽度,并尽可能使矩形系数好,这样才能保证良好的选择性。通常要求高放级的幅频特性要平坦,双峰凹陷不能大于-3dB;在相对增益为-3dB处,要求带宽大于8MHz;在相对增益为-6dB处,要求带宽要小于15MHz。这样图象载频信号和伴音载频信号才都能得到充分放大。图10为典型的高放幅频特性曲线。

联合设计高频头的高放电路是采用双回路共发射极电路,其电路如图1第③虚线框所示。R\(_{1}\)为AGC偏置电阻,该电阻不能太小,以免降低晶体管的输入阻抗,一般选数千欧;C7为滤波电容,防止高频干扰通过电源进入晶体管;R\(_{2}\)为发射极直流负反馈电阻,用以稳定直流工作点,它和C8组成交流滤波电路,时间常数RC》1/f\(_{0}\);C12是中和电容,C\(_{11}\)是提供中和电压的相位电容,使流过C12的电流和内反馈电流相抵消。在6~12频道时,L\(_{7}\)与C9、C\(_{11}\)及高放管的输出电容组成初级回路,L8与C\(_{13}\)、C14、C\(_{15}\)、C16及混频管的输入电容组成次级回路。在1~5频道时,C\(_{1}\)0与C9并联后接入初级回路,使回路电容增大,高频段采用较小的接入电容,可使初级线圈L\(_{7}\)的圈数增加,以便提高高频段的电压增益。次级回路的接入电容也是随频段的改变而改变的,高频段接入C15,低频段C\(_{14}\)、C15并联后再接入,通过改变接入电容与C\(_{18}\)的比值,从而使次级回路与混频管达到阻抗匹配。C16一般选得较大,以减小混频管输入电容的影响。R\(_{5}\)是初级回路阻尼电阻,用以降低回路Q值减小高低频道增益差,使幅频特性平坦,减小相移失真。R3是工作点调整电阻,由于各晶体管的AGC起控点电流不一致,通过改变R\(_{3}\),来改变Ic的大小,从而保证基极偏置电压总在3伏时起控。若I\(_{c}\)>Ic起控,使高放管增益下降,降低了信噪比;若I\(_{c}\)<Ic起控,则随着U\(_{AGC}\)增加,高放增益不仅不下降,反而上升,结果引起AGC的跳变。R4是电源滤波电阻,它和C\(_{29}\)组成倒L型阻容滤波器。(未完待续)(李舜阳)