PMOS集成电路和HTL集成电路的开门阈值都较高,但为什么有时PMOS集成电路不及HTL集成电路的抗干扰能力强呢?这主要是PMOS电路的输入阻抗高(大于1MΩ),也就是说只要干扰源的幅值大于开门阈值且能提供数μA到数十μA的电流,就能使电路误动作。据我们的大量观察,工业环境中各种设备的起动、制动;继电器、接触器的电弧;电焊机的火花;可控硅设备等产生的大量电磁干扰都在几伏到几十伏以上。因此PMOS电路在复杂的工业环境中要可靠地运行,必须加装抗干扰措施。目前有许多抗干扰措施都是行之有效的,但是较多的从抑制干扰源角度着手。实践证明,工业环境中干扰源是多种多样的,从干扰源出发采取防干扰措施有防不胜防之感。所以我们必须抓住事物的主要矛盾,采取措施增强线路自身的抗干扰能力。从我们的实践得知,最易受干扰的是触发器,特别是由它组成的计数电路。在数控设备中,一有干扰,计数器就首先“乱跳”,双稳态触发器就翻掉,影响最大。因此我们在计数电路的CP(时钟脉冲)端,单、双稳态电路的触发端,门电路的输入端等处采取措施,设法加一RC积分电路滤去各种干扰波。我们就是用这种办法,使PMOS数控设备在工业环境中能可靠运行。

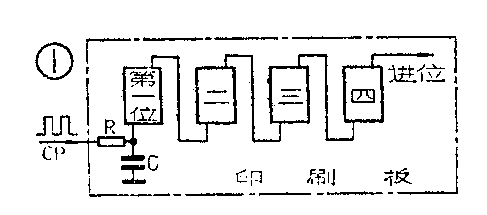

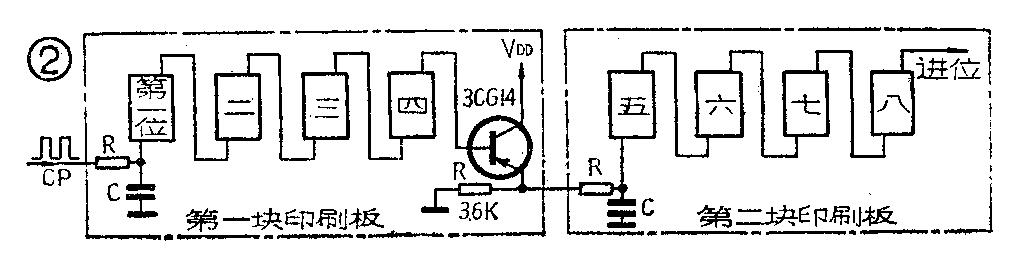

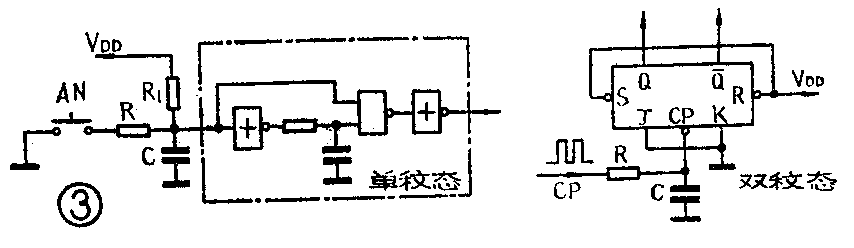

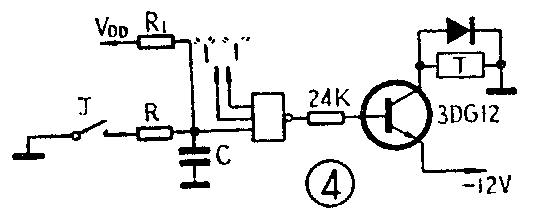

RC积分电路怎么加?加多大?我们认为:如果设备上有多个触发器组成的电路如计数器、分频器、程序脉冲发生器、移位寄存器……等单元的第一位触发器的CP输入端必须加RC积分抗干扰电路如图1,并且RC的装配位置一定要尽量靠近CP输入端处。假如触发器位数较多,一块印刷板放不下,需要进位到第二块印刷板时,则第二块板的CP输入端也应加RC,这时特别要注意,为了减轻PMOS电路输出负载,第一块板的输出端应加一射极跟随器如图2。但对在同一块印刷板内相互连接的各触发器可以不加RC。对与印刷板外有连线的单、双稳态电路也应加RC如图3。对于各种门电路一般可以不加,只有发现门电路输入端有干扰或输入端连线较长或连线通过恶劣环境的情况下才加RC,如图4。RC应加多大?如何选择?我们的体会是应结合CP的频率、波形、幅值不同而不同。选大了将阻塞CP信号,使计数器、门电路无法翻转;选小了达不到抗干扰的目的。因此RC的时间常数(τ=R·C)选择原则是:让最高工作CP频率能可靠通过的前提下尽量加大τ。对PMOS电路来讲,因为输入阻抗高,故可用大R小C。R一般在510Ω~51KΩ,C在1000P~0.1μf范围内组合选用,可用1K和0.01μf作起点调试值。

我们认为应在实践中细心观察干扰的“登陆点”,不要盲目乱加RC电路,一般一台数控设备加几组就能稳定运行。

这种方式也适用于由晶体管或其他集成电路组成的设备,不同之点是由于其他电路输入阻抗低,应该采用大C小R。一般R在数百欧~数十欧,甚至不加。C在1000P~1μf范围之间选用。

注意:这种抗干扰方式只适用在速度不太高的数控或自动化设备上。还必须注意PMOS电路的所有输入端不得悬空,否则系统将受干扰无法稳定运行。对不用的输入端应按线路要求接“1”或“0”电平。对已接有线条的输入端也要检查在运行过程中是否会有悬空机会,如图3单稳态输入端接的是按钮,当按钮不按下时输入端悬空,所以必须加电阻R\(_{1}\)接电源VDD,图4亦然,一般防输入端悬空电阻R\(_{1}\)在510K~1MΩ范围中选取。(上海医用电子仪器厂 沈琦)