集成电路触发器一般是指两个输出端总保持相反状态的双稳态触发器。它是一种能够存贮和传递数据信息的逻辑电路。象计数器、移位寄存器等都用触发器来组成;存贮器、数字比较器等也用触发器做基本存贮元件。

本篇向大家介绍几种典型集成电路触发器的工作原理和演变关系。

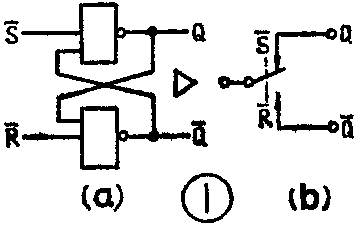

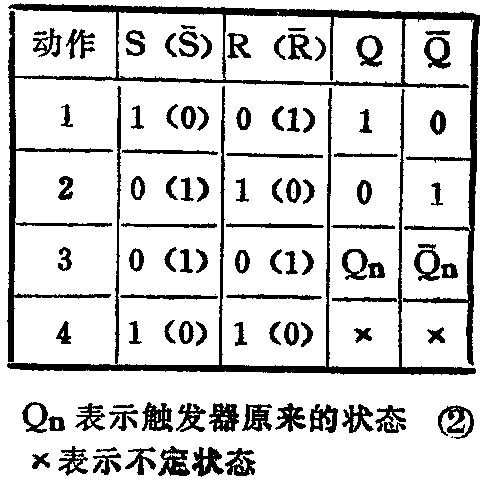

基本RS触发器

基本RS触发器(也叫RS存贮触发器)由两个具有倒相功能的逻辑门(如与非门)的输出端和输入端互相交叉耦合构成(图1a)。它有两个能够维持相反逻辑状态的输出端,一个叫做Q端,另一个叫做Q-端。当Q=1、Q-=0时,我们称触发器处于1(置位)状态;反之则称它处于0(复位)状态。因此相应的输入端分别叫做置位(S)端和复位(R)端。我们取S和R的共轭量S-和R-作为基本RS触发器的输入端。根据与非门的逻辑功能,当S-=0即S=1时,可得Q=1;当R-=0即R=1时,可得Q-=1。这样,当S=1时,触发器处于置位状态,而当R=1时,触发器处于复位状态,与习惯规定相符。基本RS触发器很像一个单刀双掷开关(图1b),倘若开关的触点被转换到一个确定位置,则电路就会具有相应确定的置位或复位状态。

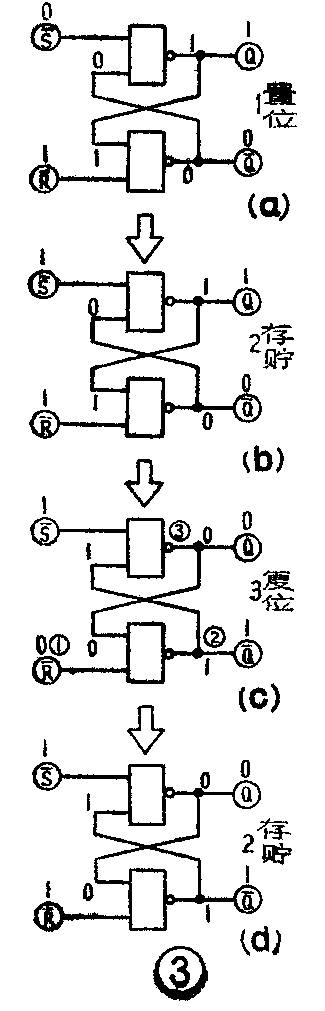

基本RS触发器的动作过程如国3所示。假如S-=0,R-=1,则Q=1、Q-=0,实现置位动作(图3a)。假如S-=0变为S-=1,即S-=R-=1,则Q和Q-维持原状态不变,实现存贮动作(图3b)。再如R-=1变为R-=0则Q=0、Q-=1,实现复位动作(图3c)。图上用圈起来的数字标出了触发器由存贮状态转入复位状态时各门的动作顺序。

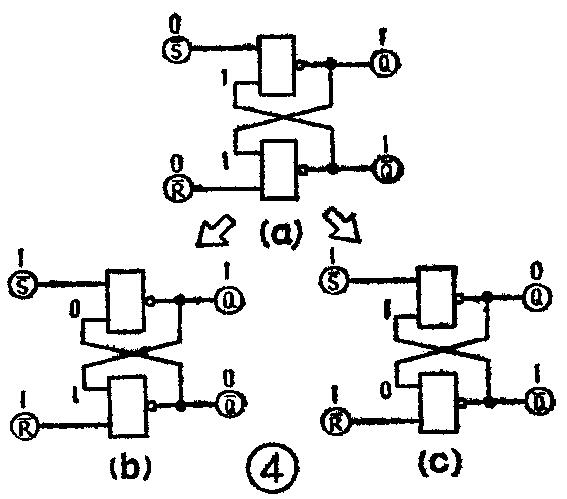

基本RS触发器两个门的输入都为0的状态是被禁止的。这可以由图4来说明。假如S-=0、R-=0,则Q=1、Q-=1(图4a),破坏了Q和Q-互相否定的条件,因此不能用来表示二进制数据(0或1)。而当图4a状态的触发器转入存贮状态S-=R-=1时,则如图4b和4c所示,触发器既可能处于置位也可能处于复位状态,因此输出是不确定的,无法实现触发器的存贮动作。所以说,基本RS触发器只允许具有如图2真值表中所列出的1(置位),2(复位),3(存贮)三种工作状态。表中第四种状态是被禁止的,因为有不确定输出。

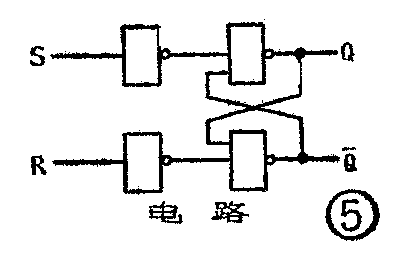

RS复位置位触发器

在实标应用中,必须严格控制各触发器的翻转时间,使它们按照一定的先后顺序(称为节拍)工作。这种控制作用是通过加在触发器的时钟脉冲(简称CP)来实现的。

在基本RS触发器中,输入信号直接加到两个交叉耦合的逻辑门,所以无法加时钟脉冲让这种电路按规定节拍工作,因此往往不能满足实际需要。

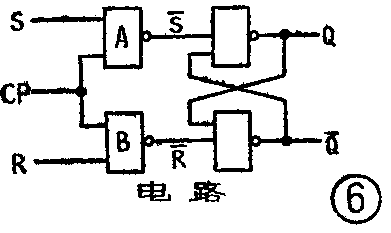

我们可以在基本RS触发器的左面再加两个与非门作导引门,构成最简单的非同步式RS复位置位触发器(图5)。虽然它也仅有置复位功能,但只要把两个导引门的输入端联接起来就能方便地加时钟脉冲使其按规定节拍工作。这就是同步式RS触发器(图6)。它有S、R两个数据输入端和一个CP时钟脉冲输入端。

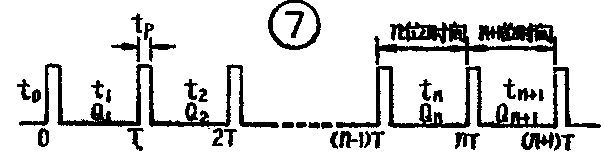

时钟脉冲CP的波形如图7所示。因为在两个时钟脉冲的时间间隔里CP=0,所以无论S、R端处于什么状态,两个与非门A、B(见图6)的输出都保持为1,基本RS触发器的状态不发生变化,此时称RS触发器处于被封锁状态。只有当CP到来时,才可能改变触发器的状态。各时钟脉冲间的时间间隔t\(_{0}\)、t1、t\(_{2}\)……tn、t\(_{n+1}\)叫做二进制数位时间,简称位(比特)时间。若用Qn表示触发器在第n位时间t\(_{n}\)内的状态,则它在tn+1位时间内的状态可用Q\(_{n+1}\)来表示。

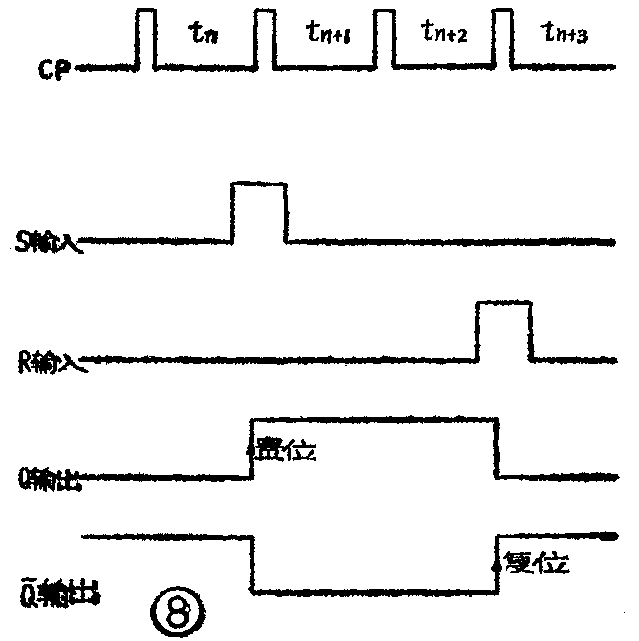

图8是在不考虑时延的理想情况下同步式RS触发器输入输出波形的时间图。当CP=1(有时钟脉冲出现)时,若在t\(_{n}\)位时间内触发器的状态为0(Qn=0,Q-\(_{n}\)=1),输入数据为Sn=1,R\(_{n}\)=0,则tn+1位时间内触发器的状态变为1(Q\(_{n+1}\)=1,Q-n+1=0)。如果此后S、R又向相反的方向变化,S\(_{n+2}\)=0,Rn+2=1,则当CP=1时触发器又回到0状态。数据信号S、R只在有时钟脉冲的情况下才起作用,所以把这类电路叫做同步式触发器,而把不具备同步功能的电路(图5)叫做非同步式触发器。

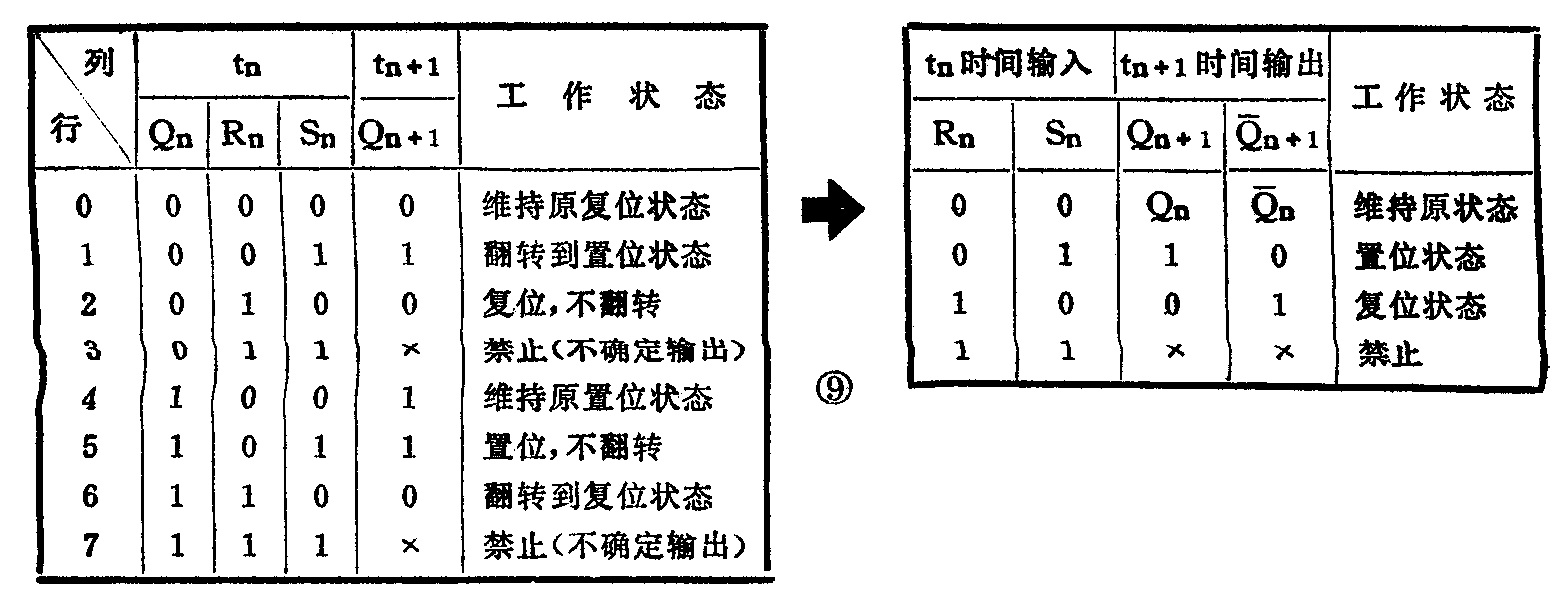

RS触发器的逻辑功能也可以用图9的真值表来描述。其中共列出两组逻辑量。一组是前一位时间t\(_{n}\)内的输入量Rn和S\(_{n}\)与输出量Qn,反映第n+1时钟脉冲出现之前电路的各种可能状态;另一组是输出量Q\(_{n+1}\),反映第n+1时钟脉冲到来时在上述输入量作用下第n+1位时间tn+1内触发器的状态。由真值表可见,应当禁止S\(_{n}\)=Rn=1(第3,第7行),避免引起不确定输出。

优先置位(S)和优先复位(R)触发器

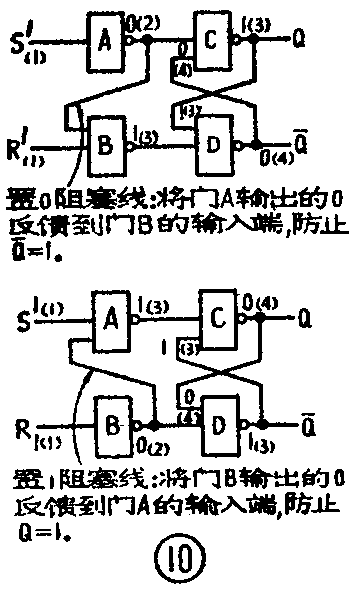

RS触发器的缺点是当S=R=1时出现输出不确定状态。怎样才能既消除这种现象而又能有两组独立逻辑功能的输入端可供使用呢?仔细分析一下可以发现,RS触发器的不确定输出是由于S=R=1时右边基本RS触发器的两个输入端都可能出现0状态引起的。于是想到:若能避免上述情况发生,不定输出的问题不就解决了吗?根据这个设想,组成了如图10所示的两个非同步式触发器。一个采用了当S=R=1时能使基本RS触发器实现优先置1的反馈线,称为置0阻塞线,构成优先置位(S)触发器;另一个采用了能实现优先置0的反馈线,称为置1阻塞线,构成优先复位(R)触发器。在这两根反馈线的分别作用下,基本RS触发器的两个输入端总处于相反的逻辑状态(其动作顺序用数字标在图10中各括号内),因此不会产生不确定输出。

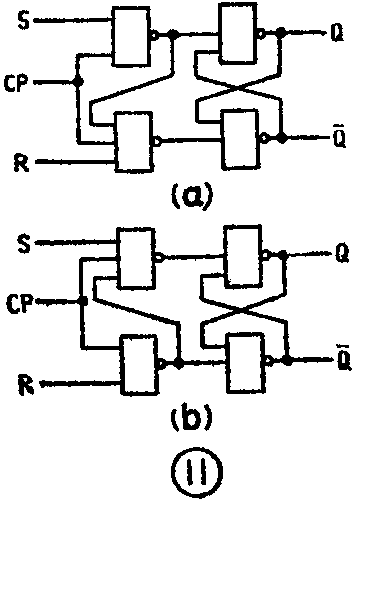

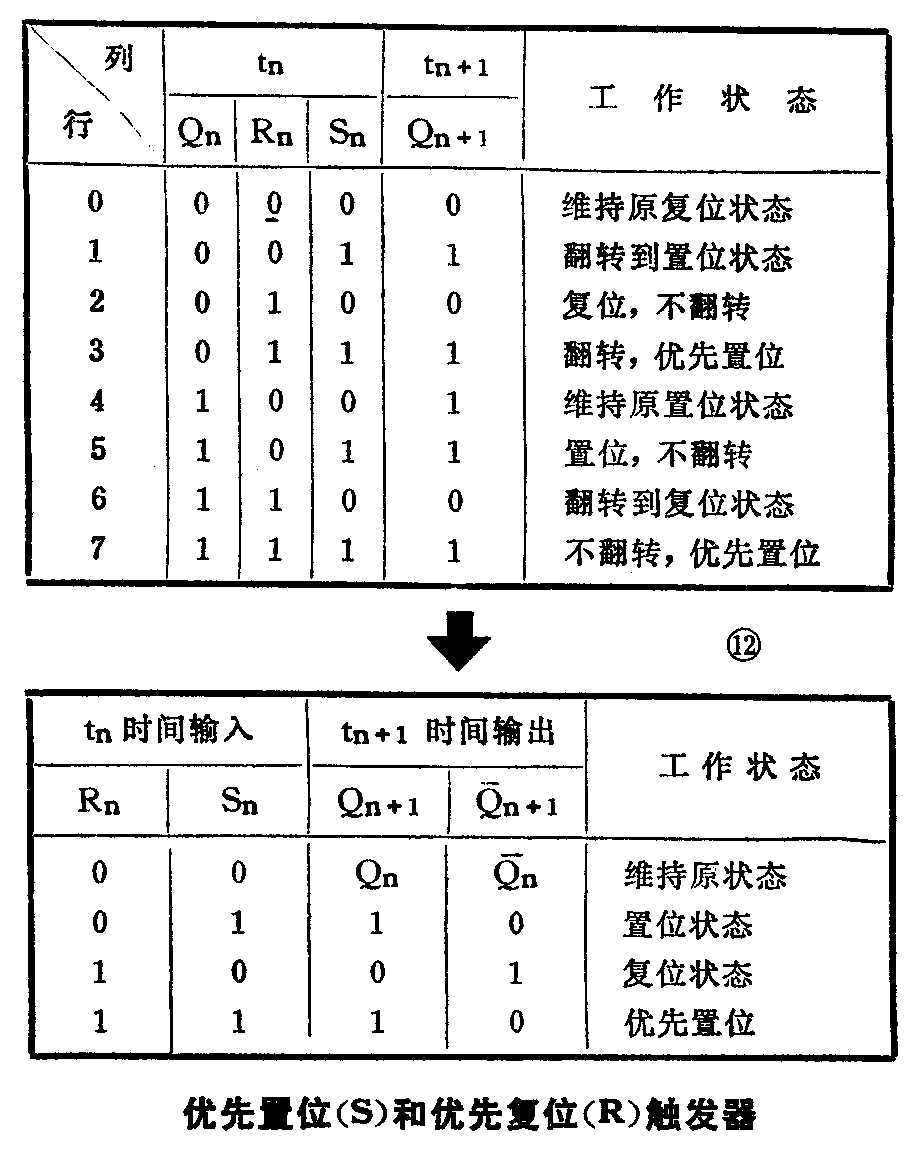

图11a和11b分别示出了同步式S和R触发器。图12为S触发器对应于8种输入输出状态组合的真值表。它说明这类触发器的逻辑功能与RS触发器的基本相同,而由于允许S=R=1,因此功能较为完善。

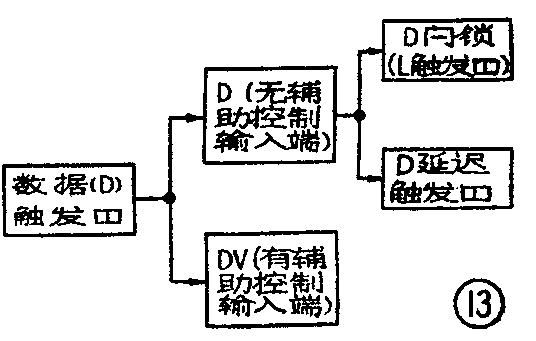

数据(D和DV)触发器

数据触发器主要用于存贮和传递以逻辑量形式表达的各种数据。它广泛应用于各种数据存贮器、计数器、移位寄存器等逻辑部件电路中。数据触发器的分类见图13。这类电路只具备一组用来传送数据的输入端,称为D端,故简称为D触发器。如果再增设一个辅助控制输入端V,便形成了DV触发器。它与一般的单端D触发器没有本质区别,因此把它们归为一类。下面介绍各类D触发器。

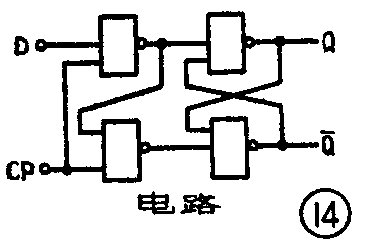

D闩锁(也叫做L)触发器是最简单的一种。图14示出了一个同步式D闩锁。对照图11的电路不难发现,D闩锁是将S触发器中的R输入端去掉,只留下S端输入数据并改称D端构成。其中,若D\(_{n}\)=1,则由于置0阻塞线的作用,能强制基本RS触发器的两个输入端处于相反的状态,使Qn+1=1、Q-\(_{n+1}\)=0;而若Dn=0,则由于置0阻塞线和基本RS触发器反馈线的作用又能使Q\(_{n+1}\)=0、Q-n+1=1。两种情况下都有Q\(_{n+1}\)=Dn。

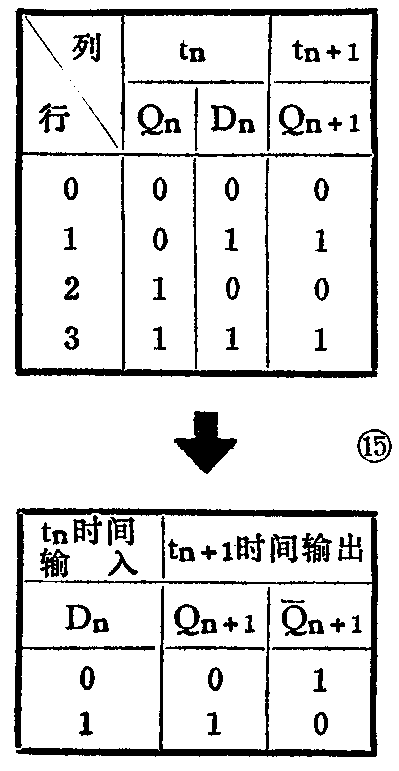

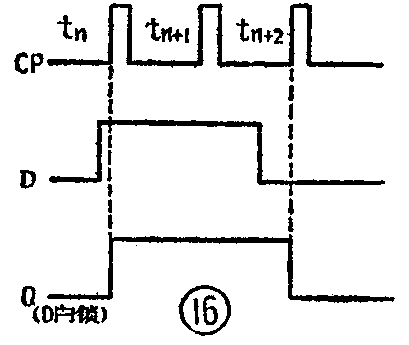

D闩锁的真值表和时间图分别绘于图15和图16。由图可见,该电路的输出Q\(_{n+1}\)永远与输入数据Dn相同而与电路的原状态无关。实际上由于任何逻辑门都对输入信号产生时延,所以Q总要迟后于D。但因为在D闩锁中这段延迟时间最大不超过一位时间,所以表示为Q\(_{n}\)+1=Dn。总之,D闩锁是一种能把某一时刻的数据暂时地,照原样保持下来的电路。

另一种电路叫做D延迟触发器,这种触发器应用甚广,其实际电路我们将在另文介绍。

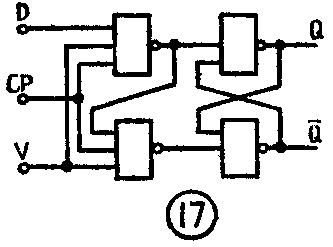

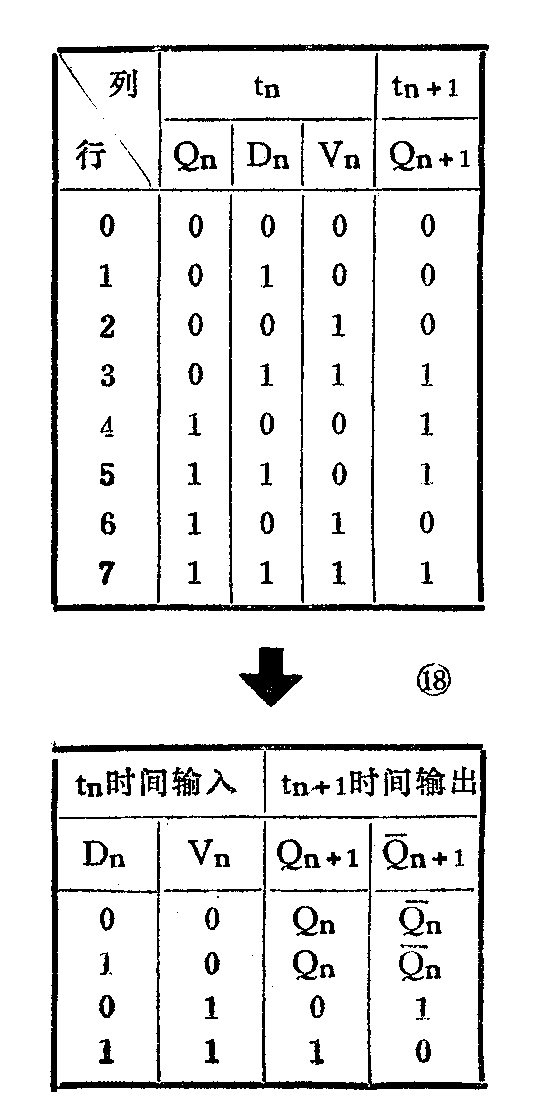

再看DV触发器。以图17所示的同步式DV闩锁为例,当V=0时两个导引门被封锁,无论D如何变化,输出都保持原状态不变。而当V=l时电路按D闩锁的方式工作。这种电路的真值表示于图18,由表可见,V端只对输入数据起选通作用而不具备独立的逻辑功能,因此我们仍把DV触发器归入具有一组独立逻辑功能输入端的一类。

双输入端JK和E触发器

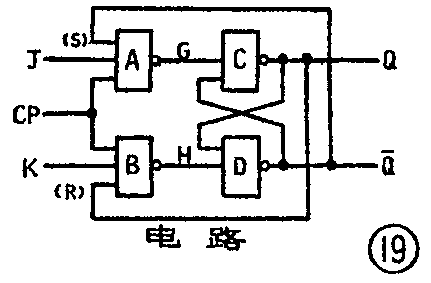

JK触发器和E触发器都具有两组逻辑功能独立的输入端,并且能避免不定状态发生。图19示出了JK触发器的原理。它是由基本RS触发器的输出端Q和Q-引出两根反馈线分别接到R端和S端并另外设置两个数据输入端J和K构成的。Q和Q-能使门A、门B的输出G和H总处于相反的逻辑状态,从而令末级基本RS触发器的两个输出端总处于相反的状态。

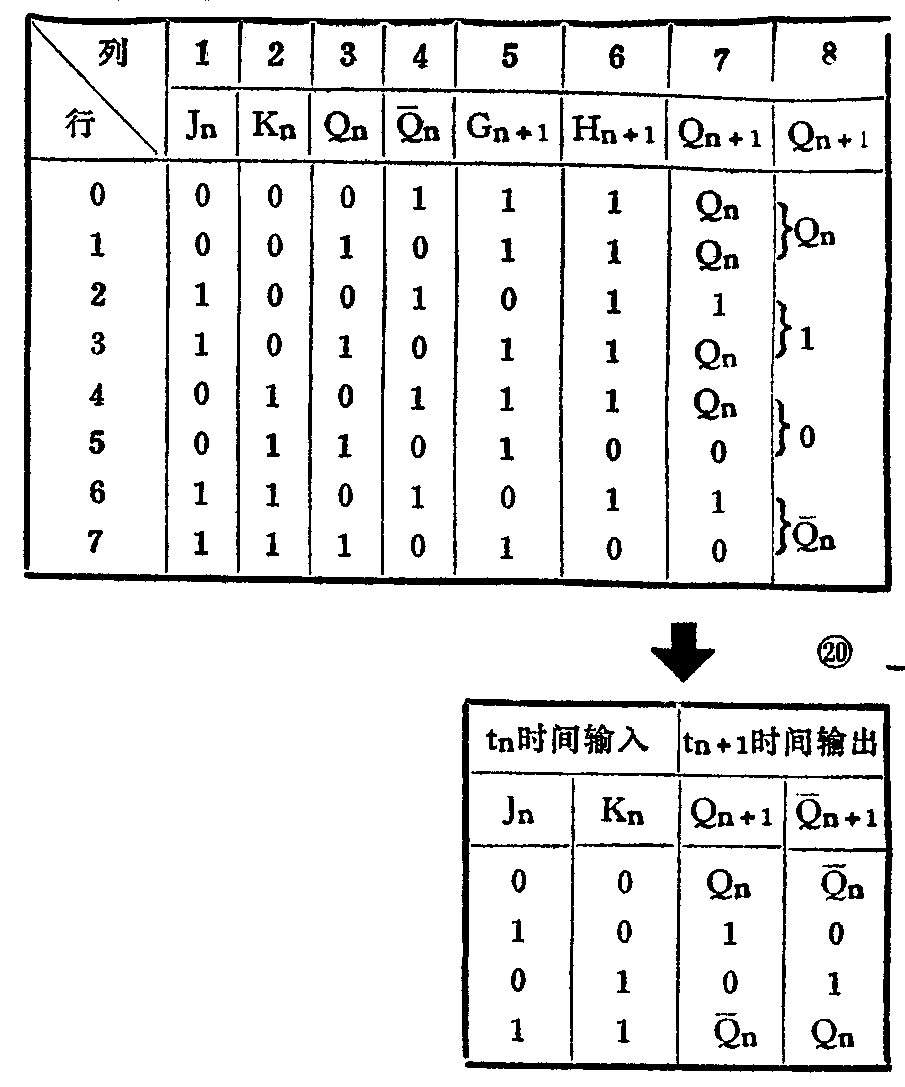

根据与非门的逻辑功能,在不考虑时延的理想条件下,由图19的电路可以从输入量J\(_{n}\)、Kn和输出量Q\(_{n}\)、Q-n的不同组合求出下一位时间内的G\(_{n+1}\)、Hn+1和Q\(_{n+1}\)的不同组合值,从而画出图20所示JK触发器的真值表。再将该表并项,便得到简化的真值表。由表可见,当Jn=1、 K\(_{n}\)=1时,每来一个时钟脉冲都会引起触发器翻转一次而不会出现输出不确定现象。

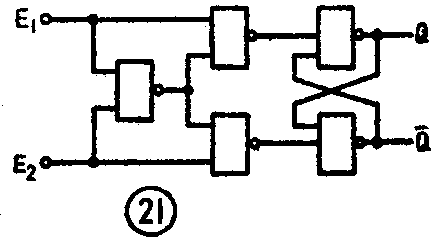

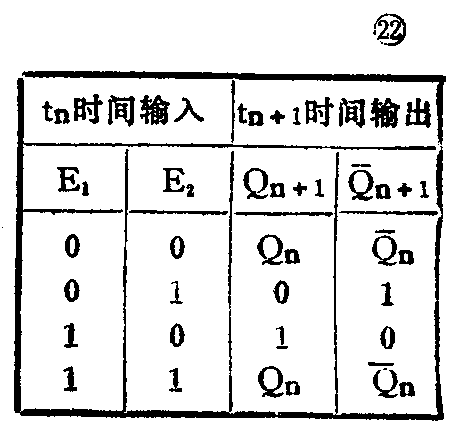

E触发器也是一种允许两个输入端状态同时为1的电路。图21是一个简单的非同步式E触发器。它是在RS复位置位触发器的基础上再增设一个与非门演变出来的。当E\(_{1}\)=E2=1或E\(_{1}\)=E2=0时,右边基本RS触发器的输入都是1,因此输出为Q\(_{n}\)+1=Qn,没有不确定状态。E触发器的真值表示于图22。

计数(T)触发器和具有直接置复位端的计数(RST)触发器

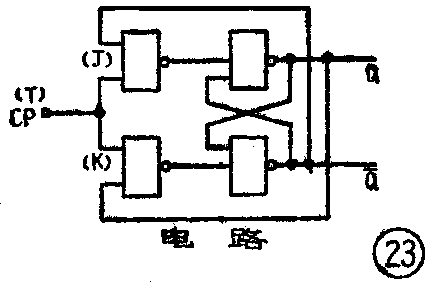

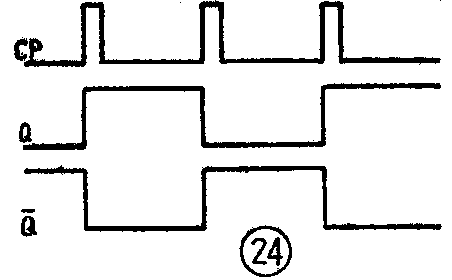

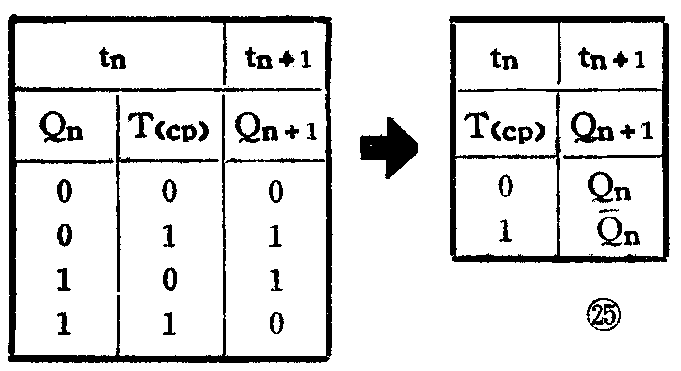

计数(T)触发器(图23)是每出现一个时钟脉冲CP都能自动翻转一次的电路。这和二进制运算中逢二进一的规律是一致的。因此T触发器最适于用来组成计数分频电路。最简单的T触发器是利用JK触发器当J\(_{n}\)=1、Kn=1时Q\(_{n}\)+1=Q-n的特性,将JK输入端联在一起直接用时钟脉冲CP控制得到的。理想T触发器的时间图示于图24,其真值表示于图25。

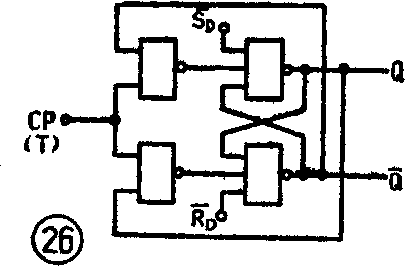

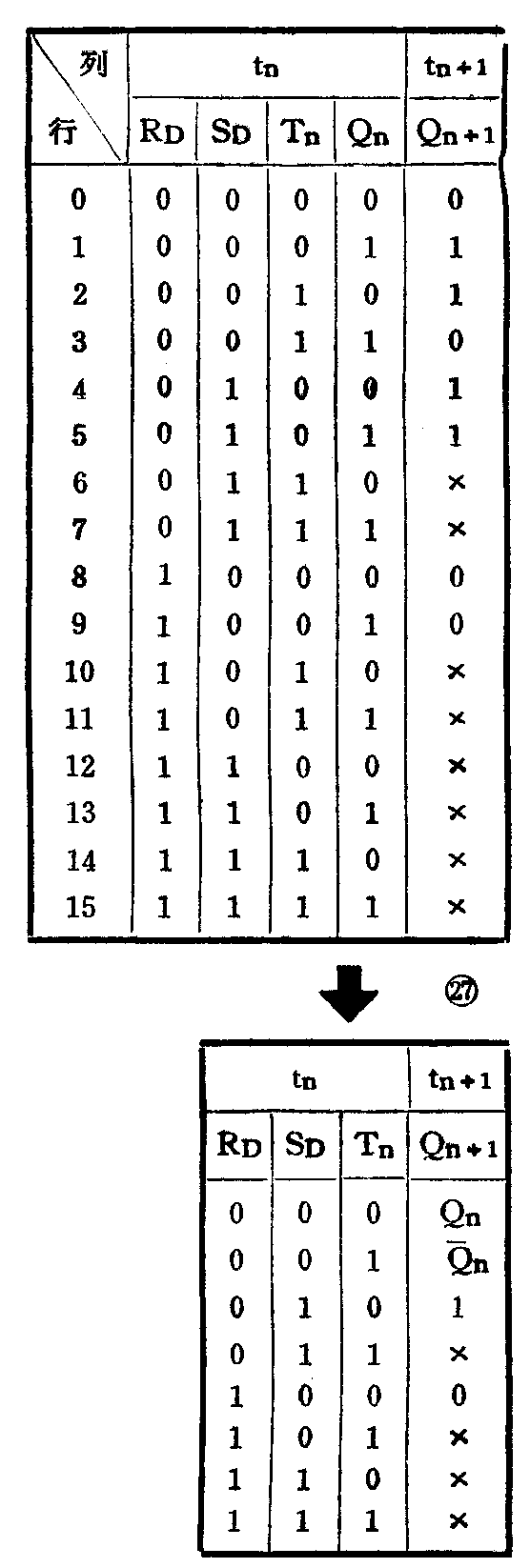

在实践中也广泛采用具有直接置复位输入端S-\(_{D}\)、R-D的计数(RST)触发器(图26)。其中S-\(_{D}\)和R-D的角标D表示“直接”的意思。通过S-\(_{D}\)和R-D端,可以直接将触发器置入所需要的状态。因此,RST触发器兼有RS和T两种触发器的功能。RST触发器的真值表列于图27。

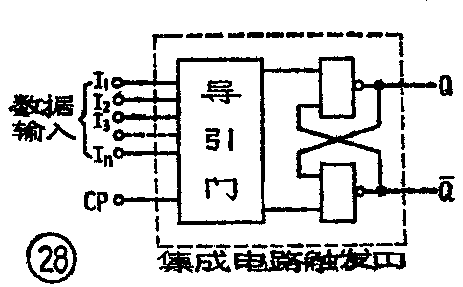

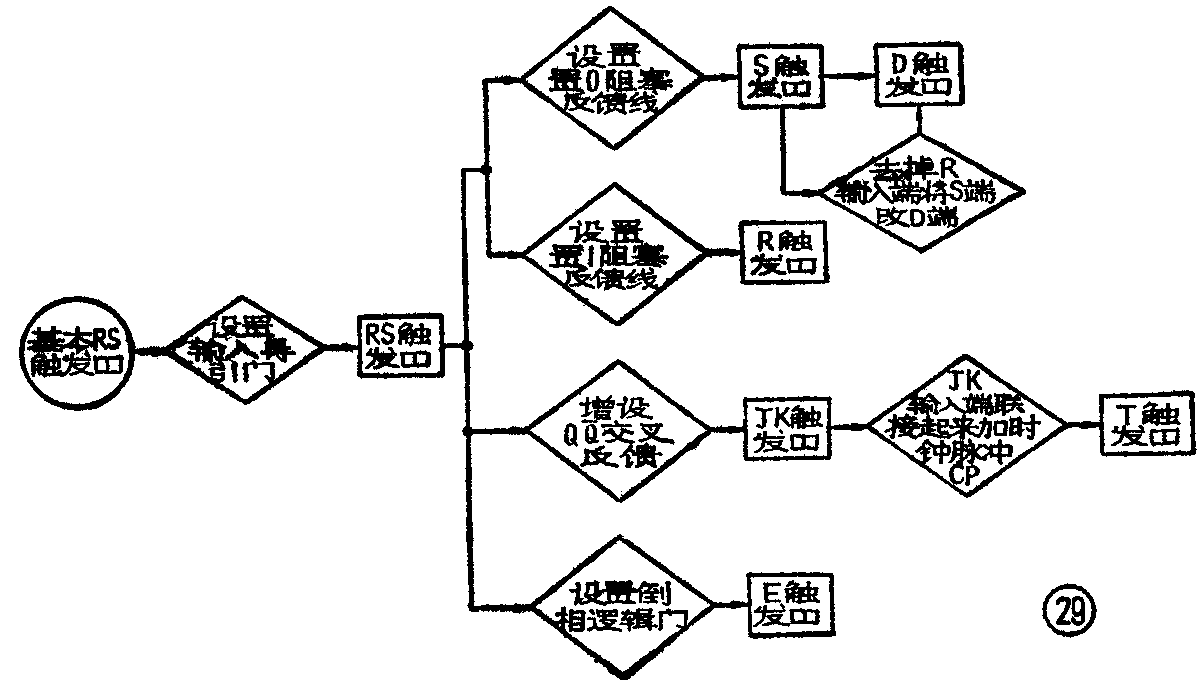

从上面的讨论可以归纳得出如图28所示各种类型触发器的一般结构。可以看出,具有不同功能的各类触发器的区别仅在于导引门的数目及其联接方式不同。它们都具备一个共同的基本性能—存贮功能。因此说,基本RS触发器是任何触发器中不可缺少的组成部分。图29示出了各类触发器结构的演变关系。

最后应当指出,上面讨论触发器的性能时没有考虑时延的影响,而实际上这种理想条件是不存在的。一般说来,当信号变化很快或者电路按规定节拍工作时必须考虑时延的影响,采取有效措施构成实用电路。(颜超)